1

Изобретение относится к .автомати- ке и вычислительной технике и может быть использовано для тестового контроля широкого класса процессорных систем.

Цель изобретения - расширение области применения и повышение коэффициента использования оборудования.

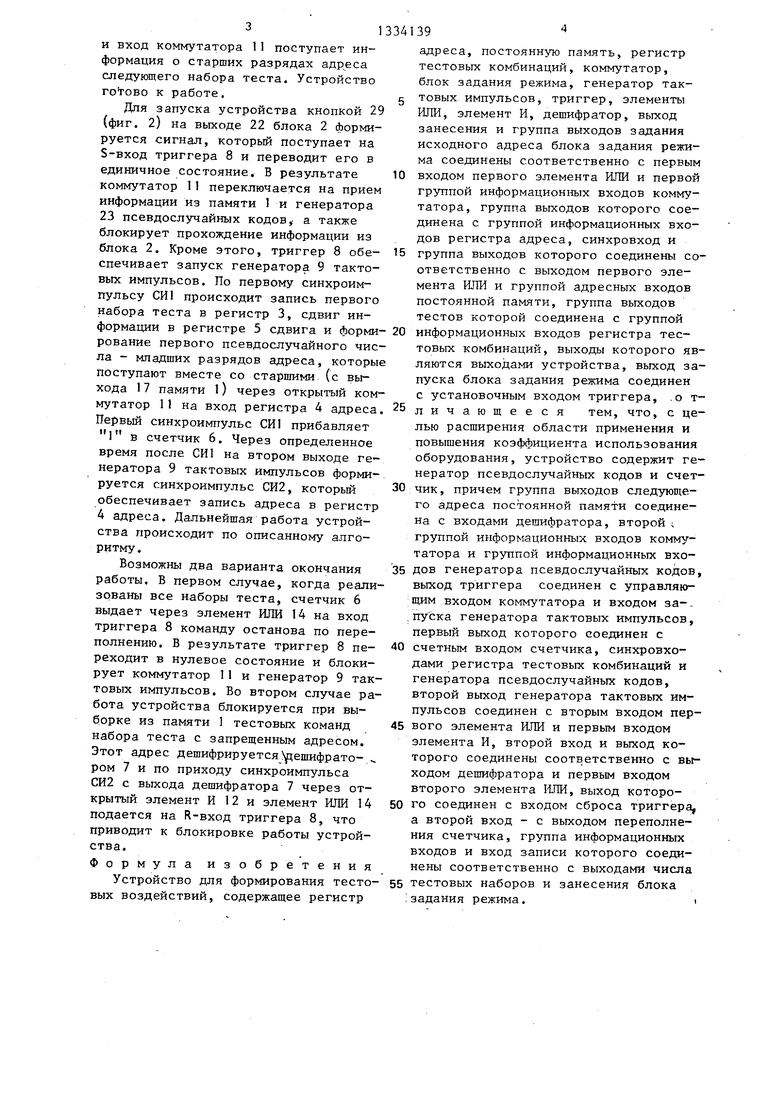

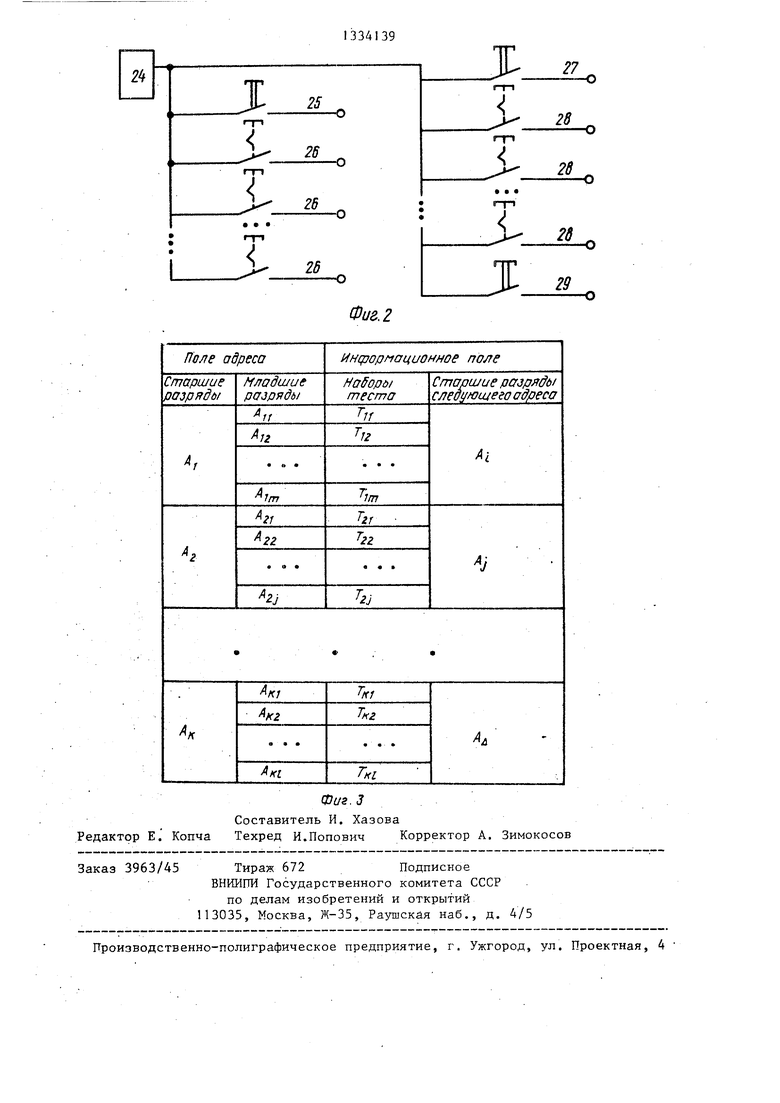

На фиг, 1 изобргнсена функциональ- ная схема предлагаемого устройства; на фиг, 2 - функциональная схема блока задания режима; на фиг. 3 - структура информации, содержащейся в постоянной памяти.

Устройство для формирования тестовых воздействий (фи1 , 1) содержит постоянную память , блок 2 задания режима, регистры тестовых комбинаций 3, адреса 4, сдвига 5, счетчик 6, дешифратор 7, триггер 8, генератор 9 тактовых импульсов, сумматор 10 по модулю два, коммутатор 11, элемент И 12, первый 13 и второй 14 элементы ИЛИ, выход 15 устройства, выходы 16 тестов и 17 следующего адреса памяти 1, выходы 18-.22 блока задания режим и генератор 23 псевдослучайных кодов

Блок задания режима (фиг, 2) содержит генератор 24 едиництэ и кноп ки 25-29.

Память 1 содержит наборы теста, поступаюгцие на контролируемый объект в определенной последовательности. В общем виде содержимое памяти 1 пред- ставлено на фиг„ 3. Старшие разряды адреса определяют группу наборов теста, которые могут быть поданы на объект контроля после воздействия предь дущего теста. При этом выборка одного из наборов теста происходит случайным образом за счет значения младших разрядов адреса, формируемых по случайному закону. Кроме этого, информационное поле содержит старшие разряды следующего адреса, определяющего такую совокупность наборов теста, один (любой) из которых можно подать на контролируемый объект в сле- дзпощем такте. Такой подход к опреде- лению старших разрядов адреса набора теста позволяет исключить подачу на объект контроля запрещенной последовательности наборов теста. Необходимость этого обусловлена особенностя- ми тестирования процессорных систем.

При размещении информации в памяти Стандартной размерности может оказаться, что не все ячейки памяти бу39 2

дут заняты. В этом случае в свободны ячейки записывается код, по которому дешифратором 7 формируется команда окончания тестирования.

Регистр 5 сдвига и сумматор 10 по модулю два обеспечивают формирование случайного значения нпадших разрядов адреса тестовых команд. При этом число входов сумматора 10 по модулю два определяется соотношением

2 f-c Гр,

где t - число входов сумматора 10 п

модулю два;

Гр - число выходов регистра 5 сдвига.

Такое соединение позволяет обеспечивать генерацию псевдослучайных чисел i размерность которых определяется числом выходов регистра 5 сдвига.

Счетчик 6 обеспечивает формирование заданного числа наборов теста. Для этого перед началом работы устройства в счетчик записывается число определяемое как разность между величиной емкости счетчика и заданным числом наборов теста. При переполнении счетчика выдается команда на окончание тестирования.

Генератор 9 тактовых импульсов обеспечивает последовательную выдачу синхроимпульсов СИ1 и СИ2,

Коммутатор 11 обеспечивает возможность формирования на информационных входах регистра 4 адреса начального адреса в период подготовки устройства к работе и адресов последуюш 1х наборов теста в период основной работы.

Устройство работает следующим образом.

Перед началом работы с помощью группы кнопок 26 и кнопки 23 блока 2 (фиг, 2) в счетчик 6 записывается число, определяемое как разность между величиной емкости счетчика и заданным числом наборов теста. После этого с помощью группы-кнопок 28 и кнопки 27 блока 2 (фиг. 2) через коммутатор 11 в регистр 4 адреса записывается адрес первого набора тес-г та. Затем адрес первого набора теста с выхода регистра 4 адреса поступает на вход памяти 1, В результате с выхода 16 на информационный вход регистра 3 поступает первый набор теста и с выхода 17 на вход дешифратора 7

31

и вход коммутатора 11 поступает информация о старших разрядах адреса следующего набора теста. Устройство готово к работе.

Для запуска устройства кнопкой 29 (фиг. 2) на выходе 22 блока 2 формируется сигнал, который поступает на S-вход триггера 8 и переводит его в единичное состояние. В результате коммутатор 11 переключается на прием информации из памяти 1 и генератора 23 псевдослучайных кодов, а также блокирует прохождение информации из блока 2. Кроме этого, триггер 8 обе- спечивает запуск генератора 9 тактовых импульсов. По первому синхроимпульсу СИ1 происходит запись первого набора теста в регистр 3, сдвиг информации в регистре 5 сдвига и форми- рование первого псевдослучайного числа - младших разрядов адреса, которые поступают вместе со старшими (с выхода 17 памяти 1) через открытый коммутатор 11 на вход регистра 4 адреса Первый синхроимпульс СИ прибавляет 1 в счетчик 6. Через определенное время после СИ1 на втором выходе генератора 9 тактовых импульсов формируется синхроимпульс СИ2, который обеспечивает запись адреса в регистр 4 адреса. Дальнейшая работа устройства происходит по описанному алгоритму.

Возможны два варианта окончания работы. В первом случае, когда реализованы все наборы теста, счетчик 6 выдает через элемент ИЛИ 14 на вход триггера 8 команду останова по переполнению. В результате триггер 8 пе- реходит в нулевое состояние и блокирует коммутатор 11 и генератор 9 тактовых импульсов. Во втором случае работа устройства блокируется при выборке из памяти 1 тестовых команд набора теста с запрещенным адресом. Этот адрес дешифрируется ешифрато- ром 7 и по приходу синхроимпульса СИ2 с выхода дешифратора 7 через открытый элемент И 12 и элемент ИЛИ 14 подается на R-вход триггера 8, что приводит к блокировке работы устройства. Формула изобретения

Устройство для формирования тесто- вых воздействий, содержащее регистр

39

адреса, постоянную память, регистр тестовых комбинаций, коммутатор, блок задания режима, генератор тактовых импульсов, триггер, элементы ИЛИ, элемент И, дешифратор, выход занесения и группа выходов задания исходного адреса блока задания режима соединены соответственно с первым входом первого элемента ИЛИ и первой группой информационных входов коммутатора, группа выходов которого соединена с группой информационных входов регистра адреса, синхровход и группа выходов которого соединены соответственно с выходом первого элемента ИЛИ и группой адресных входов постоянной памяти, группа выходов тестов которой соединена с группой информационных входов регистра тестовых комбинаций, выходы которого являются выходами устройства, выход запуска блока задания режима соединен с установочным входом триггера, .о т- личающееся тем, что, с целью расширения области применения и повышения коэффициента использования оборудования, устройство содержит генератор псевдослучайных кодов и счетчик, причем группа выходов следуюп1е- го адреса постоянной памяти соединена с входами дешифратора, второй ; группой информационных входов коммутатора и группой информационных входов генератора псевдослучайных кодов выход триггера соединен с управляющим входом коммутатора и входом за-- пуска генератора тактовых импульсов, первый выход которого соединен с счетным входом счетчика, синхровхо- дами регистра тестовых комбинаций и генератора псевдослучайных кодов, второй выход генератора тактовых импульсов соединен с вторым входом первого элемента ИЛИ и первым входом элемента И, второй вход и выход которого соединены соответственно с выходом дешифратора и первым входом второго элемента ИЛИ, выход которого соединен с входом сброса триггера, а второй вход - с выходом переполнения счетчика, группа информационных входов и вход записи которого соединены соответственно с выходами числа тестовых наборов и занесения блока ;задания режима.

Редактор Е. Копча

Фи. 3

Составитель И, Хазова Техред И.Попович Корректор А, Зимокосов

Заказ 3963/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для тестового контроля широкого класса процессорных систем. Цель изобретения состоит в расширении области применения и повьшении коэффициента использования оборудования. Устройство содержит регистр 5 сдвига, счетчик 6, триггер 8, сумматор Ю по модулю два, элемент И 12, первый и второй злементы ИЛИ 13, 14, генератор 9 тактовых импульсов, блок 1 постоянной памяти, блок 2 задания режима, регистр 3 тестовых комбинаций, регистр 4 адреса, дешифратор 7, коммутатор 11. Изобретение обеспечивает следующие преимущества: а) исключаются запрещенные комбинации команд в тестовых последовательностях и обеспечивается уменьшение временных затрат на их реализацию примерно на 50%; б) обеспечивается возможность задания множества псевдослучайных тестовых последовательностей и расширение применения устройства; в) значительно .уменьшается объем памяти ПЗУ. Последнее связлно с тем, что в ПЗУ, содержащемся в предлагаемом устройстве, записываются не все возможные разрешенные последовательности команд, а только подмножества разрешенных последователей для каждой очередной команды. 3 ил. (Л со со 4

| Устройство для диагностики логических узлов | 1980 |

|

SU892445A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

Авторы

Даты

1987-08-30—Публикация

1985-06-11—Подача