Изобретение относится к вычис.тительной технике.

Известен преобразователь напряжениекод, содержащий преобразователь код-напряжение и аналоговый сумматор, позволяющие в каждом такте получать разность преобразуемого и компенсирующего напряжений с соответствующим номеру такта весом разности 1. Это устройство имеет сложную схему.

Известен преобразователь напряжениекод, содержащий операционный усилитель, первый вход которого соединен с выходом через резистор обратной связи и с общей точкой q резисторов, второй вывод каждого из которых соединен с общими точками 2q ключевых элементов, соединенных последовательно. Выход операционного усилителя соединен с первыми входами q компараторов, вторые входы которых соединены с соответствующими выходами источника опорных напряжений. Выходы компараторов подключены к. входам кодирующего преобразователя; первый и второй опорные выходы источника опорных напряжений соединены со входами ключевых элементов. Вход элемента цифровой задержки соединен с выходом тактового генератора и с входами Т-триггера и распределителя уровней, информационные выходы которого соединены с входами элемента ИЛИ, а первый управляющий выходс входом тактового генератора 2.

Однако этот преобразователь имеет низкую точность преобразования и больпюй объем оборудования.

Целью изобретения является повышение точности преобразования и уменьщение объема оборудования.

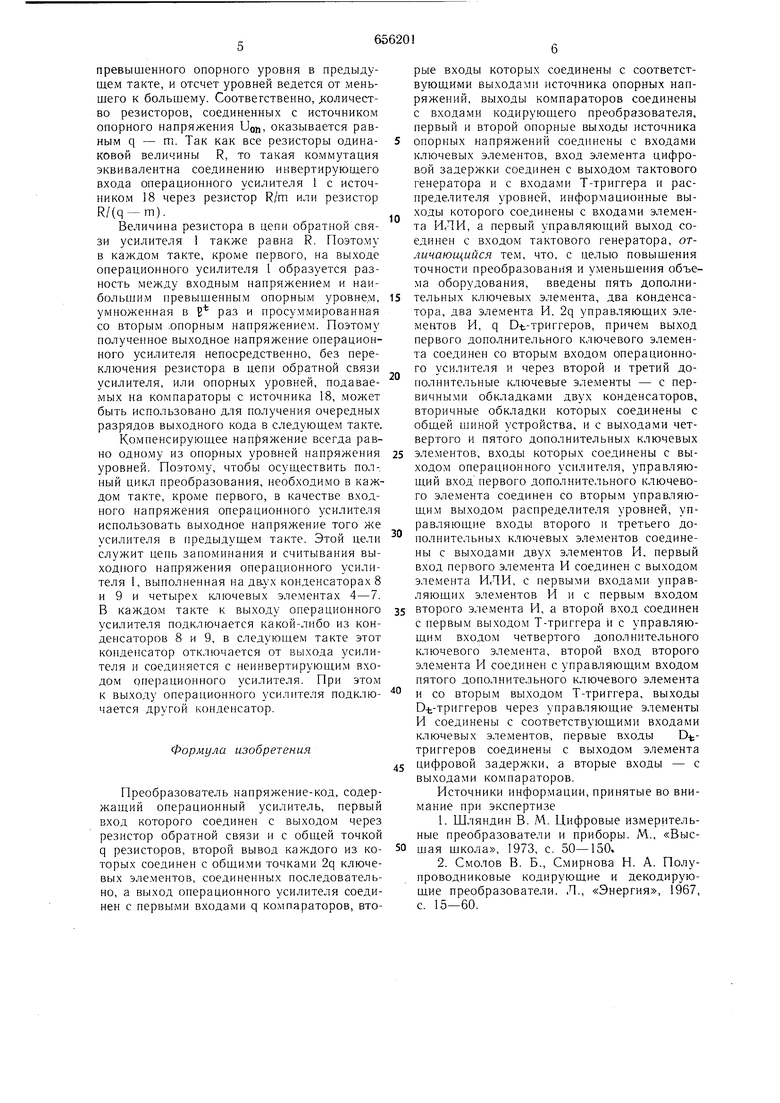

Указанная цель достигается тем, что в преобразователь напряжение-код, содержащий операционный усилитель, резистор обратной связи, q резисторов, 2q клю.чевых элементов, q компараторов, источник опорных напряжений, кодирующий преобразователь, элемент цифровой задержки, тактовый генератор, распределитель уровней, Т-триггер, элемент ИЛИ, введены пять дополнительных ключевых элементов, два конденсатора, два элемента И, 2q управляющих элементов И, q Dt-триггерОв. При этом выход первого дополнительного ключевого элемента соединен со вторым входом операционного усилителя и через второй и третий дополнительные ключевые элементы - с первичными обкладками двух конденсаторов, вторичные обкладки которых соединены с общей шиной устройства, и с выходами четвертого и пятого дополнительных ключевых элементов, входы которых соединены с выходом операционного усилителя. Управляющий вход первого дополнительного ключевого элемента соединен со вторым управляющим выходом распределителя уровней; управляющие входы второго и третьего дополнительных ключевых элементов соединены с выходами двух- элементов И. Первый вход первого элемента И соединен с выходом элемента ИЛИ, с первыми входами 2q управляющих элементов И и с первым входом второго элемента И. Второй вход первого элемента И соединен с первым выходом Т-триггера и с управляющим входом четвертого дополнительного ключевого элемента; второй вход второго элемента И соединен с управляющим входом пятого дополнительного ключевого элемента и со вторым выходом Т-триггера. Выходы О1;-триггеров через управляющие элементы И соединены с соответствующими входами ключевь х элементов, первые входы Dt-триггеров соединены с выходо.м элемента цифровой задержки, а вторые входы - с выходами компараторов. Структурная электрическая схема устройства приведена на чертеже. Устройство содержит операционный усилитель 1, резистор 2, ключевые элементы 3- 7, конденсаторы 8, 9, элементы И 10, И, элемент ИЛИ 12, распределитель 13 уровней, Т-триггер 14, тактовый генератор 15, элемент 16 цифровой задержки, кодируюаичй преобразователь 17, источник 18 опорных напряжений, q компараторов 19, q Цгтриггеров 20, 2q элементов И 21, 2q ключевых элементов 22, q резисторов 23, где q 1, t - число разрядов Е-ичного кода. С приходом импульса начала преобразования на вход запуска тактового генератора 15 последний начинает вырабатывать последовательность импульсов длительностью г с периодом повторения Т. Эта последовательность поступает на вход распределителя 13, на п выходах которого поочередно появляются тактовые импульсы длительностью Т, а на (п+ 1)-м выходе распределителя 13 импульс начинается с приходом (п + 1)-го импульса на вход распределителя 13, а заканчивается с приходом очередного импульса начала преобразования. Импульс с выхода (п Ч- 1)-го канала распределителя поступает на вход сброса тактового генератора 15 и останавливает его. Та же последовательность импульсов с выхода тактового генератора 15 поступает на вход Т-триггера 14, на одном выходе которого формируются четные тактовые импульсы, а на другом выходе - нечетные тактовые импульсы. Кроме того, эта последовательность импульсов с выхода тактового генератора 15 поступает на вход элемента 16 цифровой задержки, осуществляющего задержку последовательности на время (Т - г). Таким образом, конец 1-го импульса с выхода элемента 16 цифровой задержки совпадает с концом тактового импульса, появляющегося на выходе i-ro канала распределителя 13, а i 1,...,п. Тактовым импульсом, поступающим с выхода 1-го канала распределителя 13, открывается ключевой элемент 3. Преобразуемое напряжение поступает на инвертирующий вход операционного усилителя 1. При этом ключевые элементы 4, 6, 22 закрыты и усилитель работает с коэффициентом передачи Кпер 1. Напряжение с выхода операционного усилителя 1 поступает на один из конденсаторов, 8 или 9, в зависимости от того, какой из ключевых элементов, 5 или 7, открыт, что, в свою очередь, определяется состоянием Т-триггера перед приходом импульса начала преобразования, и запо.минается на этом конденсаторе. Это же напряжение поступает на входы компараторов 19 и сравнивается ими с рядом равностоящих опорных уровней, вырабатываемых источником 18. Результаты сравнения по каждому уровню поступают с выходов компараторов 19 на входы кодирующего преобразователя 17. Кроме того, с выхода каждого ко.мпаратора 19 сигнал поступает на информационный вход соответствуюнлего В-ь-триггера 20, осуществляющего задержку информации, поступающей во время синхронизирующего импульса, приходящего с выхода элемента 16 цифровой задержки, на время от конца этого синхронизирующего импульса до конца следующего синхронизирующего импульса. Таким образом, информация о результатах сравнения с данном такте имеется на выходах В.ь-триггеров в следующем такте. Тактовые импульсы и все последующие до п-го включительно объединяются элементом ИЛИ 12 и поступают на одни входы элементов И 21, 10, 11. При этом разрещается прохождение сигналов с выходов Dt-триггеров 20 для управления ключевы.ми элементами 22 и прохождение сигналов с выхода Т-триггера 14 для управления ключевыми элементами 3 и 6. Если в предыдущем такте какой-либо компаратор зафиксировал превышение своего опорного уровня, то в следующем такте соответствующий D -триггер открывает ключевой эле.мент, коммутирующий соответствующий резистор 23 на источник 18. В противном случае он открывает ключевой эле.мент 22, коммутирующий тот же резистор на другой вход источника 18. При этом полное число резисторов, соединенных с источником 18, равно т, где ш - номер наибольшего

превьш енного опорного уровня в предыдущем такте, и отсчет уровней ведется от меньшего к большему. Соответственно, доличество резисторов, соединенных с источником опорного напряжения UQJ,, оказывается равным q - П1. Так как все резисторы одинаковой величины R, то такая коммутация эквивалентна соединению инвертирующего входа операционного усилителя 1 с источником 18 через резистор R/m или резистор R/(q-m).

Величина резистора в цепи обратной связи усилителя 1 также равна R. Поэтому в каждом такте, кроме первого, на выходе операционного усилителя 1 образуется разность между входным напряжением и наибольшим превышенным опорным уровнем, умноженная в Е раз и просуммированная со вторым .опорным напряжением. Поэтому полученное выходное напряжение операционного усилителя непосредственно, без переключения резистора в цепи обратной связи усилителя, или опорных уровней, подаваемых на компараторы с источника 18, может быть использовано для получения очередных разрядов выходного кода в следуюшем такте.

Компенсируюшее напряжение всегда равно одному из опорных уровней напряжения уровней. Поэтому, чтобы осушествить пол-, ный цикл преобразования, необходимо в каждом такте, кроме первого, в качестве входного напряжения операционного усилителя использовать выходное напряжение того же усилителя в предыдущем такте. Этой цели служит цепь запоминания и считывания выходного напряжения операционного усилителя 1, выполненная на даух конденсаторах 8 и 9 и четырех ключевых элементах 4-7. В каждом такте к выходу операционного усилителя подключается какой-либо из конденсаторов 8 и 9, в следующем такте этот конденсатор отключается от выхода усилителя и соединяется с неинвертируюшим входом операционного усилителя. При этом к выходу операционного усилителя подключается другой конденсатор.

Формула изобретения

Преобразователь напряжение-код, содержаший операционный усилитель, первый вход которого соединен с выходом через резистор обратной связи и с общей точкой q резисторов, второй вывод каждого из которых соединен с обшими точками 2q ключевых эле.ментов, соединенных последовательно, а выход операционного усилителя соединен с первыми входами q компараторов, вторые входы которых соединены с соответствующими выходами источника опорных напряжений, выходы компараторов соединены с входами кодирующего преобразователя, первый и второй опорные выходы источника

опорных напряжений соединены с входами ключевых элементов, вход элемента цифровой задержки соединен с выходом тактового генератора и с входами Т-триггера и распределителя уровней, информационные выходы которого соединены с входами элемента ИЛИ, а первый управляющий выход соединен с входом тактового генератора, отличающийся тем, что, с целью повышения точности преобразования и уменьшения объема оборудования, введены пять дополнительных ключевых элемента, два конденсатора, два элемента И, 2q управляющих элементов И, q Dt-триггеров, причем выход первого дополнительного ключевого элемента соединен со вторым входом операционного усилителя и через второй и третий дополнительные ключевые элементы - с первичными обкладками двух конденсаторов, вторичные обкладки которых соединены с общей щиной устройства, и с выходами четвертого и пятого дополнительных ключевых

5 элементов, входы которых соединены с выходом операционного усилителя, управляющий вход первого дополнительного ключевого элемента соединен со вторым управляющим выходом распределителя уровней, управляюшие входы второго и третьего дополнительных ключевых элементов соединены с выходами двух элементов И, первый вход первого элемента И соединен с выходом элемента ИЛИ, с первыми входами управляющих эле.ментов И и с первым входом

5 второго элемента И, а второй вход соединен с первым выходом Т-триггера и с управляющим входом четвертого дополнительного ключевого элемента, второй вход второго элемента И соединен с управляющим входом пятого дополнительного ключевого элемента

и со вторым выходом Т-триггера, выходы D-t-триггеров через управляющие элементы И соединены с соответствующими входами ключевых элементов, первые входы D.триггеров соединены с выходом элемента

5 цифровой задержки, а вторые входы - с выходами компараторов.

Источники информации, принятые во внимание при экспертизе

1.Шляндин В. М. Цифровые измерительные преобразователи и приборы. М., «Выс0 шая щкола, 1973, с. 50-150,

2.Смолов В. Б., Смирнова Н. А. Полупроводниковые кодирующие и декодирующие преобразователи. Л., «Энергия, 1967, с. 15-60.

влод

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| ЭЛЕКТРОННЫЙ СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ | 1993 |

|

RU2075755C1 |

| Устройство для контроля и регулировки положения очесывающего барабана льноуборочного комбайна | 1990 |

|

SU1821066A1 |

| Интегрирующий преобразователь постоянного напряжения в код | 1988 |

|

SU1672565A1 |

| ДИАГНОСТИЧЕСКОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ АМПЕРОМЕТРИЧЕСКОГО ОПРЕДЕЛЕНИЯ ТОКА | 1994 |

|

RU2136204C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

Авторы

Даты

1979-04-05—Публикация

1974-06-17—Подача