Изобретение относится к электросвязи.

Известно устройство для коммутации цифровых сигналов, содержащее накопительные блоки, информационные выходы которых подключены ко входам блока коммутации, управляющий вход которого соединен с выходом блока управления, к перв(му входу которого подключен выход анализатора фаз, вход которого соединен с контрольными выходами накопительных блоков, к тактовым входам которых подключен выход тактового генератора, а выход блока коммутации соединен со вторым входом блока управления 1.

Однако в известном устройстве недостаточная точность коммутации.

Цель изобретения - повышение точности коммутации.

Для этого в устройство коммутации цифровых сигналов, содержащее накопительные блоки, информационные выходы которых подключены ко входам блока коммутации, управляющий вход которого соединен с выходом блока управления, к первому входу которого подключен выход анализатора фаз, вход которого соединен с контрольными выходами накопительных блоков, к тактовым входам которых подключен выход тактового генератора, а выход блока коммутации соединен со вторым входом блока управления, введен определитель фазового сдвига, первый выход которого подключен к управляющим входам накопительных блоков, дополнительные информационные выходы которых подключены к дополнительным входам блока коммутации, дополнительные выходы которого соединены со входами определителя фазового сдвига, второй вход которого подключен к третьему входу блока управления, при этом третий и четвертый выходы определителя фазового сдвига соединены с соответствуюцхими входами блока коммутации.

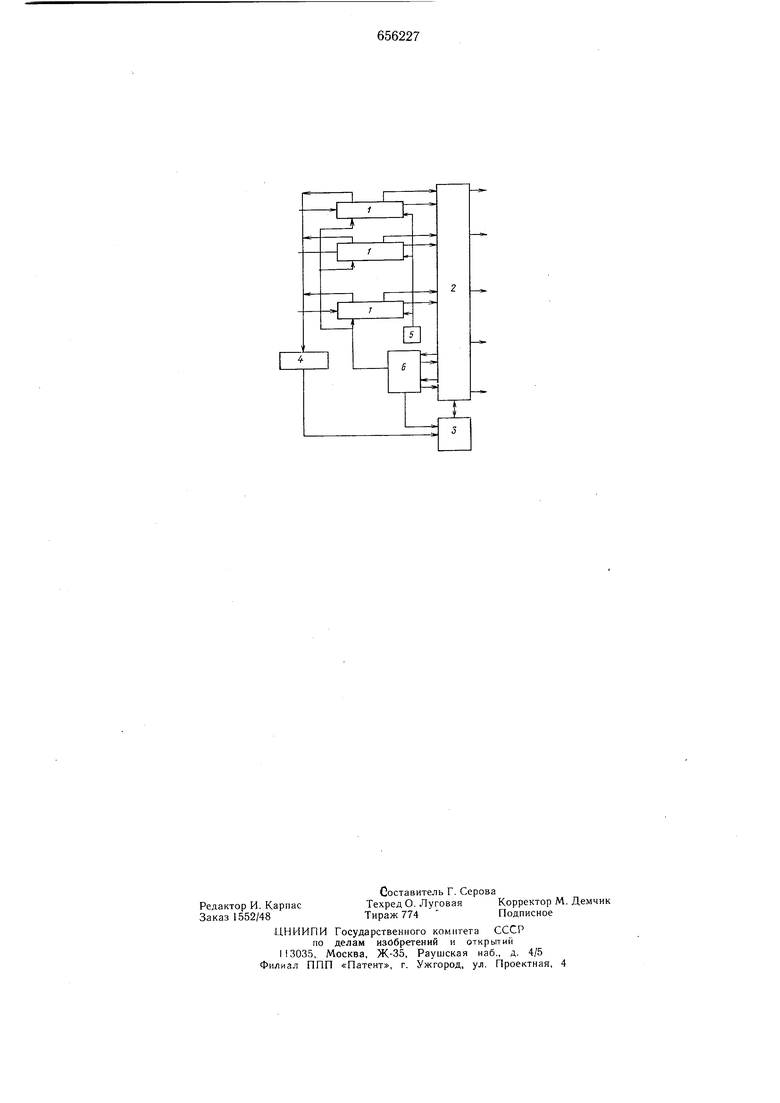

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит накопительные блоки 1, блок коммутации 2, блок управления 3, анализатор фаз 4, тактовый генератор 5, определитель 6 фазового сдвига.

Устройство работает следующим образом.

Блок коммутации 2 обеспечивает по командам блока управления 3 соединение соответствующих входа и выхода. К блоку коммутации 2 подключаются дискретные ка-.

налы связи. Накопительные блоки 1 обеспечивают no-битную занись бит информации, поступающей на вход системы коммутации от. оконечного источника канала связи. Считывание информации из накопительного блока 1 осундествляется также побитно общеузловым тактовым генератором 5. Временной интервал между моментами записи и считывания информации определяется командами, поступающими из определителя 6 фазового сдвига, а при их отсутствии темпом записи и считываниг информации. Анализатор фаз 4 определяет временной интервал между моментом записи и считывания информации в каждом из накопительных блоков 1.

При очередном установлении соединения считывание информации из накопительного блока 1 в канал по основному информационному выходу осуществляется тактовым генератором 5 со средней ячейки. При этом информация задерживается на N тактовых интервалов. Если номинал частот генераторов источника информации и уз.ла не совпадают, то фазовое расстояние между моментом записи и считывания информации будет либо увеличиваться, либо уменьщаться. Это означает, что через определенное время считывание информации будет осуществляться с одной из крайних ячеек накопительного блока.

Анализатор фаз при заполнении (освобождении) накопительного блока выдает команду в управляющее устройство об образовании дополнительного капала к оконечному или транзитному углу связи. Блок управления обеспечивает соединение дополнительного выхода накопительного блока 1 с одним из входов оконечного узла связи. На дополнительный выход информация считывается, например, со средней ячейки накопительного блока 1. При этом тракт связи может проходить через несколько узлов связи.

На оконечном узле связи выходы подключаются к входам определителя 6 фазового сдвига, в котором определяется величина фазового смещения информационного сигнала в основном и дополнительном каналах (связь основного кана.ла с выходом не прерывается).

При этом появляется необходимость задержки сигнала в тракте основного или дополнительного каналов. Если, например, задержка в дополнительном тракте больще, чем в основном, то определителем 6 фазового сдвига вводится соответствующая задержка в основной тракт. Выход канала подключают к дополнительной линии задержки и путем уменьщения темпа считывания информации выравнивают фазы сигналов в основном и дополнительном каналах.

После выравнивания фаз выход накопительного блока дополнительного канала подключается к выходу блока коммутации 2, освобождают основной канал и определитель фазового сдвига. При очередном заполнении (освобождении) буферного накопителя дополнительный канал подключается к соответствующему выходу.

Формула изобретения

Устройство для коммутации цифровых сигналов, содержащее накопительные блоки, информационные выходы которых подключены ко входам блока коммутации, управляющий вход которого соединен с выходом блока управления, к первому входу которого подключен выход анализатора фаз, вход которого соединен с контрольными вь ходами накопительных блоков, к тактовым входам которых подключен выход тактового генератора, а выход блока коммутации соединен со вторым входом блока управления, отличающееся тем, что, с целью повышения точности коммутации, введен определитель фазового сдвига, первый выход которого подключен к управляющим входам накопительных блоков, дополнительные информационные выходы которых подключены к дополнительным входам блока коммутации, дополнительные выходы которого соединены со входами определителя фазового сдвига, второй выход которого подключен к третьему входу блока управления, при этом третий и четвертый выходы определителя фазового сдвига соединены с соответствующими входами блока коммутации.

Источники информации, принятые во внимание при экспертизе

1. Левин Л. С. Основы построения цифровых систем передачи. М., «Связь, 1975, с. 82.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОМПЕНСАЦИИ ФАЗОВЫХ СМЕЩЕНИЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИНФОРМАЦИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014757C1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| Канальное устройство объединенного коммутатора каналов и сообщений | 1975 |

|

SU531295A1 |

| Устройство для сопряжения ЦВМ | 1987 |

|

SU1494008A1 |

| Устройство коммутации асинхронных цифровых сигналов | 1989 |

|

SU1633525A1 |

| Устройство переприема двоичных сигналов | 1977 |

|

SU640432A1 |

| Многоканальный интерфейс | 1990 |

|

SU1751774A1 |

| Многоканальное устройство передачи и приема асинхронных цифровых сигналов | 1988 |

|

SU1555886A1 |

| Коммутатор изохронных каналов | 1978 |

|

SU725259A1 |

| СИСТЕМА СВЯЗИ | 1985 |

|

SU1840076A1 |

Авторы

Даты

1979-04-05—Публикация

1977-03-14—Подача