со

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

Изобретение относится к вычислительной технике и может быть использовано для передачи информации между ЦВМ. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения работы по каналам связи с нестабильным временем распространения. Устройство содержит первый блок 1 коммутации, первый блок 2 управления, первый блок 3 синхронизации, блок 4 приема информации, группу 5 усилителей, второй блок 6 коммутации, второй блок 7 управления, блок 8 передачи информации, группу 9 блоков хранения данных, второй блок 10 синхронизации. Устройство обеспечивает прием и передачу пакета данных по нескольким каналам связи одновременно. 5 ил.

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано для передачи информации между ЦВМ.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения работы по каналам связи с нестабильным временем распространения.

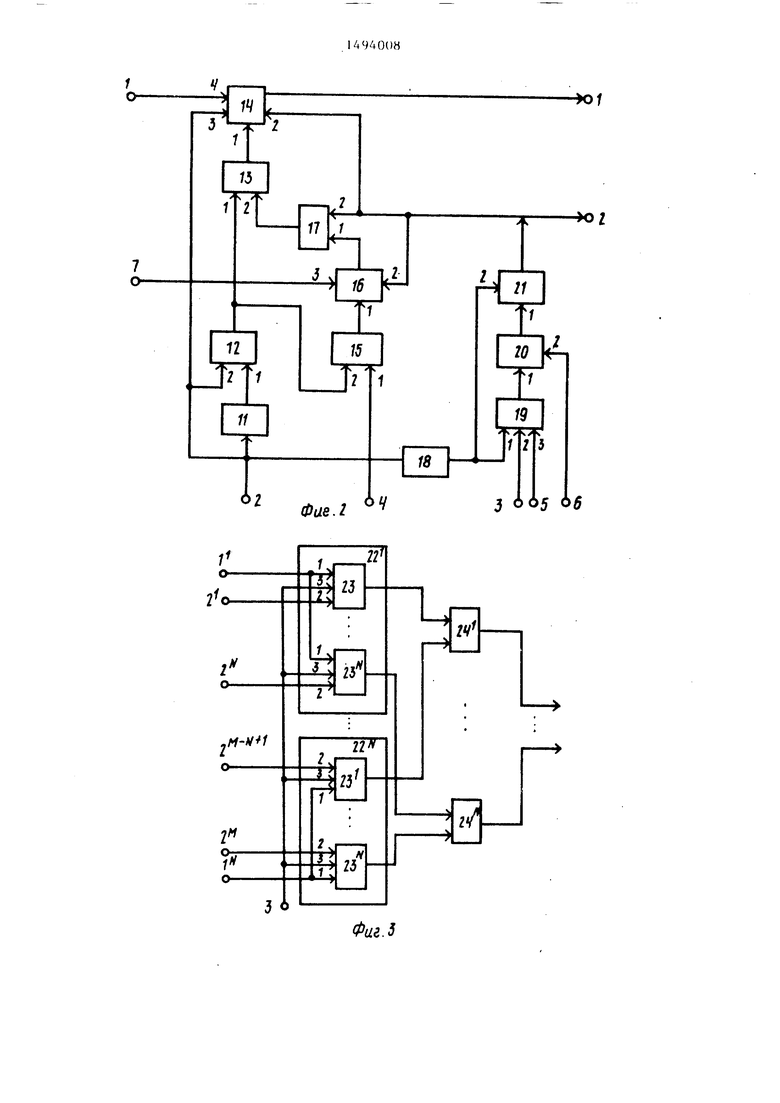

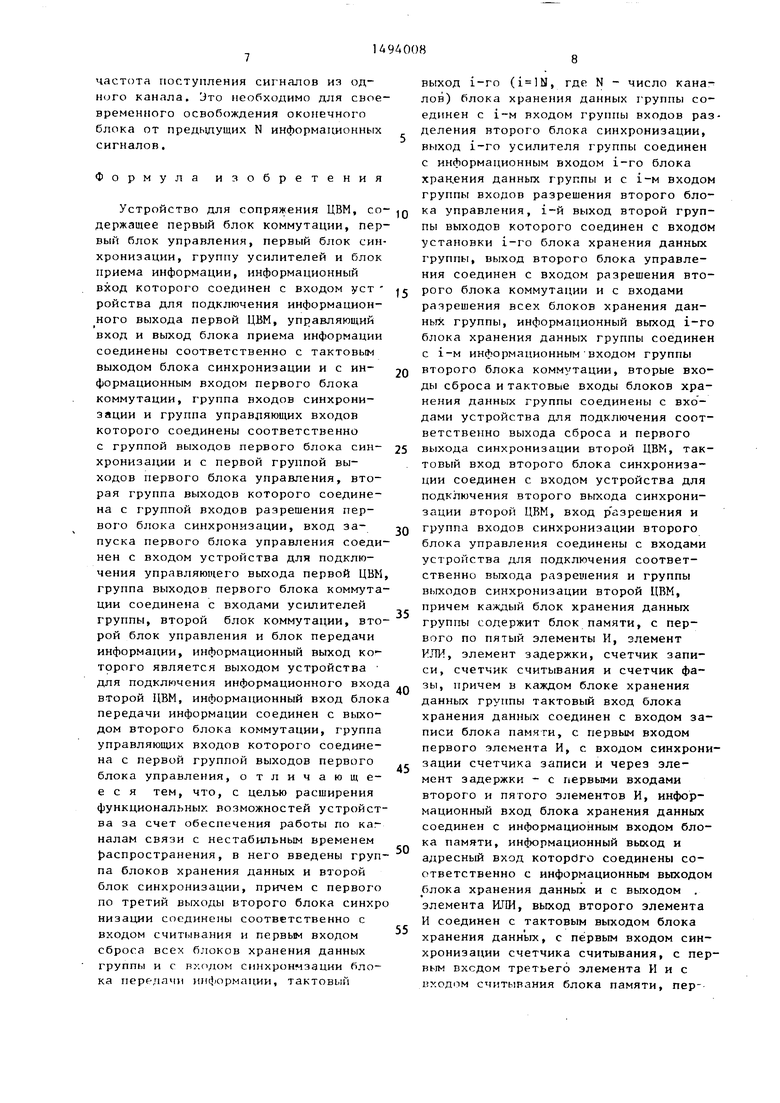

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - схема одного из блоков хранения данных; на фиг.З - схема блока 6 коммутации; на фиг.А - схема блока 7 ществляемая тактовыми импульсами по равления; на фиг.З - схема блока 10 синхронизации.

Устройство содержит первый блок 1 коммутации, п-ервый блок 2 управления, первый блок 3 синхронизации, блок А приема информации, группу усилителей 5-5,второй блок 6 коммутации, второй блок 7 управления, блок 8 передачи информации, группу блоков д -У

цепи: тактовый вход - счетчик 11 записи - первый элемент И 12 - элемент ИЛИ 13 - адресный вход блока 1А. В результате поступающие сигналы за- 20 писываются в ячейки памяти блока 1А адреса которых указывает счетчик 1I. Одновременно в анализаторе 25 вьде- ляется служебный сигнал, по которому определяется порядковый номер счи

хранения данных и второй блок 10 синх-25 тывания информации из соответствующего блока 9 по отношению к другим блокам, при этом сигналы поступают через открытый триггером 28 в исходном состоянии элемент И 29 в регистр

ронизации.

Каждый из блоков 9 хранения данных группы содержит счетчик 11 записи, первый элемент И 12, элемент ИЛИ

13, блок 1А памяти, четвертый элемент 30 30 сдвига и при появлении в нем

И 13, счетчик 16 считывания, третий элемент И 17, элемент 18 задержки, пятый элемент И 19, счетчик 20 фазы и второй .элемент И 21.

Блок 6 коммутации содержит группу 22-22 блоков элементов И 23 -23 и группу 2А элементов ИЛИ 2А -2А .

Блок 7 управления содержит группу анализаторов , элемент И 26 и триггер 27. Каждый из анализаторов 25 содержит триггер 28, элемент И 29, регистр 30 сдвига, дешифратор 31 и элемент ИЛИ 32.

Блок 10 синхронизации содержит первый одновибратор 33, группу триггеров ЗА -ЗА, первый 35 и второй 36 элементы И, второй одновибратор 37, третий элемент И 38, счетчик 39 и дешифратор АО.

Устройство работает следующим об- разом.

Информационные сигналы поступают в блок А приема информации, а затем

через блок 4 коммутации поступают на

;i-sN

служебного сигнала на одном из выхо дов дешифратора 31, подключенного к выходу регистра 30 сдвига, появляет ся потенциал, под воздействием кото

35 рого происходят следующие действия:

триггер 28 перебрасывается, в ре зультате в регистре 30 запоминается служебный сигнал, под воздействием которого на соответствующем выходе

40 дешифратора 31 поддерживается посто янный потенциал:

через элемент ИЛИ 32 потенциал п ступает на один из входов элемента И 26, подгот-вливая его к открытию;

45

50

с одного из управляющих выходов анализатора 23 потенциал поступает в блок 6 коммутации ча один из элементов И 23 соответствующей группы 22, подготавливая ее к открытию;

через элемент ИЛИ 32 потенциал п ступает на фазовый выход анализатор 23 и далее на вход установки соответствующего блока 9 группы, откры

усилители 3 тЗ . Общая частота считы-сс вает в нем элемент И 15 и в данный

вания информации и количество индивидуальных тактовых последовательностей, поступающих с.блока.3 соответственно на блоки А и 1 зависят от колитакт записи Показание счетчика 11 (адрес соответствующей ячейки памяти блока 1А) поступает на вход ус- тановкь счетчика 16 считывания, оп

честна предоставляемых каналов связи. Управление блоком 3 синхронизации и блоком 1 коммутации осуществляется с блока 2 управления под воздействием управляющих сигналов, поступаю- цих на него извне. На приемной стороне сигналы с выхода усилителей З поступают на информационные входы блоков на информационные входы анализаторов блока 7 управления, В каждом блоке 9 происходит накопление сигналов, а в блоке 1А памяти происходит запись сигналов, осугществляемая тактовыми импульсами по

цепи: тактовый вход - счетчик 11 записи - первый элемент И 12 - элемент ИЛИ 13 - адресный вход блока 1А. В результате поступающие сигналы за- писываются в ячейки памяти блока 1А адреса которых указывает счетчик 1I. Одновременно в анализаторе 25 вьде- ляется служебный сигнал, по которому определяется порядковый номер счислужебного сигнала на одном из выходов дешифратора 31, подключенного к выходу регистра 30 сдвига, появляется потенциал, под воздействием кото5 рого происходят следующие действия:

триггер 28 перебрасывается, в результате в регистре 30 запоминается служебный сигнал, под воздействием которого на соответствующем выходе

0 дешифратора 31 поддерживается постоянный потенциал:

через элемент ИЛИ 32 потенциал поступает на один из входов элемента И 26, подгот-вливая его к открытию;

5

0

с одного из управляющих выходов анализатора 23 потенциал поступает в блок 6 коммутации ча один из элементов И 23 соответствующей группы 22, подготавливая ее к открытию;

через элемент ИЛИ 32 потенциал поступает на фазовый выход анализатора 23 и далее на вход установки соответствующего блока 9 группы, открытакт записи Показание счетчика 11 (адрес соответствующей ячейки памяти блока 1А) поступает на вход ус- тановкь счетчика 16 считывания, определяя ему начальное состояние считывания.

При появлении потенциалов на всех входах элемента И 26 на выходе триггера 27 появляется разрешающий сигнал, который поступает на разрешающие входы всех блоков 9 группы и на третьи входы всех элементов И 23 всех групп 22. Поступающий на разрешающий вход блока 9 т руппы сигнал отрывает элемент И 19 (на его третьем входе в исходном состоянии присутствует потенциал с выхода дешифратора 40 блока 10 синхронизации). С тактового входа блока 9 группы тактовый импульс через элемент 18 задержки поступает на второй вход элемента И 2 и одновременно через элемент И 19 переводит счетчик 20 фазы из состояния 00 в состояние 01 так, что элемент И 21 открывается и тактовый импульс проходит через него на вход считьгоания блока 1А памяти, а также открывает третий элемент И 17 и считывает со счетчика 1Ь через элемент И 17 и элемент Ш1И 13 очередной адрес, который поступает на адресный вход блока 14 памяти и по которому происходит

считывание информации через информа- ЗО Одновибратор 33 служит для надежного

ционный выход блока 9 группы, соответствующий информационный вход блока 6 коммутации, открытый элемент И 23 соответствующей группы 22 и соот- ветствую1ций элемент ИЛИ 2А на вход блока 8 в разряд, определяемый порядковым номером считывания. Элемент 18 задержки служит для сдпига тактового импульса на время, обеспечивающее

неодновременность считывания кода ад- 40 мера ограничения импульсо считываресов со счетчика 11 записи и счетчика 16 считывания. Одновременно со считыванием информации из блока 14 памяти импульс считывания поступает через тактовый выход одного из блоков 9 группы на один из индивидуальных тактовых входов блока 10 синхронизации, а на другие индивидуальные тактовые входы поступают импульсы считывания и ч х ругих канальных комплектов.

При использовании кяналор связи с нестабильным врсме ием распространения сигналов и ф; |рм;1рования тактовых частот из информационных сигналов возникает эффект расхождения индивидуальных тактов1,1х импульсов записи (считывания) на приеме относительно друг друга. В этом случае импульсы на

индивидуальных тактовых входах блока 10 синхронизации появляются также со сдвигом во времени относительно друг друга. Под воздействием каждого импульса соответствующий триггер ЗА устанавливается в единичное состояние. При установке всех триггеров ЗА -3 в единичное состояние на выQ ходе элементов И 35 появляется потенциал, открывающий элемент И 36, подготовленный к открытию в исходном состоянии потенциалом с выхода дешифратора АО. Па третий вход элемента

5 И 36 поступает импульс общей тактовой последовательности, в результате чего потенциал с выхода элемента И 36 запускает одновибратор 37, на выходе которого образуется потенциал

0 длительности, достаточной для прохождения через элемент И 38 N тактовых импульсов с тактового входа блока 10 синхронизации на вход счетчика 39. В течение первых N-1 импульсов на выхо5 де дешифратора 40 потенциал отсутствует, а затем i-й импульс вновь переводит счетчик 39 в исходное состояние, в результате чего на выходе дешифратора АО появляется потенциал.

Одновибратор 33 служит для надежного

сбрасывания всех триггеров 34-34 в нулевое состояние. Кроме того, с выхода элемента И 35 импульс поступает через второй управляющий выход блока 10 синхронизации на входы сброса фазы всех блокоп хранения данных и на входы сброса счетчиков 20 фазы, которые закрывают элементы И.21 каналов группы блоков 9-9. Подобная

ния вызвана тем же сдвигом индиви дуальных такторих импульсов относительно друг друга, о котором было изложено выше. Во время работы счетчика 39 на первом управляющем выходе блока 10 синхронизации потенциал отсутствует, поэтому элементы 1,1 19- каналов группы блоков не пропускают импульс для переброса счетчика 20

фазы в следующее состояние. С тактового выхода блока 10 синхронизации общие тактовые импу. поступают на тактовый вход оконечного блока 8 и осуществляют счит-ыпппие информации

в порядке, опреде.чяемом служебными сигналами.

Частота К общлх тактовых импульсов на приеме Д11.п;-ч1;) Оыть больше величины N f, r;u t - номинальная

частота поступления сигналов из одного канала. DTO необходимо для своевременного освобождения оконечного блока от предыдущих N информационных сигналов.

Формула изобретения

Устройство для сопряжения ЦВМ, содержащее первый блок коммутации, пер блок управления, первый блок синхронизации, группу усилителей и блок приема информации, информационный вход которого соединен с входом уст - ройства для подключения информационного выхода первой ЦВМ, управляющий вход и выход блока приема информации соединены соответственно с тактовым выходом блока синхронизации и с информационным входом первого блока коммутации, группа входов синхронизации и группа управляющих входов которого соединены соответственно с группой выходов первого блока синхронизации и с первой группой выходов первого блока управления, вторая группа выходов которого соединена с группой входов разрешения первого блока синхронизации, вход запуска первого блока управления соединен с входом устройства для подключения управляющего выхода первой ЦВМ группа выходов первого блока коммутации соединена с входами усилителей группы, второй блок коммутации, второй блок управления и блок передачи информации, информационный выход которого является выходом устройства для подключения информационного вход второй ЦВМ, информационный вход блок передачи информации соединен с выходом второго блока коммутации, группа управляющих входов которого соединена с первой группой выходов первого блока управления, отличающ е- е с я тем, что, с целью расщирения функциональных возможностей устройства за счет обеспечения работы по каг налам связи с нестабильным временем 1эаспространения, в него введены группа блоков хранения данных и второй блок синхронизации, причем с первого по третий выходы второго блока синхр низации соединены соответственно с входом счит1 1нания и первым входом сброса всех блоков хранения данных группы и с входом cfiHxpoH43anHH блока nepejiaMn информации, тактовый

5

0

5

0

5

0

5

0

5

выход i-ro (, где N - число каналов) блока хранения данных группы соединен с i-M входом группы входов разделения второго блока синхронизации, выход i-ro усилителя группы соединен с информационным входом i-ro блока хранения данных группы и с i-м входом группы входов разрешения второго блока управления, i-й выход второй группы выходов которого соединен с входом установки i-ro блока хранения данных группы, выход второго блока управления соединен с входом разрешения второго блока коммутации и с входами разрешения всех блоков хранения данных группы, информационный выход 1-го блока хранения данных группы соединен с i-M информационным ВХОДОМ группы второго блока коммутации, вторые входы сброса и TaKTOBbie входы блоков хранения данных группы соединены с входами устройства для подключения соответственно выхода сброса и первого выхода синхронизации второй ЦВМ, тактовый вход второго блока синхронизации соединен с входом устройства для подключения второго выхода синхронизации второй ЦВМ, вход р йзрешения и группа входов синхронизации второго блока управления соединены с входами устройства для подключения соответственно выхода разрешения и группы выходов синхронизации второй ЦВМ, причем каждый блок хранения данных группы содержит блок памяти, с первого по пятый элементы И, элемент ИЛИ, злемент задержки, счетчик записи, счетчик считывания и счетчик фазы, причем в каждом блоке хранения данных группы тактовый вход блока хранения данных соединен с входом записи блока памяти, с первым входом первого элемента И, с входом синхронизации счетчика записи и через элемент задержки - с первыми входами второго и пятого элементов И, информационный вход блока хранения данных соединен с информационным входом блока памяти, информационный выход и адресный вход которого соединены соответственно с информационным выходом блока хранения данных и с выходом . элемента ИЛИ, выход второго элемента И соединен с тактовым выходом блока хранения данных, с первым входом синхронизации счетчика считывания, с первым входом третьего элемента И и с ПХОД11М считывания блока памяти, первый и второй входы сброса, установочный вход,.входы разрешения и считывания блока хранения данных соединены соответственно с входами сброса счетчиков считывания и фазы, с первым входом четвертого элемента И, с вторым и третьим входами пятого элемента И, выход которого «единен с тактовым входом счетчика фазы, вы- ход которого соединен с вторым входом второго элемента И, выход счетчика записи соединен с вторым входом первого элемента И, выход которого соединен с первым входом зле- мента ИЛИ и с вторым входом четвертого элемента И, выход которого соединен с вторым входом синхронизации счетчика считывания, выход которого соединен с в;горым входом третьего элемента И, выход которого соединен с вторым входом элемента ИЛИ, причем второй блок управления содержит триггер,:элемент И и группу анализаторов, причем во втором блоке управления вход разрешения блока управления соединен с информационными входами всех анализаторов группы и триггера, выход которого соединен с выхо дом разрешения блока управления, i-й вход (,N) группы входов разрешения блока управления соединен с входом разрешения i-ro анализатора группы, i-й вход группы входов синхронизации блока управления - с входом синхронизации i-ro анализатора группы, группа выходов выборки i-ro анализатора группы - с i-й подгруппой первой группы выходов блока управления, выход обращения i-ro анализато- ра группы - с i-M выходом второй груп группы выходов блока управления и с i-M входом элемента И, вькод которого соединен с входом синхронизации триггера, причем каждый анализатор группы содержит триггер, дешифратор регистр сдвига, элемент И и элемент

ИЛИ, причем в каждом анализаторе группы входы разрешения, синхрониза - ции и информационный соединены соответственно с первым входом элемента И, с входом синхронизации регистра ; сдвига и с информационным входом тригера, выход триггера соединен с втог рым входом элемента И, выход которого соединен с информационным входом регистра сдвига, выход которого соединен с входом дешифратора, группа: выходов которого соединена с группой выходов выборки анализатора и с группой входов элемента ИЛИ, выход котог рого соединен с выходом обращения блока управления и с входом синхронизации триггера, причем второй блок синхронизации устройства содержит первый и второй одновибраторы, групп триггеров, первый, второй и третий элементы И, счетчик и дешифратор, причем.во втором блоке синхронизации i-й вход разрешения блока синхронизации соединен с входом синхронизации i-ro триггера гру ппы, вькод которого соединен с i-м входом первого элемента И, выход которого соединен с вторым выходом блока синхронизации, с первым входом второго элемента И и через псфвый одновибратор - с нулевыми входами триггеров группы, выход дешифратора является первым выходом блока синхронизации и соединен с вторым входом второго элемента И, вход синхронизации блока синхронизации соединен с третьим входом второго элемента И с первым входом третьего элемента И., вьгхо1 второго элемента И соединен с входом второго одновибратора, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с третьим выходом блока синхронизации и со счетным входом счетчика, группа информационных выходов которого соединена с группой входов дешифратора.

oz

3 665 65

Фие.

Фи.Ч

| Сети ЭВМ/Под ред | |||

| В.К.Глушко- ва | |||

| М.: Связь, 1977, с | |||

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| Авторское свидетельство СССР по заявке № 4116501/2А-09, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-15—Публикация

1987-11-02—Подача