Ю

f

1-

Ч- Чг-1 t

05 СО

со Сл

to

ел

Изобретение относится к электросвязи и может быть использовано в цифровых коммутационных станциях.

Целью изобретения является повы- шение точности коммутации и повышение пропускной способности.

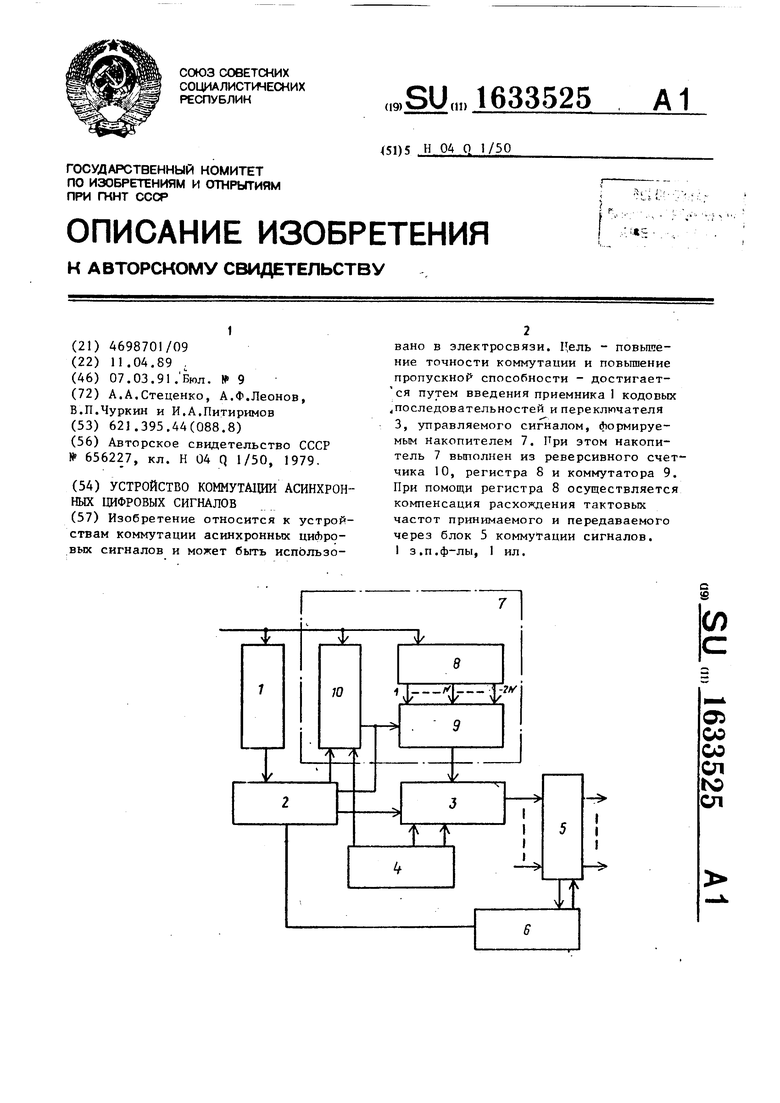

На чертеже представлена структурная электрическая схема устройства коммутации асинхронных цифровых сиг- налов.

Устройство содержит приемник 1 кодовых последовательностей, анализатор 2 фаз, переключатель 3, генератор 4, блоки коммутации 5 и управ- ления 6, накопитель 7, содержащий регистр 8, коммутатор 9 и реверсивный счетчик 10.

Устройство работает следующим образом.

При установлении соединения по одной из двух линий с выхода блока 6 на вход анализатора 2 поступает сигнал, в соответствии с которым в последнем формируется код установки начальной задержки информации на N бит в регистре 8 накопителя 7. Этот код поступает на установочный вход реверсивного счетчика 10 с выхода установки фазового смещения анализа- тора. На установочный вход накопителя 7 с анализатора 2 подается код, изменяющий фазу считывания последовательности информационных сигналов, поступающей по одной из линий на вход регистра 8. По второй линии на вход регистра 8 подается тактовая частота линейного сигнала. Число разрядов К установки счетчика 10 определяется равенством 2 2N, где N - половина емкости регистра 8.

Код установки начальной задержки фазирует счетчик 10 и поступает с его выхода на вход управления коммутатора 9 и вход анализа задержки анализатора 2. Коммутатор 9 при этом подключает/ /выход регистра 8 через свой информационный выход к информационному входу переключателя 3, ,а анализатор 2 контролирует правиль- ность начальной установки считывания Одновременно с управляющего выхода анализатора 2 на вход переключателя 3 подается сигнал для подключения его информационного входа к входу блока 5. Таким образом осуществляетс подключение соединительного тракта к блоку 5 и начальная задержка информации на N бит.

На тактовый вход счетчика 10 поступает тактовая частота линейного сигнала, на второй вход которого с I выхода генератора 4 подается местная тактодля частот. В общем случае эти тактовые частоты отличаются между собой величиной и знаком, поэтому с течением времени их фазы сменятся на К линияхjHa выходах реверсивного счетчика 10 появится новое сочетание сигналов, устанавливающее считывание информации с (N - 1) или (N + 1) ячейки регистра 8.

При продолжительном смещении тактовых частот считывание постепенно переместится в 1-ю или 2N-IO ячейку регистра 8, а на вход анализатора 2 с выхода счетчика 10 поступает соответствующий номерам этих ячеек код считывания, указывающий на то, что запас емкости регистра для компенсации дальнейшего расхождения тактовых частот соответствует их относительному смещению на один период. С выхода блока 6 на вход анализатора 2 постоянно поступают сигналы системы единого времени. Анализатор 2 при наличии на его входе анализатора задержки сигнального кода указывающего на считывание информации с одной из крайних ячеек регистра 8 формирует и подает на вход управления переключателя 3 в ближайшем интервале сигнал для соединения выхода переключателя 3 с одним из его входов, подключенных к генератору 4. При этом с одного из выходов генератора 4 через блок 5 коммутации в соединительный тракт передается одна из двух кодовых последовательностей, соответствующая направлению смещения считывания информации с регистра 8. На следующей станции соединительного тракта при выделении в приемнике 1 кодовой последовательности с его выхода на вход анализатора 2 поступает сигнал, указывающий на смещение считывания информации в одну из крайних ячеек регистра 8 предыдущей станции. В анализаторе 2 осуществляется сопоставление сигналов на входах анализа задержки и дешифрации кодовых последователь- ностей и формирование сигналов на выходе установки фазового смещения и управляющем выходе. ,

Таким образом, образовавшиеся на нескольких станциях смещения фазы считывания информационных сигналов как бы транслируются по соединительному тракту через промежуточные до входяпчей станции. Осуществляется компенсация смещения Фазы путем изменения темпа считывания информации с его накопителя 7.

Максимальное число таких трансляций при одновременном и одностороннем заполнении накопителей на всех станциях равно числу станций в соединительном тракте.

теля, установочные вход которого соединен с вьтшдом установки базового смещения анализатора фаз, вход кода установки начальной задержки которого соединен с вторым выходом блока управления, вход накопителя объединен с входом приемника кодовых последовательностей, выход которого подклю- чен к входу дешифрации анализатора фаз, управляющий выход которого подключен к управляющему входу переключателя, выход которого подключен к входу блока коммутации, а два допол- / 1. Устройство коммутации асинхронных ,,- нительных входа переключателя соеди10

Формула изобретения

цифровых сигналов, содержащее блок коммутации, блок управления, вход и первый выход которого подключены соответственно к выходу и управляющему входу блока коммутации, накопитель, 20 контрольный выход которого соединен с входом анализа задержки анализатора фаз, и генератор, выход которого подключен к тактовому входу накопителя, отличающееся тем,25 что, с целью повышения точности коммутации и повышения пропускной способности, введены приемник кодовых последовательностей и переключатель, информационный вход которого подклю- 30 чен к информационному выходу накопинены с кодовыми выходами генератора,

2. Устройство поп.1, отличающееся тем, что накопитель содержит регистр, выходы которого подключены к входам коммутатора, управляющий вход которого подключен к выходу реверсивного счетчика, первый вход которого объединен с входом регистра и является входом накопителя, информационным выходом которого является выход коммутатора, управляющий вход которого соединен с контрольным выходом накопителя, установочным и тактовым входами которого являются одноименные входы реверсивного счетчика.

,,-

10

нены с кодовыми выходами генератора,

2. Устройство поп.1, отличающееся тем, что накопитель содержит регистр, выходы которого подключены к входам коммутатора, управляющий вход которого подключен к выходу реверсивного счетчика, первый вход которого объединен с входом регистра и является входом накопителя, информационным выходом которого является выход коммутатора, управляющий вход которого соединен с контрольным выходом накопителя, установочным и тактовым входами которого являются одноименные входы реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство коррекции кода | 1986 |

|

SU1490720A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| СПОСОБ КОМПЕНСАЦИИ ФАЗОВЫХ СМЕЩЕНИЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИНФОРМАЦИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014757C1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для селекции признаков подвижных объектов | 1989 |

|

SU1691860A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

Изобретение относится к устройствам коммутации асинхронных циАро- вых сигналов и может быть использовано в электросвязи. Цель - повышение точности коммутации и повышение пропускной способности - достигает- ся путем введения приемника 1 кодовых последовательностей и переключателя 3, управляемого сигналом, формируемым накопителем 7. При этом накопитель 7 выполнен из реверсивного счет чика 10, регистра 8 и коммутатора 9. При помощи регистра 8 осуществляется компенсация расхождения тактовых частот принимаемого и передаваемого через блок 5 коммутации сигналов. I з.п.ф-лы, 1 ил.

| Устройство для коммутации цифровых сигналов | 1977 |

|

SU656227A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-03-07—Публикация

1989-04-11—Подача