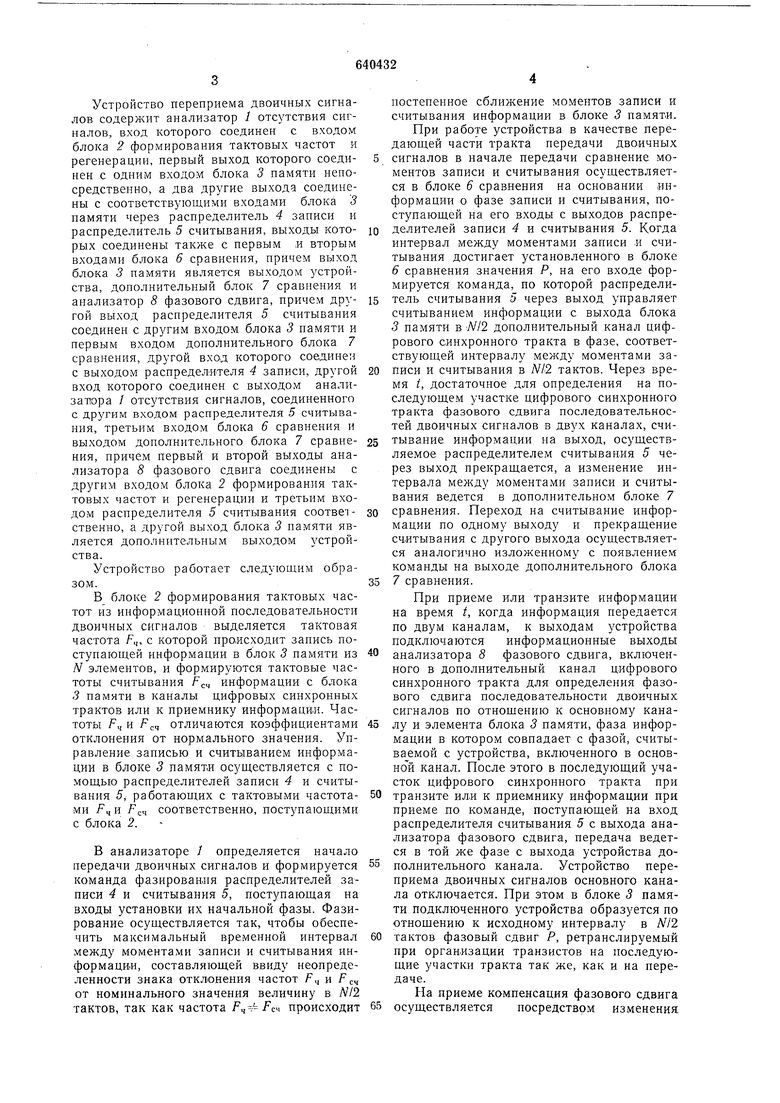

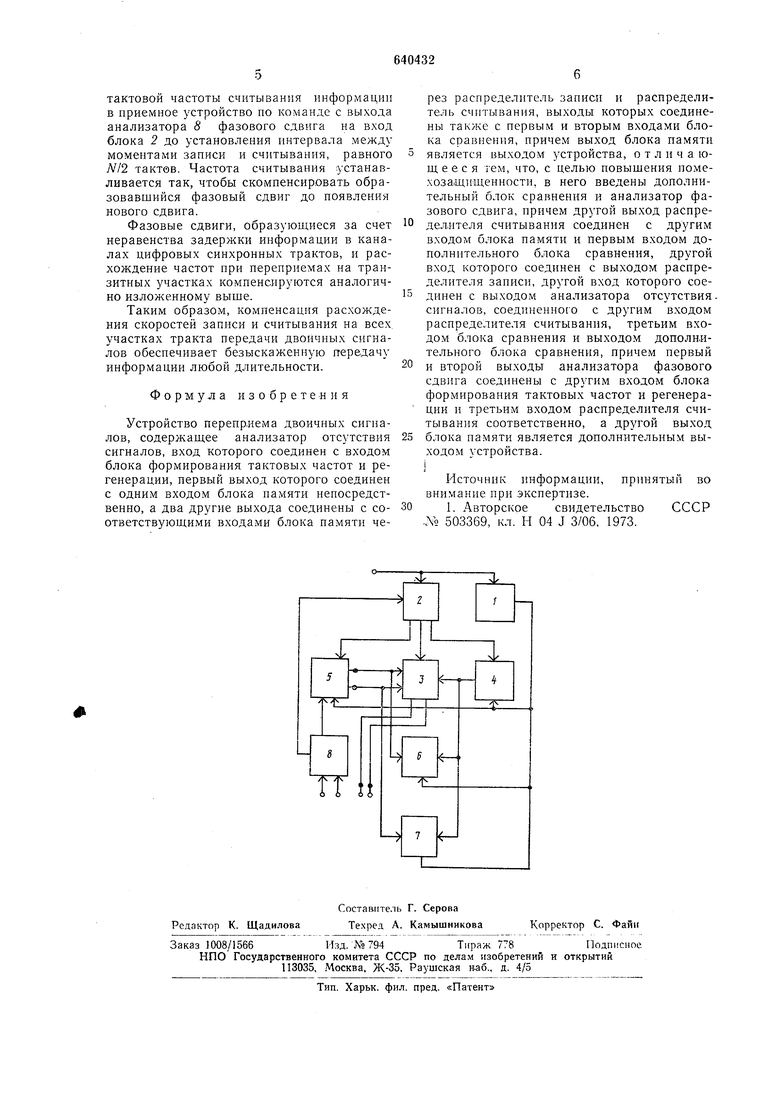

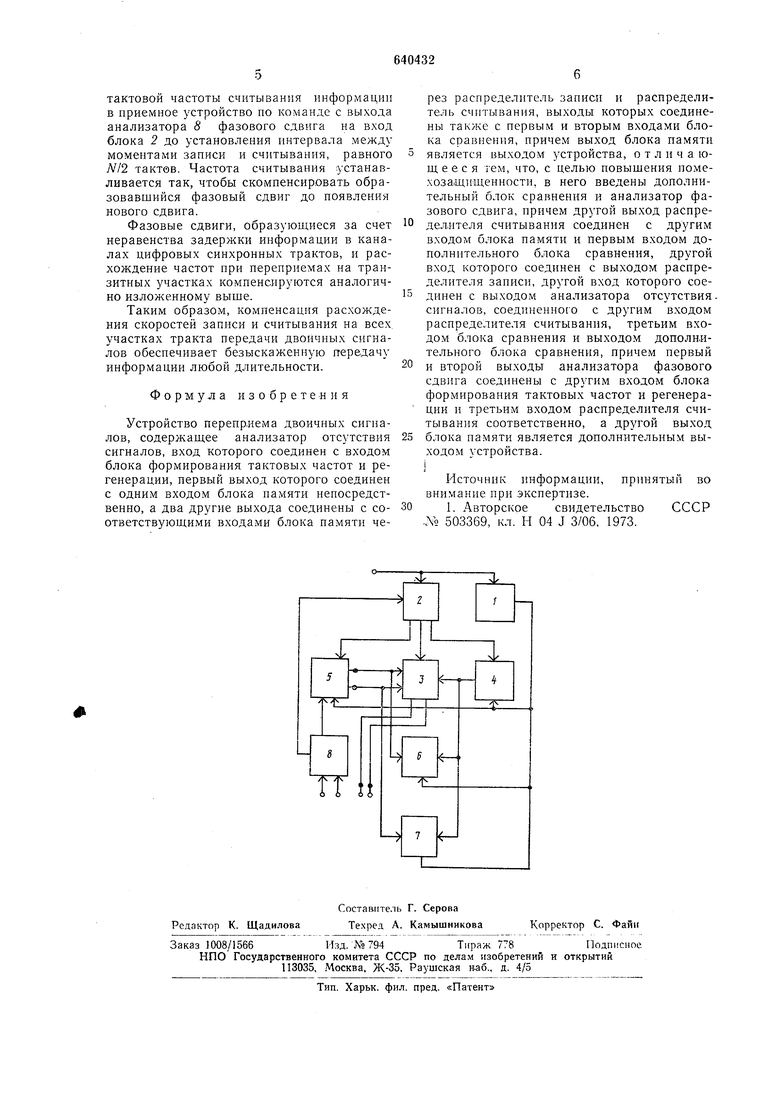

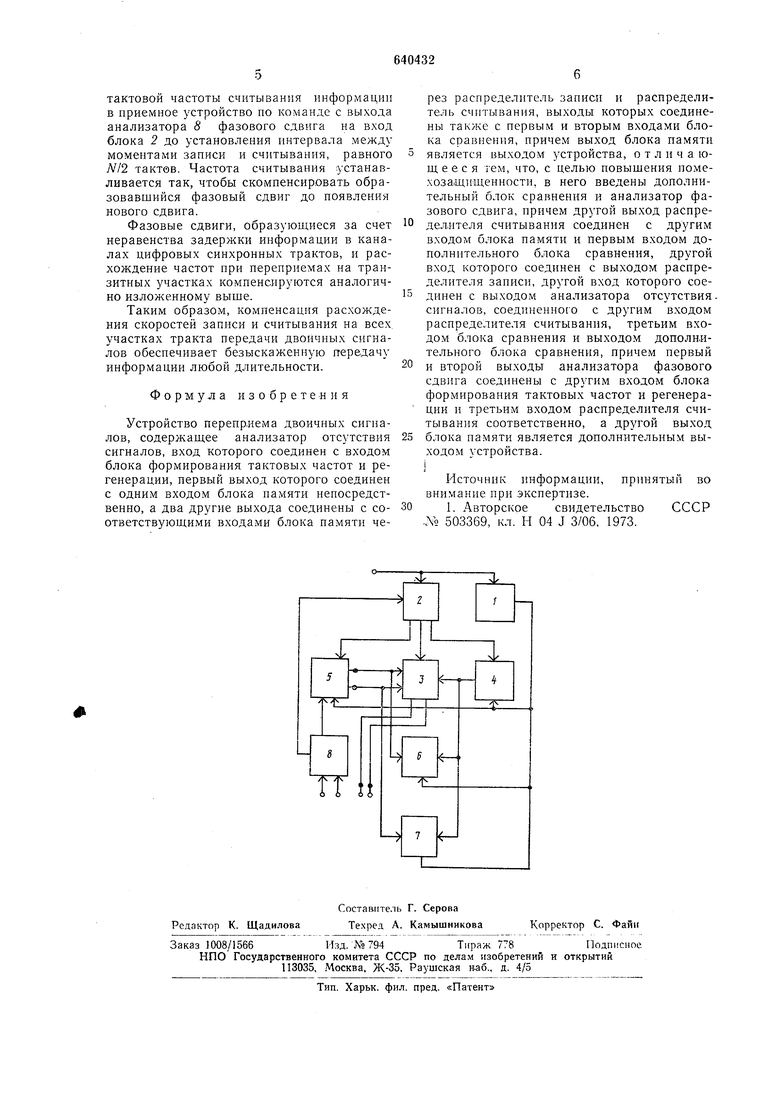

Изобретение отноеится к радиотехнике и может использоваться при конструировании устройств сопряжения каналов цифровых синхронных трактов связи с частотнонезависимыми источниками двоичной информации и между собой. Известно устройство переприема двоичных сигналов, содержащее анализатор отсутствия сигналов, вход которого соединен с входом блока формирования тактовых частот и регенерации, первый выход которого соединен с одним входом блока памяти непосредственно, а два другие выхода соединены с соответствующими входами блока памяти через распределитель записи и распределитель считывания, выходы которых соедипены также с первым и вторым входами блока сравнения, причем выход блока памяти является выходом устройства 1. Однако в известном устройстве недостаточная помехозащищенность. Цель изобретения - повыщение помехозащищенности. Для этого в устройство переприема двоичных сигналов, содержащее анализатор отсутствия сигналов, вход которого соединен с входом блока формирования тактовых частот и регенерации, первый выход которого соединен с одним входом блока памяти непосредственно, а два другие выхода соединены с соответствующим входам блока памятп через распределитель записн и распределитель считывания, выходы которых соединены также с первым и вторым входами блока сравнения, причем выход блока памяти является выходом устройства, введепы дополнительный блок сравнения и анализатор фазового сдвига, причем другой выход распределителя считывания соединен с другим входом блока памяти и первым входом дополнительного блока сравиения, другой вход которого соединен с выходом распределителя записи, другой вход которого соединен с выходом анализатора отсутствия сигналов, соединенного с другим входом распределителя считывания, третьим входом блока сравнения и выходом дополнительного блока сравнения, причем первый и второй выходы анализатора фазового сдвига соединены с другим входом блока формирования тактовых частот и регеиерацпи и третьим входом распределителя считывания соответственно, а другой выход блока памяти является дополнитель:ibi,i ;з1:1ходом устройства. -а чертеже изображена структурная элсктр1;ческая схема предлагаемого устройства.

Устройство переприема двоичных сигналов содержит анализатор / отсутствия сигналов, вход которого соединен с входом блока 2 формирования тактовых частот и регенерации, первый выход которого соедипен с одиим входом блока 3 памяти непосредственно, а два другие выхода соединены с соответствующими входами блока 3 памяти через распределитель 4 записи и распределитель 5 считывания, выходы которых соединены также с первым и вторым входами блока 6 сравнения, причем выход блока 8 памяти является выходом устройства, дополнительный блок 7 сравнения и анализатор 8 фазового сдвига, причем другой выход распределителя 5 считывания соединен с другим входом блока 3 памяти и первым входом дополнительного блока 7 сравнения, другой вход которого соединен с выходом распределителя 4 записи, другой вход которого соединен с выходом анализатюра / отсутствия сигналов, соединенного с другим входом распределителя 5 считывания, третьим входом блока 6 сравнения и выходом дополнительного блока 7 сравнения, причем первый и второй выходы анализатора 8 фазового сдвига соединены с другим входом блока 2 формирования тактовых частот и регенерации и третьим входом распределителя 5 считывания соотве1ственно, а другой выход блока 3 иамяти является дополнительным выходом устройства.

Устройство работает следующим образом.

В блоке 2 формирования тактовых частот из информационной последовательности двоичных сигналов выделяется тактовая частота /.,, с которой происходит запись постуиающей информации в блок 3 памяти из N элементов, и формируются тактовые частоты считывания F информации с блока 3 памяти в каналы цифровых синхронных трактов или к приемнику информации. Частоты F. и сч отличаются коэффициентами отклонения от нормального значения. Управление записью и считыванием информации в блоке 3 памяти осуществляется с помощью распределителей записи 4 и считывания 5, работающих с тактовыми частотами РЧ и /-(.q соответственно, поступающими с блока 2.

В анализаторе / определяется начало передачи двоичных сигналов и формируется команда фазированля распределителей записи 4 и считывания 5, поступающая на входы установки их начальной фазы. Фазирование осуществляется так, чтобы обеспечить максимальный временной интервал между моментами записи и считывания информации, составляющей ввиду неопределенности знака отклонения частот F и f сч от номинального значения величину в N12 тактов, так как частота .Feu происходит

постепенное сближение моментов записи и считывания информации в блоке 3 памяти. При работе устройства в качестве передающей части тракта передачи двоичных сигналов в начале передачи сравнение моментов записи и считывания осуществляется в блоке 6 сравнения на основании информации о фазе записи и считывания, поступающей на его входы с выходов распределителей записи 4 и считывания 5. Когда интервал между моментами записи .и считывания достигает установленного в блоке

6сравнения значения Р, на его входе формируется команда, по которой распределитель считывания 5 через выход управляет считыванием информации с выхода блока 3 памяти в М2 дополнительный канал цифрового синхронного тракта в фазе, соответствующей интервалу между моментами записи и считывания в N12. тактов. Через время /, достаточное для определения на последующе.м участке цифрового синхронного тракта фазового сдвига последовательностей двоичных сигналов в двух каналах, считывание информации на выход, осуществляемое распределителем считывания 5 через выход прекращается, а изменение интервала между моментами записи и считывания ведется в дополнительном блоке 7 сравнения. Переход на считывание информации по одному выходу и прекращение считывания с другого выхода осуществляется аналогично изложенному с появлением команды на выходе дополнительного блока

7сравнения.

При приеме или транзите информации на время /, когда информация передается по двум каналам, к выходам устройства подключаются информационные выходы анализатора 8 фазового сдвига, включенного в дополнительный канал цифрового синхронного тракта для определения фазового сдвига последовательности двоичных сигналов по отнощению к основному каналу и элемента блока 3 памяти, фаза информации в котором совпадает с фазой, считываемой с устройства, включенного в основной канал. После этого в последующий участок цифрового синхронного тракта при транзите или к приемнику информации при приеме по команде, поступающей на вход распределителя считывания 5 с выхода анализатора фазового сдвига, передача ведется в той же фазе с выхода устройства дополнительного канала. Устройство переприема двоичных сигналов основного канала отключается. При этом в блоке «3 памяти подключенного устройства образуется по отнощению к исходному интервалу в N12 тактов фазовый сдвиг Р, ретранслируемый при организации транзистов на последующие участки тракта так же, как и на передаче.

На приеме компенсация фазового сдвига осуществляется посредством изменения тактовой частоты считывания информации в приемное устройство ио команде с выхода анализатора 8 фазового сдвига на вход блока 2 до установления интервала между моментами записи и считывания, равного тактов. Частота считывания устанавливается так, чтобы скомпенсировать образовавшийся фазовый сдвиг до появления нового сдвига. Фазовые сдвиги, образующиеся за счет неравенства задержки информации в каналах цифровых синхронных трактов, и расхождение частот при иереприемах на транзитных участках комиенсируются аналогично изложенному выше. Таким образом, компенсация расхождения скоростей записи и считывания на всех участках тракта передачи двоичных сигналов обеспечивает безыскаженную передачу информации любой длительности. Формула изобретения Устройство переприема двоичных сигналов, содержащее анализатор отсутствия сигналов, вход которого соединен с входом блока формирования тактовых частот и регенерации, первый выход которого соединен с одним входом блока памяти непосредственно, а два другие выхода соединены с соответствующими входами блока памяти через распределитель записи и распределитель считывания, выходы которых соединены также с первым и вторым входами блока сравнения, причем выход блока памяти является выходом устройства, отличающееся тем, что, с целью повышения помехозащищенности, в него введены дополнительный блок сравнения н анализатор фазового сдвига, причем другой выход распределлтеля считывания соединен с другим входом блока памяти и первым входом дополнптельного блока сравнения, другой вход которого соединен с выходом распределителя записи, другой вход которого соединен с выходом анализатора отсутствиясигналов, соединенноЕО с другим входом распределителя считывания, третьим входом блока сравнения и выходом дополнительного блока сравнения, причем первый и второй выходы анализатора фазового сдвига соединены с другим входом блока формирования тактовых частот и регенерации н третьим входом распределителя считывания соответственно, а другой выход блока памяти является дополнительным выходом устройства. Источник информации, принятый во внимание при экспертизе. 1. Авторское свидетельство СССР .Vo 503369, кл. Н 04 J 3/06, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор изохронных каналов | 1978 |

|

SU725259A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Устройство для квазисинхронного ввода двоичных сигналов | 1973 |

|

SU503369A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство для асинхронного переприема | 1987 |

|

SU1513494A1 |

| Устройство для ввода двоичной информации | 1980 |

|

SU924885A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

Авторы

Даты

1978-12-30—Публикация

1977-03-23—Подача