дсржки - к входу «сброс второго триггера, выход которого подключен ко второму входу второго блока совпадения, выход которого подключен к установочному входу третьего триггера, выход первого триггера подключен через второй блок задержки ко второму входу первого блока совпадения, входы второй сборки соединены со входами фазового детектора, выходы второй и третьей сборок подключены к входам третьего блока совпадения, выход которого подключен к входу «сброс третьего триггера, через четвертую сборку - к входу «сброс первого триггера, а выход первого триггера подключен через третий блок задержки к входу четвертой сборки.;

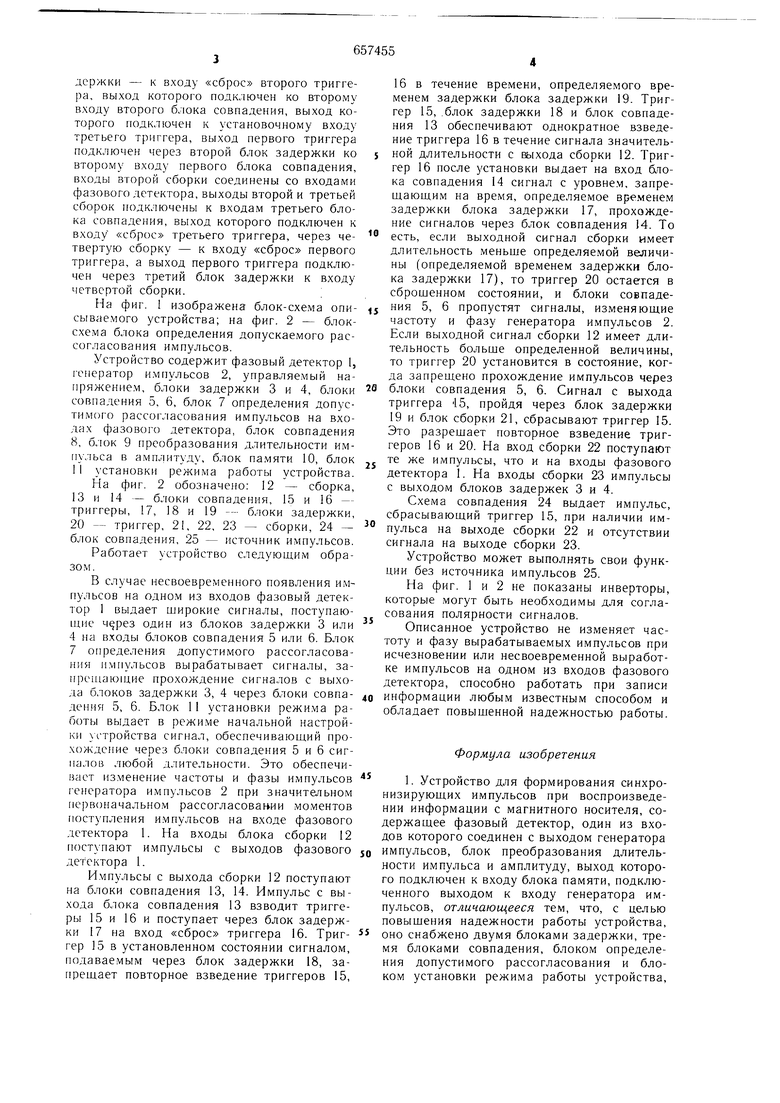

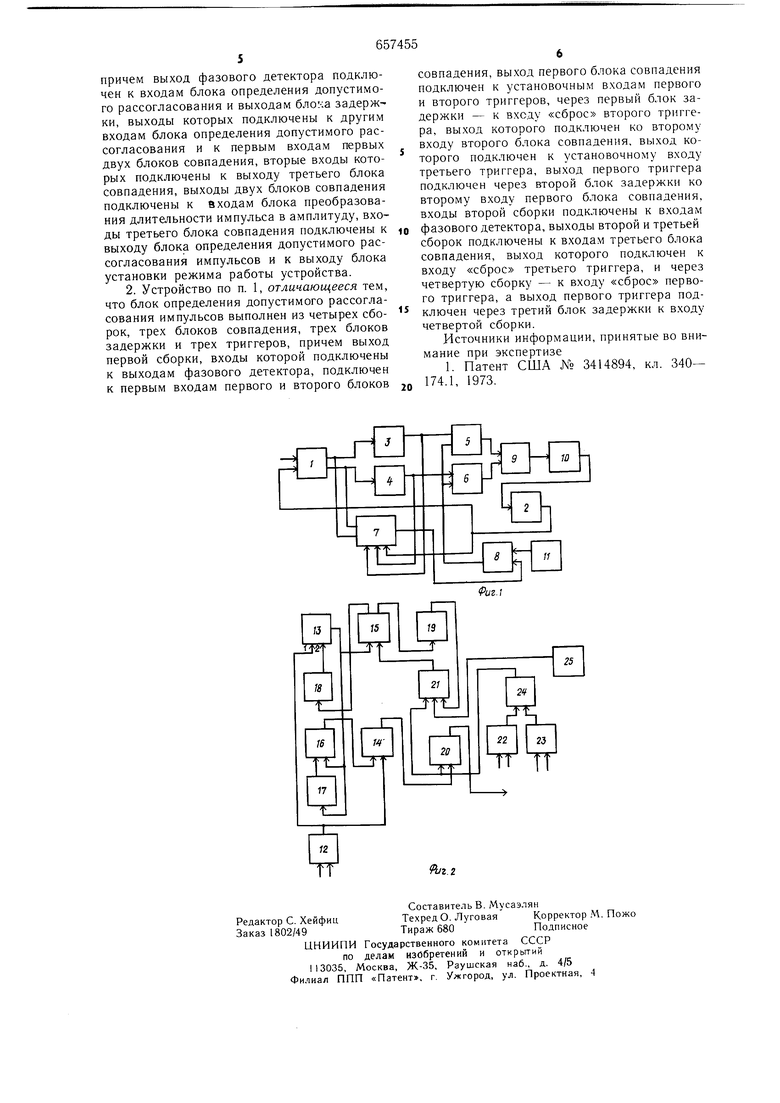

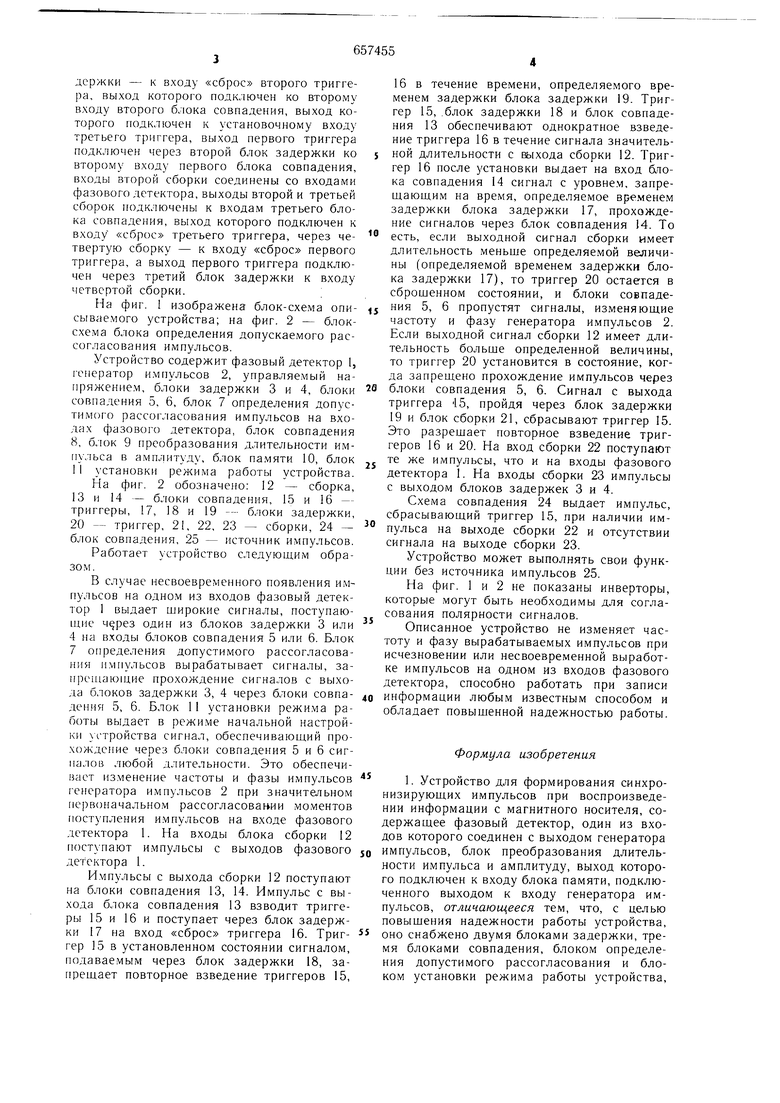

На фиг. 1 изображена блок-схема описываемого устройства; на фиг. 2 - блоксхе.ма блока определения допускаемого рассогласования импульсов.

Устройство содержит фазовый детектор 1, 1енератор импульсов 2, управляе.мый напряжением, блоки задержки 3 и 4, блоки совпадения 5, 6, блок 7 определения допустимого рассогласования импульсов на входах фазового детектора, блок совпадения 8, 6.:iOK 9 преобразования длительности импульса в амплитуду, блок па.мяти 10, блок 1 I установки режима работы устройства.

На фиг. 2 обозначено: 12 - сборка, 13 и 14 - блоки совпадения, 15 и 16 - триггеры, 17, 18 и 19 -- блоки задержки, 20 - триггер, 21, 22, 23 - сборки, 24 - блок совпадения, 25 - источник импульсов.

Работает устройство следующим образом.

В случае несвоевременного появления импульсов на одном из входов фазовый детектор 1 выдает широкие сигналы, поступаюnj.ne один из блоков задержки 3 или 4 на входы блоков совпадения 5 или 6. Блок 7 определения допустимого рассогласования импульсов вырабатывает сигналы, за11реи1аю1цие прохождение сигна.лов с выхода блоков задержки 3, 4 через блоки совпадения 5, 6. Блок 11 установки режима работы выдает в режиме начальной настройки ччтройства сигнал, обесиечиваюпдий прохождение через блоки совпадения 5 и 6 сигпалов любой длительности. Это обеспечивает изменение частоты и фазы импульсов генератора импульсов 2 при значительном первоначальном рассогласовании моментов поступления и.мпульсов на входе фазового детектора 1. На входы блока сборки 12 поступают импульсы с выходов фазового детектора 1.

Импульсы с выхода сборки 12 поступают на блоки совпадения 13, 14. Импульс с выхода блока совпадения 13 взводит триггеры 15 и 16 и поступает через блок задержки 17 на вход «сброс триггера 16. Триггер 15 в установленном состоянии сигналом, подавае.мым через блок задержки 18, запрещает повторное взведение триггеров 15,

16 в течение времени, определяемого временем задержки блока задержки 19. Триггер 15, .блок задержки 18 и блок совпадения 13 обеспечивают однократное взведение триггера 16 в течение сигнала значительной длительности с выхода сборки 12. Триггер 16 после установки выдает на вход 6jioка совпадения 14 сигнал с уровнем, запрещающим на время, определяемое временем задержки блока задержки 17, прохождение сигналов через блок совпадения 14. То есть, если выходной сигнал сборки имеет длительность меньще определяемой величины (определяемой временем задержки блока задержки 17), то триггер 20 остается в сброщенном состоянии, и блоки совпадения 5, 6 пропустят сигналы, изменяющие частоту и фазу генератора импульсов 2. Если выходной сигнал сборки 12 имеет длительность больще определенной величины, то триггер 20 установится в состояние, когда запрещено прохождение импульсов через блоки совпадения 5, 6. Сигнал с выхода триггера 15, пройдя через блок задержки 19 и блок сборки 21, сбрасывают триггер 15. Это разрещает повторное взведение триггеров 16 и 20. На вход сборки 22 поступают те же импульсы, что и на входы фазового детектора 1. На входы сборки 23 импульсы с выходом блоков задержек 3 и 4.

Схема совпадения 24 выдает импульс, сбрасывающий триггер 15, при наличии импульса на выходе сборки 22 и отсутствии сигнала на выходе сборки 23.

Устройство может выполнять свои функции без источника импульсов 25.

На фиг. 1 и 2 не показаны инверторы, которые могут быть необходимы для согласования полярности сигналов.

Описанное устройство не изменяет частоту и фазу вырабатываемых импульсов при исчезновении или несвоевременной выработке импульсов на одном из входов фазового детектора, способно работать при записи информации любым известным способом и обладает повыщенной надежностью работы.

Формула изобретения

1. Устройство для формирования синхронизирующих импульсов при воспроизведении информации с магнитного носителя, содержащее фазовый детектор, один из входов которого соединен с выходом генератора импульсов, блок преобразования длительности импульса и амплитуду, выход которого подключен к входу блока памяти, подключенного выходом к входу генератора импульсов, отличающееся тем, что, с целью повыщения надежности работы устройства, оно снабжено двумя блоками задержки, тремя блоками совпадения, блоком определения допустимого рассогласования и блоком установки режима работы устройства.

причем выход фазового детектора подключен к входам блока определения допустимого рассогласования и выходам блока задержки, выходы которых подключены к другим входам блока определения допустимого рассогласования и к первым входам первых двух блоков совпадения, вторые входы которых подключены к выходу третьего блока совпадения, выходы двух блоков совпадения подключены к входам блока преобразования длительности импульса в амплитуду, входы третьего блока совпадения подключены к выходу блока определения допустимого рассогласования импульсов и к выходу блока установки режима работы устройства.

2. Устройство по п. 1, отличающееся тем, что блок определения допустимого рассогласования импульсов выполнен из четырех сборок, трех блоков совпадения, трех блоков задержки и трех триггеров, причем выход первой сборки, входы которой подключены к выходам фазового детектора, подключен к первым входам первого и второго блоков

совпадения, выход первого блока совпадения подключен к установочным входам первого и второго триггеров, через первый блок задержки - к входу «сброс второго триггера, выход которого подключен ко второму входу второго блока совпадения, выход которого подключен к установочному входу третьего триггера, выход первого триггера подключен через второй блок задержки ко второму входу первого блока совпадения, входы второй сборки подключены к входам фазового детектора, выходы второй и третьей сборок подключены к входам третьего блока совпадения, выход которого подключен к входу «сброс третьего триггера, и через четвертую сборку - к входу «сброс первого триггера, а выход первого триггера подключен через третий блок задержки к входу четвертой сборки.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3414894, кл. 340- 174.1, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый компаратор | 1981 |

|

SU983978A1 |

| Устройство для синхронизации записываемой на магнитный носитель информации | 1977 |

|

SU649032A1 |

| Устройство воспроизведения сигналов цифровой информации с магнитного носителя | 1983 |

|

SU1099324A1 |

| Устройство фазовой автоподстройки | 1983 |

|

SU1185602A1 |

| Устройство выделения информации | 1977 |

|

SU656100A1 |

| Частотно-фазовый компаратор | 1989 |

|

SU1688382A1 |

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

| Устройство для декодирования сигнала воспроизведения магнитной записи | 1985 |

|

SU1304071A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU919124A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

Авторы

Даты

1979-04-15—Публикация

1976-03-24—Подача