Изобретение относится к радиотехнике и может быть использовано в цифровы) синтезаторах частоты, применяемых в радиолокации и радиосвязи.

Известны цифровые перестраиваемые делители частоты с симметрированным выходным сигналом 1,2.

Первое из известных устройств содержит двоичный счетчик, выполненный на триггерах со счетным входом (счетных триггерах), основной и вспомогательный элементы сравнения, подключенные к выходам двоичного счетчика и к шинам управления, выход вспомогательного элемента сравнения подключен к первому, выходу статического триггера, а выход основного, элемента сравнения - ко второму входу статического триггера и к шине сброса (установки нуля) двоичного счетчика 1.

К недостаткам данного устройства от-, носятся: низкое быстродействие, связанное с тем, что первый разряд счетчика при срабатывании основного элемента сравнения претерпевает двойное переключение за один период частоты счета (по и.мпульсу счета и по сигналу сброса), а также получение

асимметричного выходного сигнала при нечетных коэффициентах деления.

Второе из известных устройств содержит разрядный двоичный счетчик, элементы сравнения, одни входы которых подключены к шипе управления, а выход первого из них - к единичному входу триггера и инверторы, вход первого из которых подключен к шине управления 2.

Этот делитель также имеет низкое быстродействие, но его выходной сигнал симметричен при любом коэффициенте деления. . Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в перестраиваемый делитель частоты, содержаший разрядный двоичный счетчик, элементы сравнения, триггер и инверторы, введены элементы И-ИЛИ, элементы И, элемент ИЛИ и формирователь синхроимпульсов, вход которого соединен с входной шиной, первый выход - непосредственно с одним из входов синхронизации разрядного двоичного счетчика, а второй выход - через первый элемент И со вторым входом синхронизации и через второй элемент И со

входом установки разрядного двоичного счетчика, разрядные выходы которого подключены к информационным входам элементов И-ИЛИ, управляющие входы которых соединены с быходом первого инвертора, а выходы - с другими входами первого элемента сравнения, при этом другие входы второго элемента сравнения подключены к разрядным выходам разрядного двоичного счетчика, выход - к первому входу элемента ИЛИ, к нулевому входу триггера, через второй элемент НЕ ко входу первого элемента И и непосредственно ко входу второго элемента И, а второй вход элемента ИЛИ соединен с выходом первого элемента сравнения, а также тем, что разрядный двоичный счетчик содержит информационный и буферный регистры и сумматор, информационные входы которого подключены к (п-1)-ым выходам старших разрядов буферного регистра, управляющий вход - к единичному выходу первого разряда буферного регистра, нулевой вход которого соединен с D-в-ходом первого разряда информационного регистра, D-входы (п - 1)-ых старЩих разрядов которого соединены с выходами сум Матора, а разрядные входы - с D-входами буферного регистра.

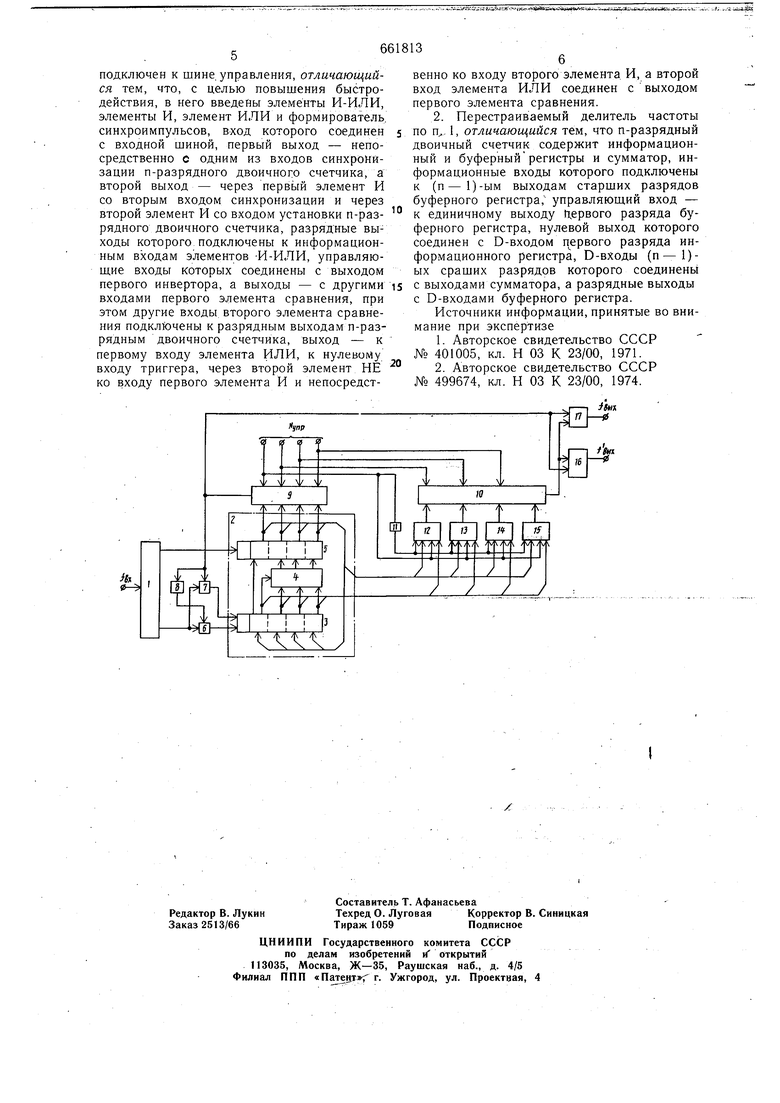

На чертеже представлена структурная электрическая схема перестраиваемого де;уШтеЛЯ ЧаСТОТЫг --;- ----- ....-;г,.. - : i .

Устройство содержит 1 - формирователь синхросигналов, 2 - п-разрядный двоичный счетчик, 3 - буферный D-регистр, 4: /- сумматор, 5 - информационный D-регистр, 6, 7 - элементы И, 8 - инвертор, 9, 10 - элементы сравнения, 11 -инвертор,12 - 15 - элементы И-ИЛИ, 16 - триггер, 17 - элемент ИЛИ.

Перестраиваемый делитель частоты работает следующим образом.

Частота поступает на формирователь синхросигналов 1, на первом выходе которого формируется импульсная последовательность с частотой и фазой равными частоте и фазе входного сигнала fg, а на втором выходе - импульсная последовательность с частотой fgx, отстоящая по фазе на 180° от входного сигнала (сдвинутая на величину -). В зависимости от формы входного сигнала, конкретная реализация формирователя I может быть различной.

В исходном состоянии на выходе элемента сравнения 9 присутствует «нулевой потенциал, запрещающий прохождение через элемент И 7 сийхросерии на вход установки «нуля буферного регистра 3 счетчика 2 и через инвертор 8 разрешающий прохождение сигнала через элемент И 6 на вход синхронизации буферного регистра 3.

С поступлением каждого импульса содержимое информационного регистра 5 переписывается в буферный регистр 3, при этом на выходах сумматора 4 фЬрМйруётй;я Ч:ИСлр,

равное сумме содержимого (л- 1) старщих разрядовбуферного регистра 3 и содержимого первого разряда буферного регистра 3 (вес разряда - 2° 1).

5 При достижении содержимым информационного регристра 5 величины, равной Nynp , срабатывает элемент сравнения 9 и «единичный сигнал с его выхода устанавливает триггер 16 в «нулевое состояние, открывает элемент И 7 и запирает через инвертор 8

0 элемент И 6. Следующий импульс, пройдя через элемент И 7, «обнулит (сбросит в состояние «О) буферный регистр 3, и начнется новый цикл счета, при этом в информационном регистре 5 установится состояние «10....О, а на выходе элемента сравнения 9 сформируется «нулевой потенциал и цикл работы делителя повторится до следующего сравнения. Таким образом, на выходе элемента сравнения 9 сигналы будут появляться с частотой, равной fix/Nynp, с этой частотой

0 будет происходить сброс триггера 16, установка которого в «единицу осуществляется сигналом с выхода элемента сравнения 10. Процесс симметрирования выходного сигнала триггера 16 осуществляется с помощью элемента сравнения 10 следующим об5 разом.

На входы элемента сравнения 10 сигнал N упр подается сдвинутым на один разряд в сторбну младщих ( Ыу„р/2). Вторые входы элемента сравнения 10 подключаются через

0 элементы И-,ИЛИ 12-15 к выходам либо буферного 3, либо информационного 5 регистров в зависимости от значения первого разряда Nynfi. При нечетном коэффициенте деления (1-ый разряд Nanf)«b) элемент

5 сравнения 10 подключается к выходам буферного регистра 3, при четном коэффициенте деления (1-ый разряд «О) - к выходам информационного регистра 5. Таким образом, при любых значениях Nynp выходной сигнал на выходе триггера 16 будет представлять собой «меандр с дли.тельностямИ импульса и паузы точно равными Tix-Nynf,/2 и частотой равной fgx/NifnjbЕсли же выходные сигналы элементов сравнения 9 и 10 собрать на,элементе ИЛИ 17, то на его выходе получится последовательность импульсов с частотой, равной 2fgj,/Nyn)jH длительностью t Т,,, то есть результат деления дробный коэффициент Nynp/2, кратный0,5.

0

Формула изобретения

1. Перестраиваемый делитель частоты,

содержащий п-разрядный двоичный счетчик,

элементы сравнения, одни входы которых

подключеньг к щине управления, а выход

первого из них - к единичному входу триг тера, и ийГЁёрторы, вход первого из которых подключен к шине, управления, отличающийся тем, что, с целью повышения быстродействия, в него введены элементы И-ИЛИ, элементы И, элемент ИЛИ и формирователь, синхроимпульсов, вход которого соединен с входной шиной, первый выход - непосредственно с одним из входов синхронизации п-разрядного двоичного счетчика, а второй выход - через первый элемент И со вторым входом синхронизации и через второй элемент И со входом установки п-разрядного двоичного счетчика, разрядные выходы которого подключены к информационным входам элементов -И-ИЛИ, управляющие входы которых соединены с выходом первого инвертора, а выходы - с другими входами первого элемента сравнения, при этом другие входы, второго элемента сравнения подключены к разрядным выходам п-разрядным двоичного счетчика, выход - к первому входу элемента ИЛИ, к нулевому входу триггера, через второй элемент НЕ ко входу первого элемента И и непосредст661813венно ко входу второго элемента И, а второй вход элемента ИЛИ соединен с выходом первого элемента сравнения. 2. Перестраиваемый делитель частоты по п, 1, отличающийся тем, что п-разрядный двоичный счетчик содержит информационный и буферныйрегистры и сумматор, информационные входы которого подключены к (п-1)-ым выходам старших разрядов буферного регистра, управляюший вход - к единичному выходу (хервого разряда буферного регистра, нулевой выход которого соединен с D-входом первого разряда информационного регистра, D-вХоды (п-1)ых сраших разрядов которого соединены с выходами сумматора, а разрядные выходы с D-входами буферного регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 401005, кл. Н 03 К 23/00, 1971. 2.Авторское свидетельство СССР № 499674, кл. Н 03 К 23/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Делитель с переменным коэффициентом деления | 1975 |

|

SU520689A1 |

| Перестраиваемый делитель частоты | 1977 |

|

SU678672A1 |

| Перестраиваемый делитель частоты следования импульсов | 1978 |

|

SU777824A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Частотный компаратор | 1983 |

|

SU1167719A2 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Авторы

Даты

1979-05-05—Публикация

1977-03-28—Подача