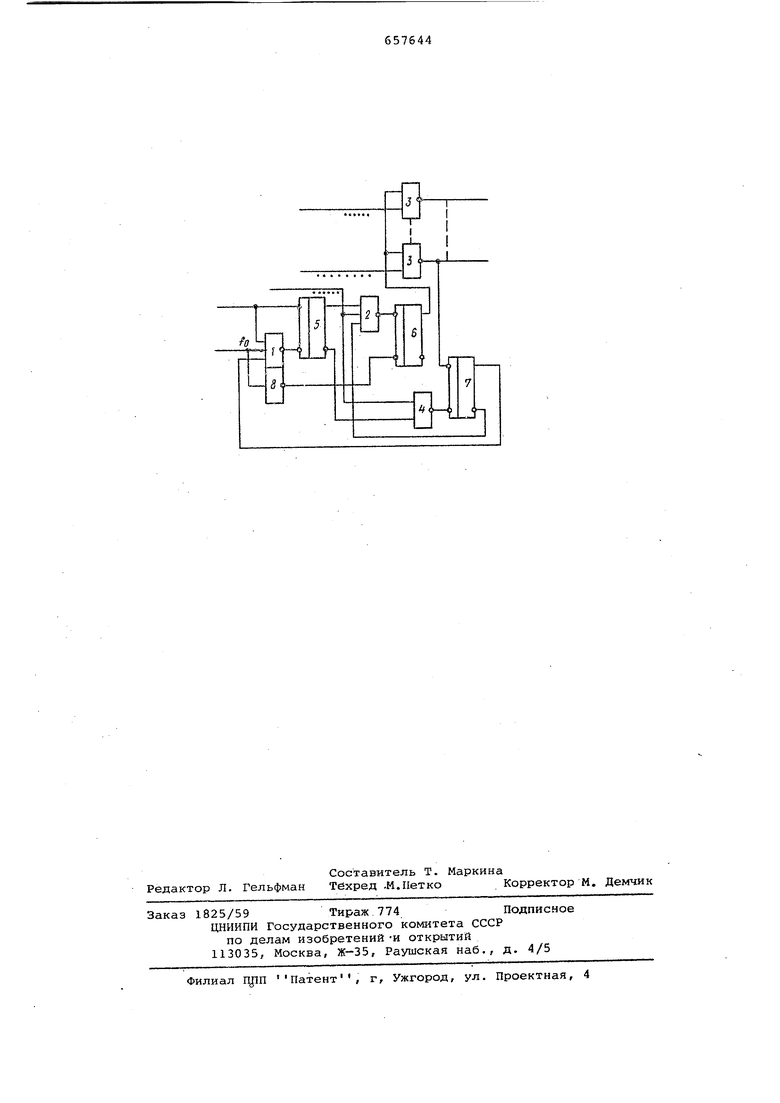

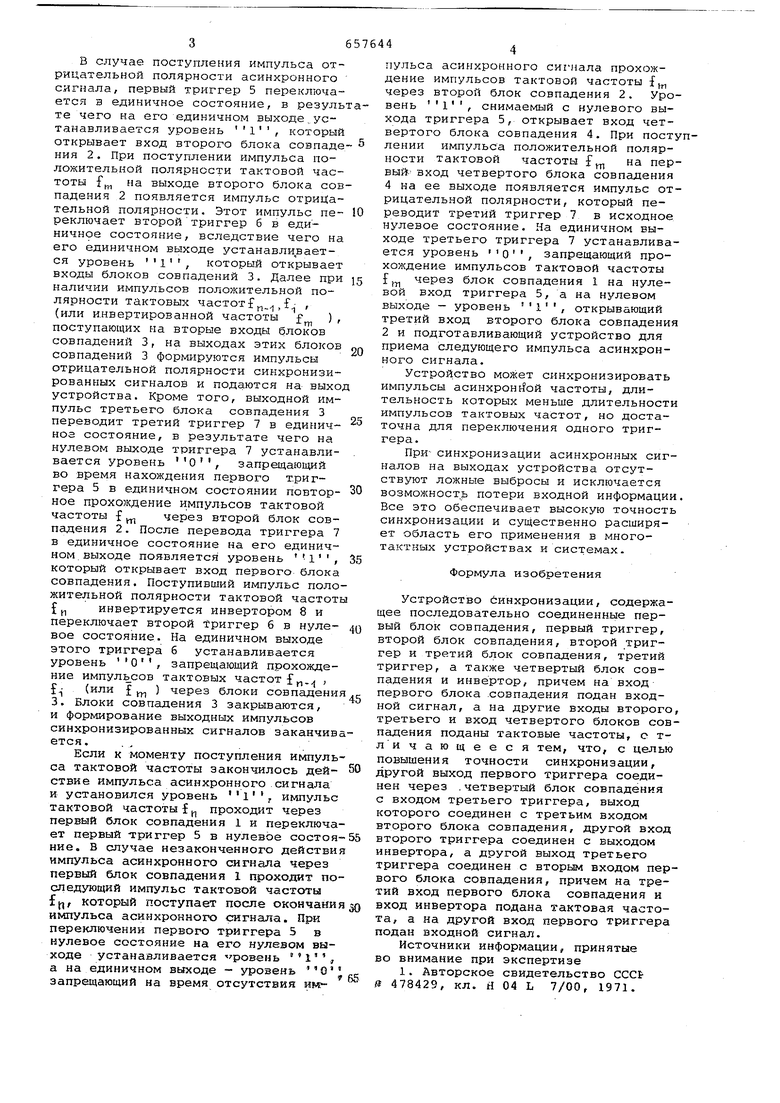

Изобретение относится ктехнике связи и может использоваться в многотактных устройствах и системах для согласования асинхронных сигналов с импульсами тактовых частот. Известно устройство синхронизации содержащее последовательно соединенные первый блок совпадения, первый триггер, второй блок совпадения, второй триггер и третий блок совпа: дения, третий триггер, четвертый бло совпадения и инвертор, причем на вход.первого блока совпадения подан входной сигнал, а на другие входы второго, третьего и четвертого блоко совпадения поданы тактовые частоты 1. . Однако данное устройство имеет не высокую точность синхронизации. Цель изобретения - повышение точности синхронизации. Для этого в устройство синхрониза ции, содержащее последовательно соединенные первый блок совпадения, пер вый триггер, второй блок совпадения, второй триггер и третий блок совпаде ния, третий триггер, а также четвертый блок совпадения и инвертор, причем на вход первого блока совпадени подан входной сигнал, а на другие ,входы второго, третьего и вход четвертого блоков совпадения поданы тактовые частоты, другой выход первого триггера соединен через четвертый блок совпадения с входом третьего триггера, выход которого соединен с третьим входом второго блока совпадения, другой вход второго триггера соединен с выходом инвертора, а другой выход третьего триггера соединен с вторым входом первого блока совпадения, причем на третий вход первого блока совпадения и вход инвертора подана тактовая частота, а на другой вход первого триггера подан входной сигнал. На чертеже изображена структурная электрическаяUсхема предложенного устройства. Устройство синхронизации содержит блоки совпадения 1,2, 3, 4, триггеры 5, 6, 7 и инвертор 8. Предложенное устройство работает следующим образом. Вначале триггеры 5, 6, 7 находятся в нулевых состояниях, т.е. единичные выходы триггеров 5, 6, 7 имеют низкие уровни (потенциалы) , а нулевые - высокие уровни . В случае поступления импульса отрицательной полярности асинхронного сигнала, первый триггер 5 переключается 3 единичное состояние, в резуль те чего на его единичном выходе,ускоторыйтанавливается уровень открывает вход второго блока совпаде НИН 2. При поступлении импульса положительной полярности тактовой частоты f на выходе второго блока сов падения 2 появляется импульс отрицательной полярности. Этот импульс переключает второй триггер 6 в единичн9е состояние, вследствие чего на его единичном выходе устанавли вается уровень , который открывает входы блоков совпадений 3. Далее при наличии импульсов положительной полярности тактовых частот f , , (или инвертированной частоты f ), поступающих на вторые входы блоков совпадений 3, на выходах этих блоков совпадений 3 формируются импульсы отрицательной полярности синкронизированных сигналов и подаются на выхо устройства. Кроме того, выходной импульс третьего блока совпадения 3 переводит третий триггер 7 в единичноз состояние, в результате чего на нулевом выходе триггера 7 устанавлизапрещающийвается уровень во время нахождения первого триггера 5 в единичном состоянии повторнов прохождение импульсов тактовой частоты f j через второй блок совпадения 2. После перевода триггера 7 в единичное состояние на его единичном, выходе появляется уровень , который открывает вход первого блока совпадения. Поступивший импульс поло жительной полярности тактовой частот инвертируется инвертором 8 и переключает второй триггер 6 в нулевое состояние. На единичном выходе этого триггера б устанавливается уровень О , запрещающий прохождение импуль сов тактовых частот f f,. (или f ) через блоки совпадени 3. Блоки совпадения 3 закрываются, и формирование выходных импульсов синхронизированных сигналов заканчив ется ... Если к моменту поступления импуль са тактовой частоты закончилось действие импульса асинхронного сигнала и установился уровень ,, импульс тактовой частоты f проходит через первый блок совпадения 1 и переключа ет первый триггер 5 в нулевое состоя ние. В случае незаконченного действи импульса асинхронного сигнала через первый блок совпадения 1 проходит по следующий импульс тактовой частоты который поступает после окончани импульса асинхронного сигнала. При переключении первого триггера 5 в нулевое состояние на его нулевом выходе устанавливается ровень а на единичном выходе - уровень запрещающий на время отсутствия импульса асинхронного сиг-нала прохождение импульсов тактовой частоты через второй блок совпадения 2. Уровень , снимаемый с нулевого выхода триггера 5, открывает вход четвертого блока совпадения 4. При поступлении импульса положительной полярности тактовой частоты f на первый вход четвертого блока совпадения 4 на ее выходе появляется импульс отрицательной полярности, который переводит третий триггер 7 в исходное нулевое состояние. На единичном выходе третьего триггера 7 устанавливается уровень О, запрещающий прохождение импульсов тактовой частоты ff через блок совпадения 1 на нулевой вход триггера 5, а на нулевом выходе - уровень , открывающий третий вход второго блока совпадения 2 и подготавливающий устройство для приема следующего импульса асинхронного сигнала. Устройство может синхронизировать импульсы асинхронЕ ой частоты, длительность которых меньше длительности импульсов тактовых частот, но достаточна для переключения одного триггера. При- синхронизации асинхронных сигналов на выходах устройства отсутствуют ложные выбросы и исключается возмол(ност,ь потери входной информации. Все это обеспечивает высокую точность синхронизации и существенно расширяет область его применения в многотактных устройствах и системах. Формула изобретения Устройство синхронизации, содержащее последовательно соединенные первый блок совпадения, первый триггер, второй блок совпадения, второй триггер и третий блок совпадения, третий триггер, а также четвертый блок совпадения и инвертор, причем на вход первого блока .совпадения подан входной сигнал, а на другие входы второго, третьего и вход четвертого блоков совпадения поданы тактовые частоты, с тличающееся тем, что, с целью повышения точности синхронизации, другой выход первого триггера соединен через .четвертый блок совпадения с входом третьего триггера, выход которого соединен с третьим входом второго блока совпадения, другой вход второго триггера соединен с выходом инвертора, а другой выход третьего триггера соединен с вторым входом первого блока совпадения, причем на третий вход первого блока совпадения и вход инвертора подана тактовая частота, а на другой вход первого триггера подан входной сигнал. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССВ № 478429, кл. Н 04 L 7/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1982 |

|

SU1075392A1 |

| Устройство синхронизации | 1971 |

|

SU478429A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| ОХРАННОЕ КОДОВОЕ УСТРОЙСТВО | 1990 |

|

SU1834548A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU739721A1 |

| Устройство для многоуровневой кодоимпульсной модуляции | 1975 |

|

SU559416A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

Авторы

Даты

1979-04-15—Публикация

1977-07-26—Подача