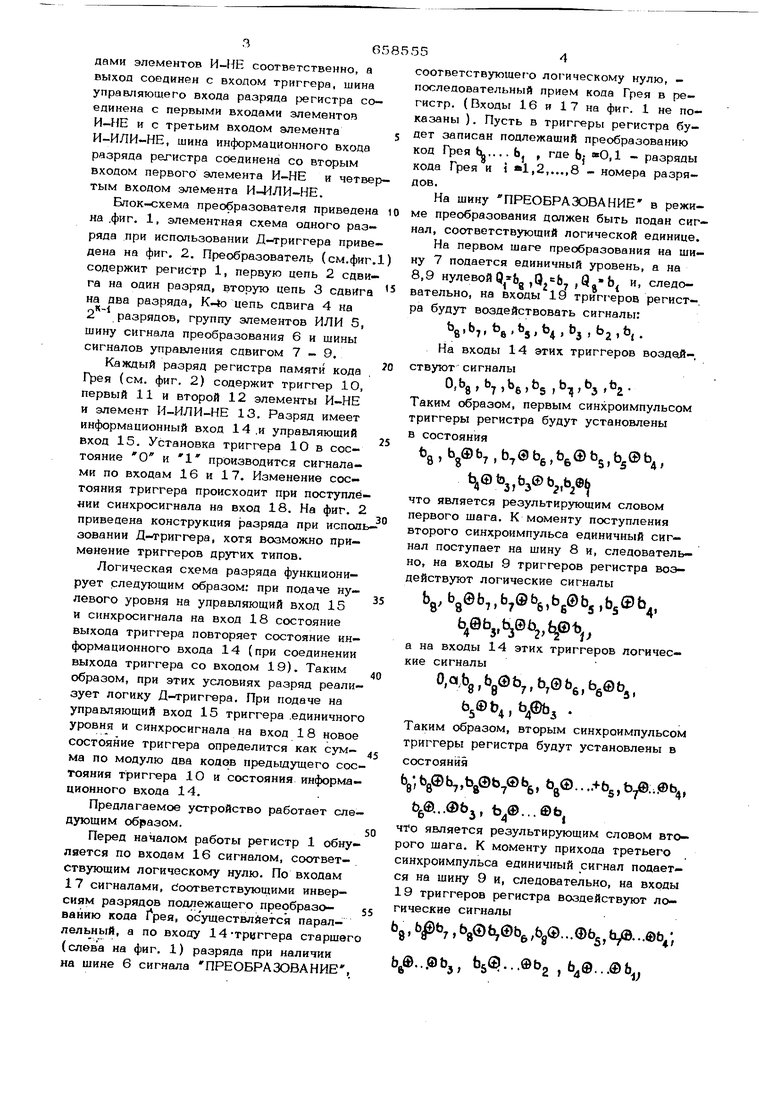

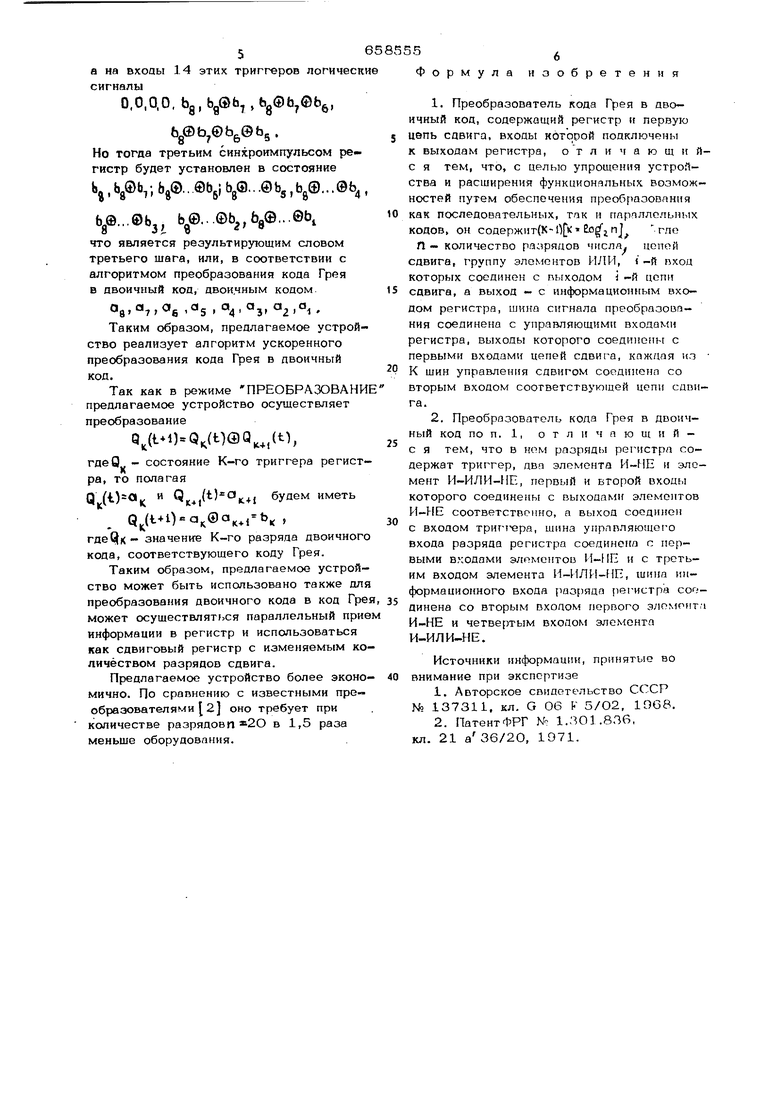

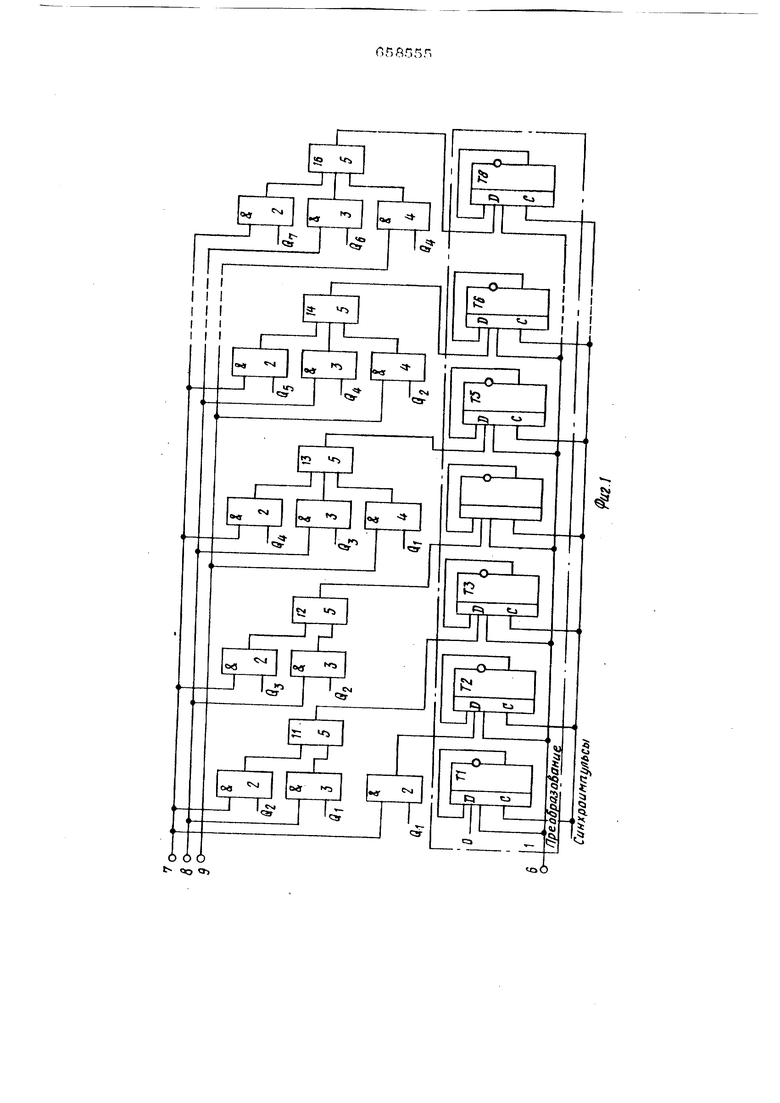

Изобретение относится к области цифровой вычислительной техники и может быть использовано в вычислительных и телеметрических системах. Известен преобразователь кода Грея в двоичный код, содержащий сдвиговый регистр, полусумматор и элемент И i. Недостатком данного устройства является низкая скорость преобразования, связанна с последовательным принципом работы. Ближайшим техническим решением дан ной задачи является преобразователь , содержащий регистр и первую цепь сдвига, входы которой подключены к выходам регистра 2. Недостатком известного устройства является относительно большой объем аппаратуры, связанный с необходимостью использования регистра двоичного кода и большо о количест ва полусумматоров и ограниченность функциональных возмож ностей, вследствие того, что регистр нел зя использовать для других целей. Целью изобретения является упрощение устройства и расширение его функциональных возможностей путем обоспечсиня параллельного и последовател1..ного приема информации в регистр функций преобразования. Эта цель достигается тем, что предлагаемое устройство содержит ( гае Л- количество разрядов числа цепей сдвига, группу элементов ИЛИ, i - ты-й вход которых соединен с выходом i - той цепи сдвига, a выход - с информационным входом регистра, шина сигнала преобразования соединена с управляющими входами регистра, выходы которого соединены с первыми входами цепей сдвига, каждая из К шин управления сдвигом соединена со вторым входом соответствующей цепи сдвига. Другое отличие предложенного устройства состоит в том, что в пем разряды регистра содержат триггер, два элемента И-НЕ и элемент И-МЛИ-ИВ, первый и второй входы которого соединены с выхо 6дами элементов И-НЕ соответственно, а выход соединен с входом триггера, шина управляющего входа разряда регистра соединена с первыми входами элементов И-НЕ и с третьим входом элемента И-ИЛИ НЕ, шина информационного входа разряда регистра соединена со вторым входом первого элемента И-НЕ и четвер тым входом элемента ИЛЛИ-НЕ. Блок-схема преобразователя приведена на .фиг. 1, элементная схема одного разряда при использовании Д-триггера приве дена на фиг. 2. Преобразователь (см.фиг. содержит регистр 1, первую цепь 2 сдвига на один разряд, вторую цепь 3 сдвига на два разряда, цепь сдвига 4 на 2 разрядов, группу элементов ИЛИ 5, шину сигнала преобразования 6 и шины сигналов управления сдвигом 7-9. Каяшый разряд регистра памяти кода , Грея (см. фиг. 2) содержит триггер 1О, первый 11 и второй 12 элементы И-НЕ и элемент И-ИЛИ-НЕ 13. Разряд имеет информационный вход 14 .и управляющий вход 15. Установка триггера 10 в состояние О и производится сигналами по входам 16 и 17. Изменение состояния триггера происходит при поступлении синхросигнала на вход 18. На фиг. 2 привецена конструкция разряда при испопь зовании Д- риггера, хотя возможно применение триггеров других типов. Логическая схема разряда функционирует следующим образом: при подаче нулевого уровня на управляющий вход 15 и синхросигнала на вход 18 состояние выхода триггера повторяет состояние информационного входа 14 (при соединении выхода триггера со входом 19). Таким образом, при этих условиях разряд реализует логику Д-триггера. При подаче на управляющий вход 15 триггера .единичного уровн я и синхросигнала на вход 18 новое состояние триггера определится как сум- ма по модулю два кодов предыдущего состояния триггера 1О и состояния информационного входа 14. Предлагаемое устройство работает следующим образом. Перед началом работы регистр 1 обнуляется по входам 16 сигналом, соответствующим логическому нулю. По входам 17 сигналами, Соответствующими инверсиям разрядов подлежащего преобразованию кода , осуществлйется параллельный, а по входу 14-триггера старшег (слева на фиг. 1) разряда при наличии на шине 6 сигнала ПРЕОБРАЗОВАНИЕ, соответствующего логическому нулю, - последовательный прием кода Грея в регистр. (Входы 16 и 17 на фиг. 1 не показаны ). Пусть в триггеры регистра будет записан подлежащий преобразованию код Грея h..... Ь, f где Ь.- 0,1 - разряды кода Грея и i «1,2,...,8 - номера разряов. На шину ПРЕОБРАЗОВАНИЕ в режиме преобразования должен быть подан сигнал, соответствующий логической единице. На первом шаге преобразования на шину 7 подается единичный уровень, а на 8,9 иулевойО Ьд , , и, следовательно, на входы 19 триггеров регист-, ра будут воздействовать сигналы: в S 4 З входы 14 этих триггеров воздай-, ствуют сигналы 0,Ь8,Ь,Ьб,Ьд,Ь,Ь,Ь2. Таким образом, первым синхроимпульсом триггеры регистра будут установлены в состояния feg,bg®b,,b,0bg,bg®b5,b5®b, 4®,з®ь„ь,© что является результирующим словом первого шага. К моменту поступления второго синхроимпульса единичный сигнал поступает на шину 8 и, следовательно, на входы 9 триггеров регистра воздействуют логические сигналы D,®b,,bg0b5,b5®b, а на входы 14 этих триггеров логические сигналы 0,a.bg,6g®b,,b,0bg,bg0b, Ь5®Ь4, . Таким образом, вторым синхроимпульсом триггеры регистра будут установлены в состояния bg;bg®b,,, bg®....+b5,b7®...®b4, bg®...®bj, ...©bj что является результирующим словом второго шага. К моменту прихода третьего синхроимпульса единичный сигнал подается на шину 9 и, следовательно, на входы 19 триггеров регистра воздействуют логические сигналы 8 7 9® ® & д®--® &,Ьт®--©Ь ; Ь,®...®Ьз, Ь5...®Ь2 ,Ь4©...®Ь, а на входы 14 этих триггеров логическ сигналы 0.0.0,0, ba,bgffib,,bg®b,©b, 6g®b,. Но тогда третьим синхроимпульсом регистр будет установлен в состояние S.b8®b,;bj®...®b,ibgQ...®b.,,bg®...©b, ь„ь,®... bg®..,©b,. что является результирующим словом третьего шага, или, в соответствии с алгоритмом преобразования кода Грея в двоичный код, двоичным кодом. °3. а2°1 Таким образом, предлагаемое устрой ство реализует алгоритм ускоренного преобразования кода Грея в пвоичный код. Так как в режиме ПРЕОБРАЗОВАНИ предлагаемое устройство осуществляет преобразование QJbi)Q(t)@Q,(t), гдеО - состояние К-го триггера регист ра, то полагая Q ( будем иметь Qj,() , b гдеС|к - значение К-го разряда двоичног кода, соответствующего коду Грея. Таким образом, предлагаемое устрой ство может быть использовано также дл преобразования двоичного кода в код Гре может осуществляться параллельный при информации в регистр и использоваться как сдвиговый регистр с изменяемым ко личеством разрядов сдвига. Предлагаемое устройство более эконо мично. По сравнению с известными преобразователями 2 оно требует при количестве разрядов п 2О в 1,5 раза меньше оборудования. Формула изобретения 1.Преобразователь кода Грея в двоичный код, содержащий регистр и первую цепь сдвига, входы которой подключены к выходам регистра, отличающийс я тем, что, с целью упрощения устройства и расширения функциональных возможностей путем обеспечения преобразования как последовательных, так и ппрпллсльных кодов, он содержит( EflgfjnJ гпе Л - количество разрядов числя, цепей сдвига, группу элементов ИЛИ, i -и вход которых соединен с выходом i -и цепи сдвига, а выход - с информационным входом регистра, шина сигнала преобразования соединена с управляющими входами регистра, выходы которого соединены с первыми входами цепей сдвига, каждая из К шин управления сдвигом соединено со вторым входом соответствующей цепи сдвига. 2.Преобразователь кода Грея в двоичный код по п. 1, отличающийс я тем, что в ном разряды регистра содержат триггер, два элемента И-ИЕ и элемент И-ИЛИ-НЕ, первый и второй входы которого соединены с выходами элементов И-ПЕ соответственно, а выход соединен с входом триггера, шина управляющего входа разряда регистра соединена с первыми входами элпмонтов И-МЕ и с третьим входом элемента И-ИЛИ-ИЕ, шнна информационного входа разряда регистра соодинена со вторым входом первого элп)оит.1 И-НЕ и четвертым входом элемента И-ИЛИ-НЕ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 137311. кл. G 06 F 5/О2, 10G8. 2.ПатентФРГ № 1.3О1.836, кл. 21 а36/20, 1071.

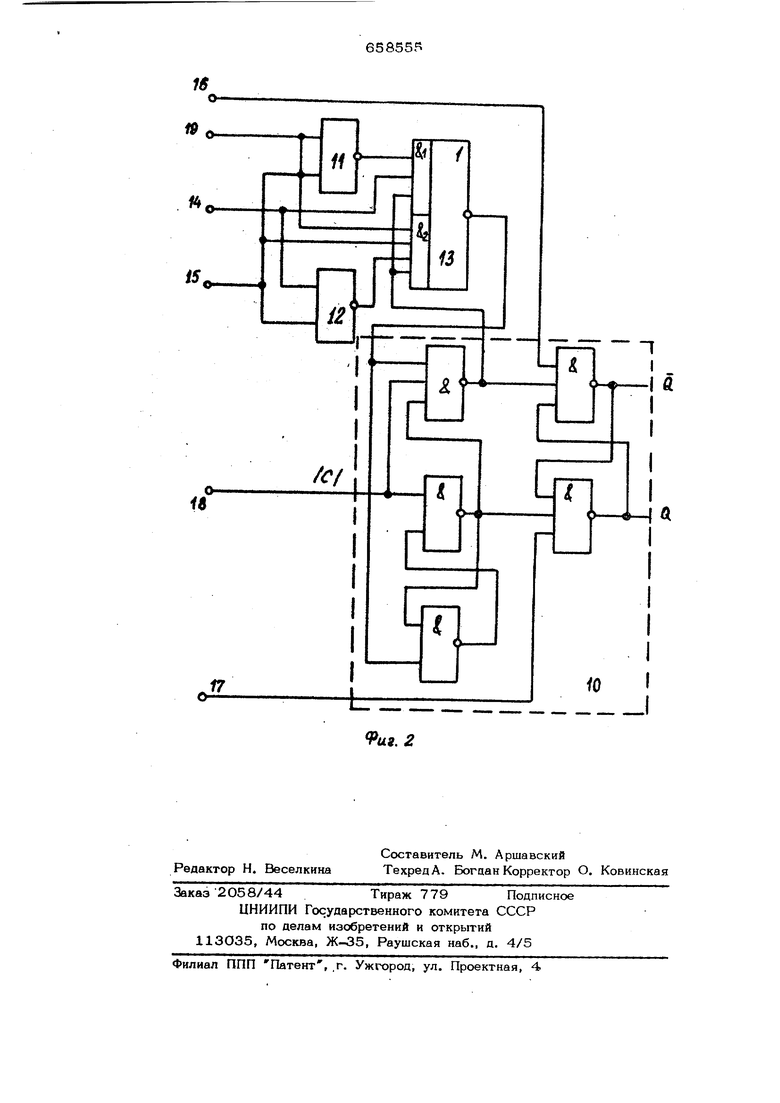

9u9.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода грея в двоичный код | 1977 |

|

SU658556A1 |

| Преобразователь кодов | 1975 |

|

SU763885A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Преобразователь параллельного комбинаторного кода в позиционный код | 1982 |

|

SU1035597A1 |

| Устройство для формирования двоичного кода | 1981 |

|

SU964699A1 |

| Устройство для кодирования 64-разрядных информационных слов в составной корректирующий код с расстоянием шесть | 1982 |

|

SU1132292A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

Авторы

Даты

1979-04-25—Публикация

1976-11-22—Подача