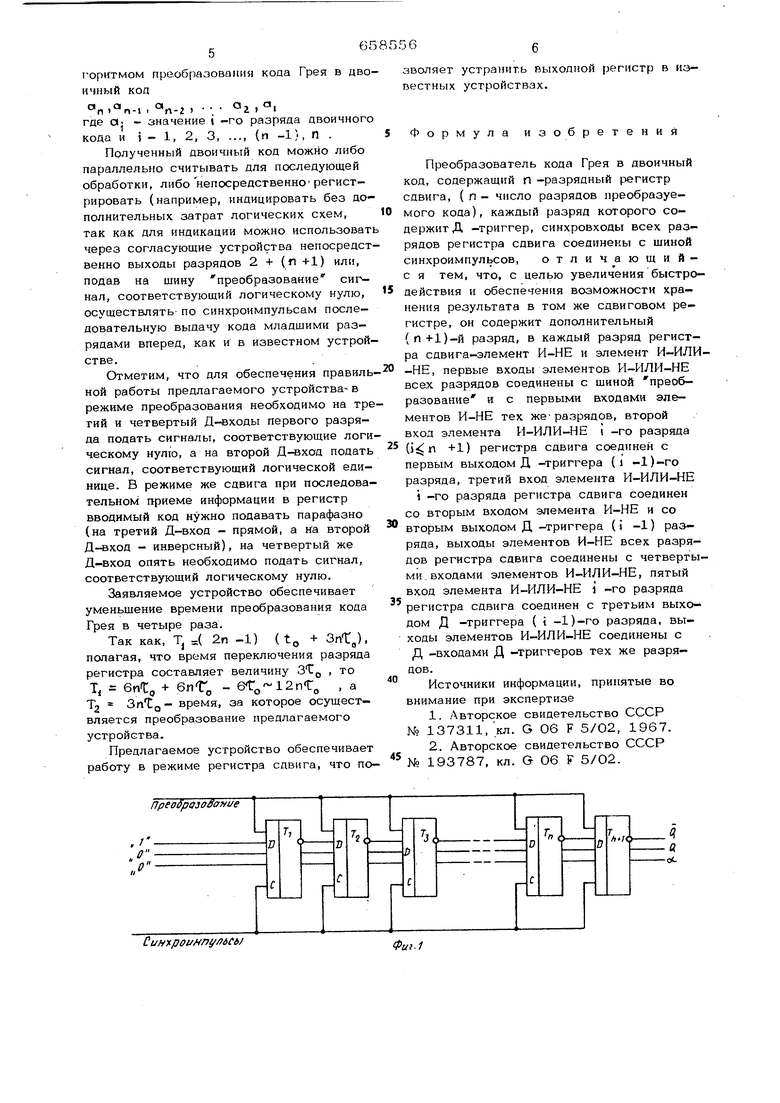

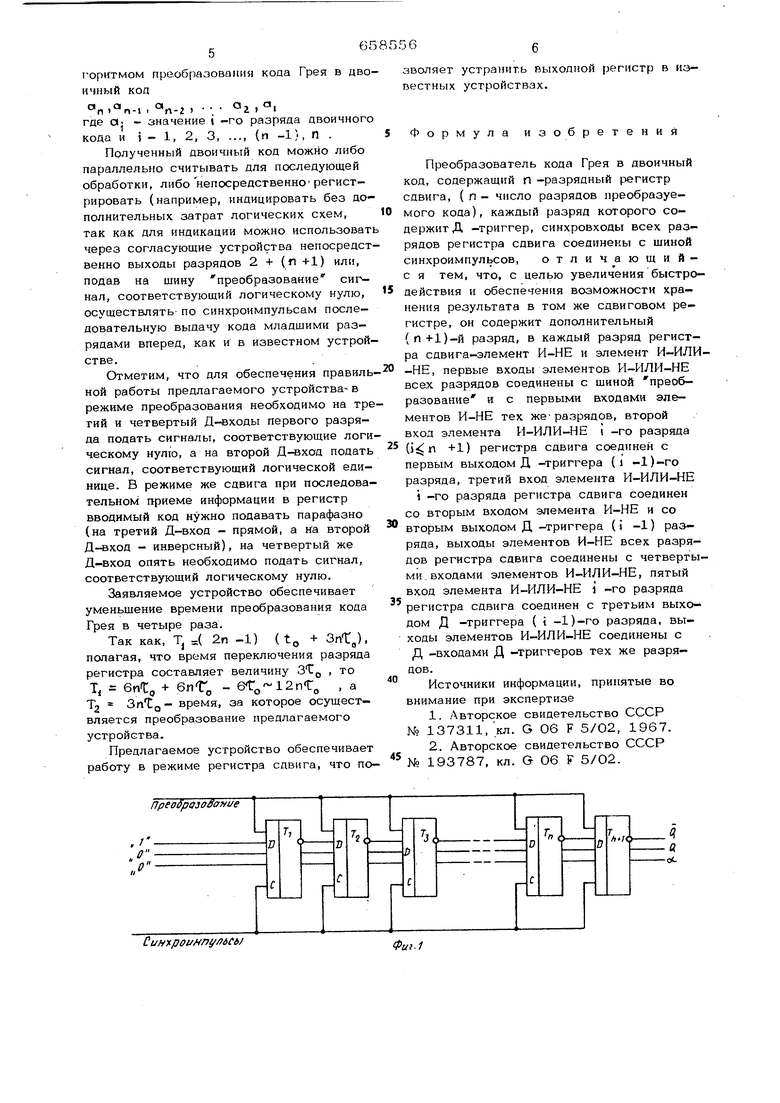

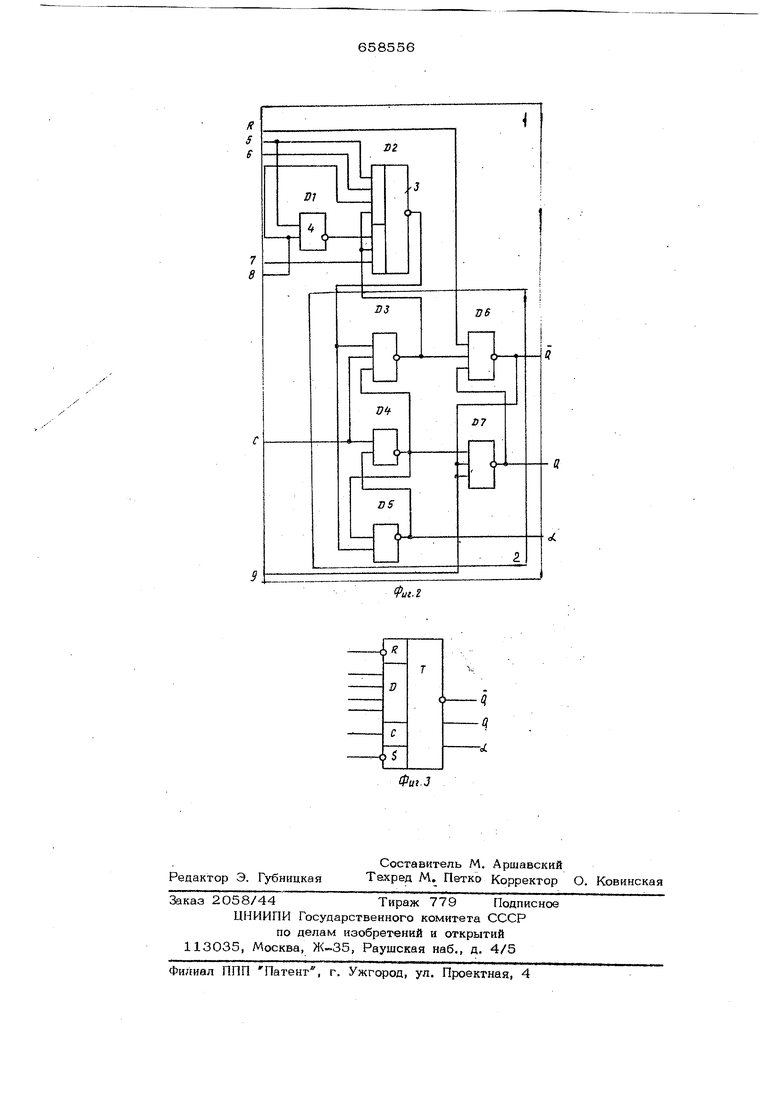

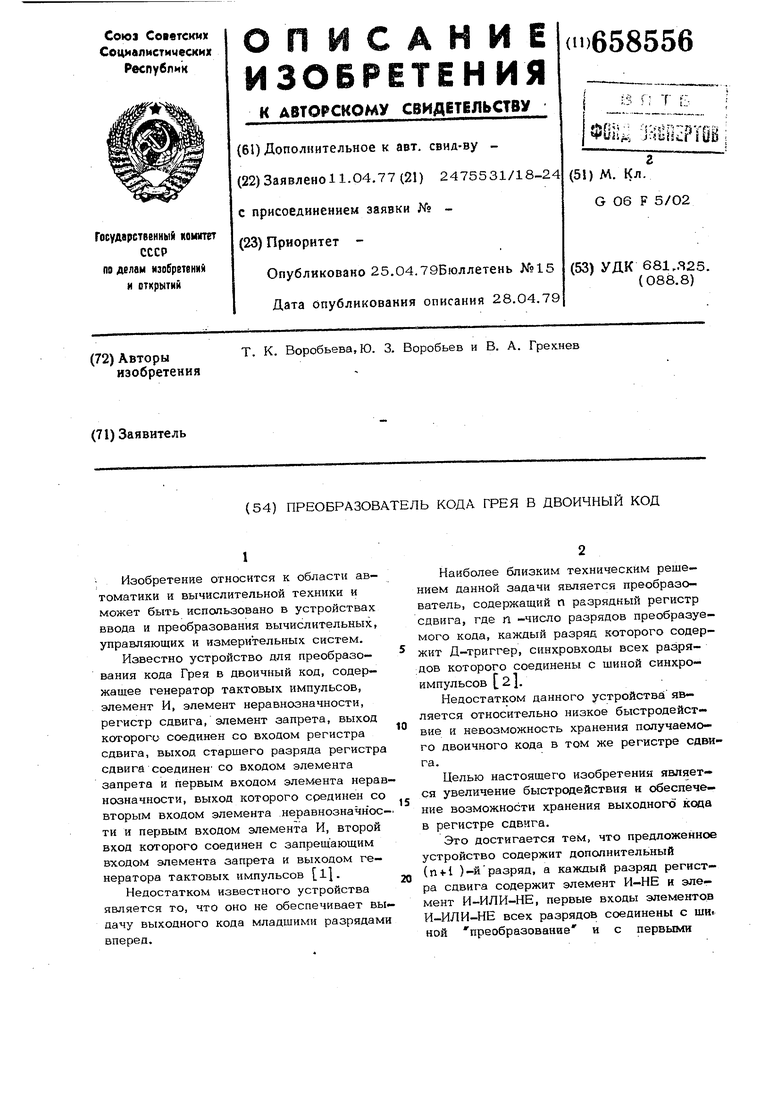

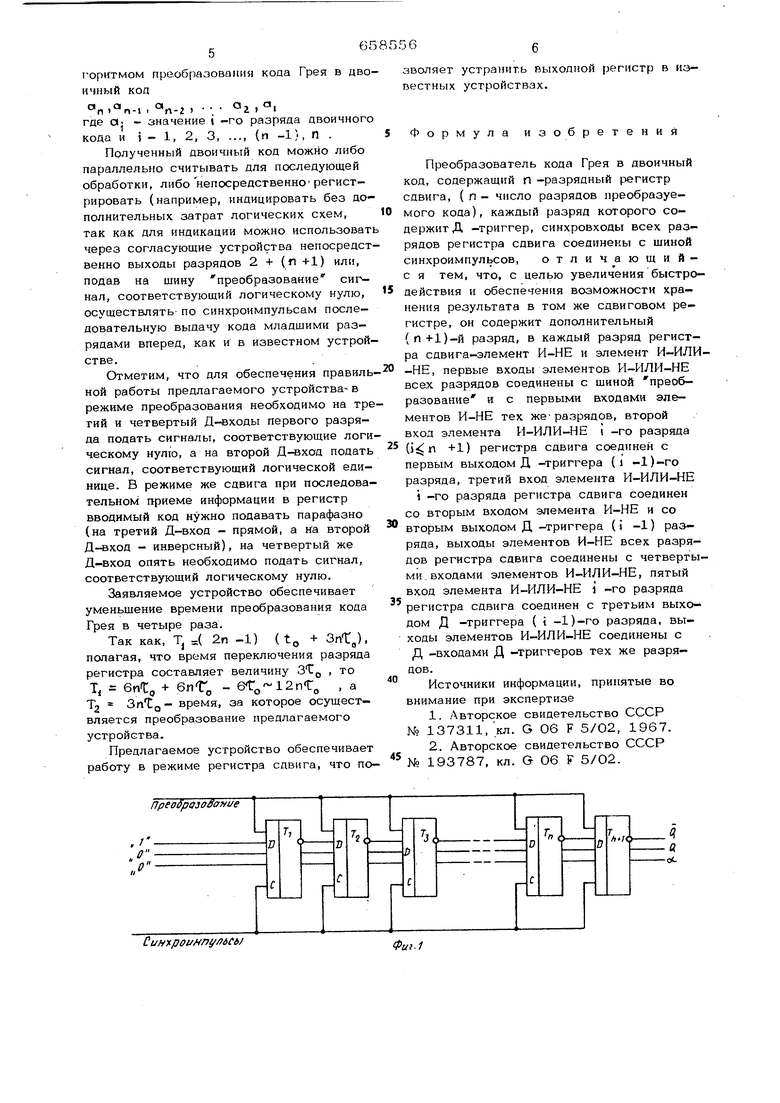

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах ввода и преобразования вычислительных, управляющих и измерительных систем. Известно устройство для преобразования кода Грея в двоичный код, содержащее генератор тактовых импульсов, элемент И, элемент неравнозначности, регистр сдвига, элемент запрета, выход которого соединен со входом регистра сдвига, выход старшего разряда регистра сдвига соединен со входом элемента запрета и первым входом элемента нерав нозначности, выход которого соединен со вторым входом элемента неравнозначнос ти и первым входом элемента И, второй вход которого соединен с запрещающим входом элемента запрета и выходом генератора тактовых импульсов l|. Недостатком известного устройства является то, что оно не обеспечивает вы дачу выходного кода младшими разрядам вперед. Наиболее близким техническим решением данной задачи является преобразователь, содержащий п разрядный регистр сдвига, где п -число разрядов преобразуемого кода, каждый разряд которого содержит Д-триггер, синхровкодь всех разрядов которого соединены с щиной синхроимпульсов 2 . Недостатком данного устройства является относительно низкое быстродействие и невозможность хранения получаемого двоичного кода в том же регистре сдвига. Целью настоящего изобретения является увеличение быстродействия и обеспечение возможности хранения выходного кода в регистре сдвига. Это достигается тем, что предложенное устройство содержит дополнительный ( )-иразряд, а каждый разряд регистра сдвига содержит элемент И-НЕ и элемент И-ИЛИ-НЕ, первые входы элементов И-ИЛИ-НЕ всех разрядов соединены с ши. ной преобразование и с первыми входами элементов И-НЕ тех же разрядов, второй вход элемента И-ИЛИ-НЕ i -го раз ряда () регистра сдвига соединен с первым выходом Д-триггера ( I -1)-го разряда регистра сдвига, третий вход эле- мента И-ИЛИ-НЕ i -го разряда регистра сдвига соединен со вторым входом элемен та И-НЕ и со вторым выходом Д- риггера выходы элементов И-НЕ всех разрядов регистра сдвига соединены с четвертыми входами элементов И-ИЛИ-НЕ, пятый вход элемента И-ИЛИ-НЕ i -го разряда регистра сдвига соединен с третьим выходом Д-триггера ( j -1)-го разряда, выходы элементов Й-ИЛИ-НЕ соединены с Д-«ходами Д-триггеров тех же разрядов. На фиг. 1 приведена структурная схема предлагаемого преобразователя, на фиг. 2 схема разряда регистра сдвига, на фиг. 3условное изображение разряда регистра сдвига. Разряд 1 регистра сдвига состоит из Д-триггера 2, элемента 3 И-ИЛИ-НЕ, элемента 4 И-НЕ, управляющие Д-входы 5-8 задают режим функционирования разряда. Предлагаемое устройство работает следующим образом. По входам R (на фиг. 1 не показаны), производится установка триггеров регистра в исходное (нулевое) состояние сигналом, соответствующим логическому нулю. По входам S , (на фиг. 1 не показаны) производится параллельный прием пбдлежащего преобразованию кода Грея в следующем порядке: старший, п-й, разряд кода Грея записывается в первый разряд регистра, следующий (п-1)-й, во второй, ..., младший, то есть первый, разряд кода Грея - в п-й разряд регистра. Регистр содержит (п+1) разряд. Последовательный прием кода Грея в регистр осуществляется по третьему Д-«ходу первого разряда (фиг. 1) при наличии на шине преобразование сигнала, соответст- вующего логическому .нулю. Код Грея должен вводиться с младших разрядов. В этом режиме предлагаемое устройство работает как обычный регистр сдвига на Д-триггерак. Разряд регистра сдвига предлагаемого устройства выполняет функции обычного Д-триггера при наличии на его первом Д-входе сигнала, соответствующего логическому нулю. При наличии на первом Д-входе сигнала, соответствующего логической единице, разряд регистра сдвига осуществляет сложение по mod 2 значений логических сигнатов, воздействующих на третий и четвертый Д-входы. Таким образом, в режиме преобразование работа разряда регистра предлагаемого устройства может быть описана следующим логическим уравнением:Q(.)® yfi), где x{t) - логический сигнал, воздействующий на третий D -вход в момент времени ; у(-Ь) - логический сигнал, воздействующий на четвертый; TD - вход триггера в момент времени 1 ; Q() - состояние триггера в момент времени ( t +1). Время дискретизируется синхроимпульсами, так как установление триггера в какое-ппибо состояние осуществляется только по воздействию синхроимпульса (за исключением установки по R и S входам). Теперь, зная работу разряда регистра сдвига, легко разобрать работу предлагаемого устройства. Действительно, связи в предлагаемом устройстве выполнены так, что для произвольного К -го, где к-1, 2, 3, ..., п - целое число разряда регистра в режиме преобразования справедливо соотношение x(t))Q,(t)@ /t). где o./t)0 oC/t) ;а.Ь,,..,ЭЬ„,,.„, «2., Qjit) b T n-nVz- inT соответственной, (n-1), (П-2), .,,(п-К)-й разряды кода Грея. Если по истечении времени .. , где LQ - так же как и у прототипа, задержка распространения логического сигнала на одном логическом элементе и п - число разрядов кода Грея, на шину сиахроимпульсы подать тактирующий импульс, то в разрядах 2 + (п +1) регистра окажется соответственно записанным код, в соответствии с логикой работы разряда- регистра л алIopWTMOM преобразования кода Грея в двоичный код 2 . п °п-1 где а- - значение -го разряда ДВОИЧНОГ кода и i - 1, 2, 3, .... (п -1), П . Полученный двоичный код можно либо параллельно считывать для последующей обработки, либо непосредственнорегистрировать (например, индицировать без до полнительных затрат логических схем, так как для индикации можно использоват через согласующие устройства непосредст венно выходы разрядов 2 + (г +1) или, подав на шину преобразование сигнал, соответствующий логическому нулю, осуществлять- по синхроимпульсам последовательную выдачу кода младшими разрядами вперед, как и в известном устрой Отметим, что для обеспечения правиль ной работы предлагаемого устройства-в режиме преобразования необходимо на тре тий и четвертый первого разряда подать сигналы, соответствующие логи ческому нулю, а на второй Д-вход подать сигнал, соответствующий логической единице. В режиме же сдвига при последовательном приеме информации в регистр вводимый код нужно подавать парафазно (на третий Д-вход - прямой, а на второй Д-Бход - инверсный), на четвертый же Д-вход опять необходимо подать сигнал, соответствующий логическому нулю. Заявляемое устройство обеспечивает уменьшение времени преобразования кода Грея в четыре раза. Так как, Т ( 2п -1) (t + 3nt), полагая, что время переключения разряда регистра составляет величину ЗГ , то Т, бпТо о - , а Тз ЗпТ|э - время, за которое осуществляется преобразование предлагаемого устройства. Предлагаемое устройство обеспечивает работу в режиме регистра сдвига, что поПреобразование

зволяет устранить выходной регистр в известных устройствах. Формула изобретения Преобразователь кода Грея в двоичный код, содержащий п -разрядный регистр сдвига, ( п - число разрядов преобразуемого кода), каждый разряд которого содержит Д -триггер, синхровходы всех разрядов регистра сдвига соединены с шиной синхроимпульсов, отличающий гс я тем, что, с целью увеличения быстро- действия и обеспечения возможности хранения результата в том же сдвиговом регистре, он содержит дополнительный (п+1)-й разряд, в каждый разряд регистра сдвига-элемент И-НЕ и элемент И-ИЛИ-НЕ, первые входы элементов И-ИЛИ-НЕ всех разрядов соединены с шиной преобразование и с первыми входами элементов И-НЕ тех жеразрядов, второй вход элемента И-ИЛИ-НЕ i -го разряда ( +1) регистра сдвига соединен с первым выходом Д -триггера (i -1)-го разряда, третий вход элемента И-ИЛИ-НЕ i -го разряда регистра сдвига соединен со вторым входом элемента И-НЕ и со вторым выходом Д -триггера (i -1) разряда, выходы элементов И-НЕ всех разрядов регистра сдвига соединены с четвертыми, входами элементов И-ИЛИ-НЕ, пятый вход элемента И-ИЛИ-НЕ i -го разряда регистра сдвига соединен с третьим выходом Д -триггера ( t -1)-го разряда, выходы элементов И-ИЛИ-НЕ соединены с Д -входами Д -триггеров тех же разрядов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 137311,кл. G 06 F 5/02, 1967. 2.Авторское свидетельство СССР М 193787, кл. G 06 F 5/02.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода грея в двоичный код | 1976 |

|

SU658555A1 |

| Преобразователь кодов | 1975 |

|

SU763885A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| Преобразователь кода Грея в двоичный код | 1982 |

|

SU1087983A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1023334A2 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Регистр сдвига | 1977 |

|

SU651418A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

Cuf rtpouHni/ff6Ci f

Фиг.1

-

-J.

Авторы

Даты

1979-04-25—Публикация

1977-04-11—Подача