to

25

Поступивший на вход 20 запуска сигнап Начало преобразования обнуляет регистры 3 и 4 и разрешает запись информации в регистры 1 и 2, В регистр 1 записывается К чисел в коде Грея, К N/n, где N и п соответственно число разрядов регистра 1 и вводимого числа. В регистр 2 запи- сьшается N-разрядный двоичный код, содержащий I в разрядах 1-, (п+1)-, (2п+1)-,.,.,(К-1). n+1-M и О во всех остальных разрядах,,

На тактовый вход 19 поступают синхроимпульсы, каждый из которых обес печивает формирование одного разряда, начиная qo старшего, всех К выходных чисел. Для завершения преобразования требуется п синхроимпульсов« Синхроимпульсы поступают на формирователь

20 9, котарый формирует короткие импульсы: на первом выходе по переднему фронту входных импульсов, на втором - с задержкой 2/3 периода.

Преобразование кода Грея в двоич- ньй производится поразрядно одновременно для всех К чисел, В первом такте с помощью регистра 2 и элементов И первой группы 5 осуществляется выделение старших разрядов чисел из регистра 1 и их сравнение на сумматорах 7 по модулю два с соответству- кидими. разрядами регистра 3, Так как исходное состояние регистра 3 нуле- то 1 на выходе каждого сумма- 7 по

i- в

разряде соответствуняце1го числа в .коде Грея. Эти единицы записываются в соответствующие разряды регистра 4,

40 принимающего информацию только единичными сигналами, а также через элементы 8 задержки на 1/3 периода синхроимпульсов записьшаются,в регистр 3. После, этого появляется им пульс ,а втором выходе формирователя 9, который осуществляет сдвиг информации в регистрах 2 и 3. Этим обусловлено вьщеление в следующем такте следующего разряда исходных чисел, его сложение по модулю два с содер- .жимым соответствующего разряда регистра 3, которое соответствует суМ- ме по модулю два предьщущих разрядов и запись результата в соответствующий осуществляет следующую коммутацию:55 разряд двоичных чисел в регистре 4.

Изобретение относится к вычислительной те.хнике и может быть использовано в автоматизированных измерительных системах, в частности в устг ройствах обмена информацией между измерительными устройствами и ЭВМ.

Цель изобретения - расширение функциональных возможностей путем реализации обратного преобразования из двоичного кода в код Грея.

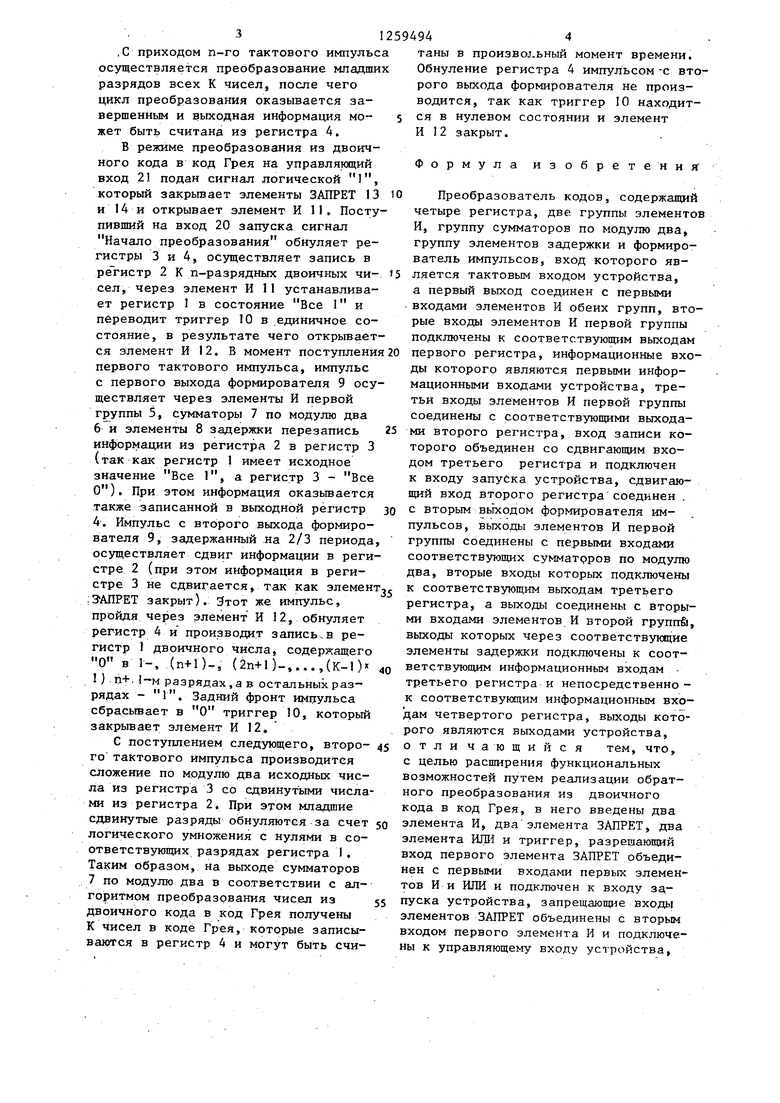

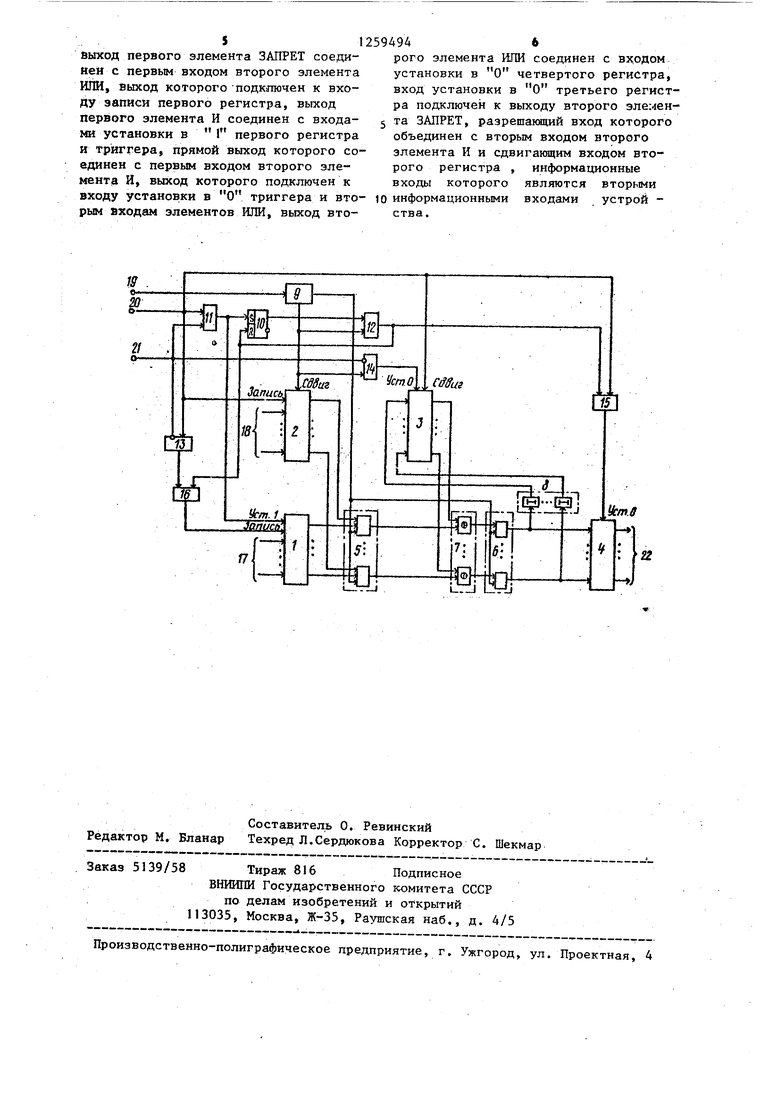

На чертеже представлена функциональная схема устройства.

Преобразователь кода Грея в двоичный код содержит регистры 1-4 с первого по четвертый, первую 5 и вторую 6 группы элементов И, группу 7 сумматоров по модулю два, группу 8 элементов задержки, формирователь 9 импульсов, триггероЮ, первый 11 и первый 13 и второй 12 элементы И, Второй 14 элемент. ЗАПРЕТ, первый 15 к второй 16 элементы ИЛИ. Информационные Входы первого 1 и второго 2 регкстроз являются соответственно nepBbWH 17 и вторыми 18 информацион- входами устройства, вход формирователя 9 импульсов:является тактовым входом 19 устройства. Вход записи второго регистра 2, сдвигающий вход третьего-регистра 3, разрешающий вход первого элемента ЗАПРЕТ 13 и первые входы первых элементов И 11 и ИЛИ . 15 объединены и подключены к входу 20 запуска устройства, запрещающие входы элементов ЗАПРЕТ 13 и 14 и вто- 35 тора рой вход первого элемента И 11 объединены и подключены к управляющему входу 21 устройства.. Выходы четвертого регистра 4 являются выходами.22 устройства.

30

вoe

модулю два имеет место только при наличии i в старшем

Устройство работает следующим образом.

На управляющий вход 21 устройства подается сигнал установки режима: логический О соответствует преобразованию чисел, представленных в коде Грея, в двоичный код, логическая 1 соответствует преобразованию чисел, представленных в двоичном коде, в код Грея.

В режиме преобразования из кода Грея в двоичный код поданный на уп- равлякяци вход 21 сигнал логического

О

элементы И 11 к 12 закрыты, триггер 10 в состоянии О, элементы ЗАПРЕТ 13 и 14 открыты.

50

В последующих тактах устройство работает аналогично.

Преобразование кода Грея в дво ньй производится поразрядно однов менно для всех К чисел, В первом те с помощью регистра 2 и элемент И первой группы 5 осуществляется деление старших разрядов чисел из регистра 1 и их сравнение на сумм торах 7 по модулю два с соответст кидими. разрядами регистра 3, Так к исходное состояние регистра 3 нул то 1 на выходе каждого сум 7 по

i- в

тора

вoe

модулю два имеет место только при наличии i в старшем

В последующих тактах устройство работает аналогично.

,С приходом п-го тактового импульса осуществляется преобразование младших разрядов всех К чисел, после чего цикл преобразования оказывается завершенным и выходная информация может быть считана из регистра 4.

В режиме преобразования из двоичного кода в код Грея на управляющий вход 21 подан сигнал логической I, который закрьгаает элементы ЗАПРЕТ 13 и 14 и открывает элемент И 11, Поступивший на вход 20 запуска сигнал Начало преобразования обнуляет регистры 3 и 4, осуществляет запись в ре гистр 2 К п-разрядных двоичных чисел, через элемент И 11 устанавливает регистр 1 в состояние Все 1 и переводит триггер 10 в единичное состояние, в результате чего открьгоаеттаны в производ.ьный момент времени. Обнуление регистра 4 импульсом -с второго выхода формирователя не производится, так как триггер 10 находит- 5 ся в нулевом состоянии и элемент И 12 закрыт.

Формула изобретения

10 Преобразователь кодов, содержащий четыре регистра, две группы элементов И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов, вход которого ляется тактовым входом устройства, а первый выход соединен с первыми входами элементов И обеих групп, вторые входы элементов И первой группы подключены к соответствующим выходам

ся элемент И 12. В момент поступления 20 первого регистра, информационные вхопервого тактового импульса, импульс с первого выхода формирователя 9 осуществляет через элементы И первой группы 5, сумматоры 7 по модулю два 6 и элементы 8 задержки перезапись информации из регистра 2 в регистр 3 (так как регистр 1 имеет исходное значение Все 1, а регистр 3 - Все О). При этом информация оказьгоается также записанной в выходной регистр 4. Импульс с второго выхода формирователя 9, задержанный .на 2/3 периода, осуществляет сдвиг информации в регистре 2 (при этом информация в регистре 3 не сдвигается, так как элемент,, к соответствующим выходам третьего :ЗАПРЕТ закрыт). Этот же импульс, пройдя через элемент И 12, обнуляет регистр 4 и производит записьчВ регистр 1 двоичного числа, содержащего О в 1-, (n+l)-., (2п+1)-,..., (К-1)х 40 I) п+. 1-м разрядах, а в остальных разрядах - 1. Задний фронт имцульса сбрасьшает в О триггер 10, который закрьгоает элемент И 12.

С поступлением следующего, второ- 5 го тактового импульса производится сложение по модулю два исходных числа из регистра 3 со сдвинутыми числами из регистра 2. При этом младшие сдвинутые разряды обнуляются за счет 50 элемента И, два элемента ЗАПРЕТ, два

регистра, а выходы соединены с вторыми входами элементов И второй группй выходы которых через соответствующие элементы задержки подключены к соответствующим информационным входам третьего регистра и непосредственно - к соответствующим информационным входам четвертого регистра, выходы которого являются выходами устройства, отли чающийся тем, что, с целью расширения функциональных возможностей путем реализации обратного преобразования из двоичного кода в код Грея, в него введены два

логического умножения с нулями в соответствующих разрядах регистра 1. Таким образом, на выходе сумматоров 7 по модулю два в соответствии с алгоритмом преобразования чисел из двоичного кода в код Грея получены К чисел в коде Грея, которые записываются в регистр 4 и Могут быть считаны в производ.ьный момент времени. Обнуление регистра 4 импульсом -с второго выхода формирователя не производится, так как триггер 10 находит- ся в нулевом состоянии и элемент И 12 закрыт.

Формула изобретения

Преобразователь кодов, содержащий четыре регистра, две группы элементов И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов, вход которого является тактовым входом устройства, а первый выход соединен с первыми входами элементов И обеих групп, вторые входы элементов И первой группы подключены к соответствующим выходам

ды которого являются первыми информационными входами устройства, третьи входы элементов И первой группы соединены с соответствующими выходами второго регистра, вход записи которого объединен со сдвигающим входом третьего регистра и подключен к входу запуска устройства, сдвигающий вход второго регистра соединен .

с вторым вьЬс од ом формирователя импульсов, выходы элементов И первой группы соединены с первыми входами соответствующих сумматрров по модулю два, вторые входы которых подключены

к соответствующим выходам третьего

элемента И, два элемента ЗАПРЕТ, два

регистра, а выходы соединены с вторыми входами элементов И второй группй, выходы которых через соответствующие элементы задержки подключены к соответствующим информационным входам третьего регистра и непосредственно - к соответствующим информационным входам четвертого регистра, выходы которого являются выходами устройства, отли чающийся тем, что, с целью расширения функциональных возможностей путем реализации обратного преобразования из двоичного кода в код Грея, в него введены два

элемента ИЛИ и триггер, разрешающий вход первого элемента ЗАПРЕТ объединен с первыми входами первых элементов И и ИЛИ и подключен к входу за,- пуска устройства, запрещающие входы элементов ЗАПРЕТ объединены с вторым входом первого элемента И и подключены к управляющему входу устройства.

J 1

выход первого элемента ЗАПРЕТ соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу записи первого регистра, выход первого элемента И соединен с входами установки в Г первого регистра и триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого подключен к входу установки в О триггера и вторым входам элементов ИЛИ, выход вто594946

рого элемента ИЛИ соединен с входом установки в О четвертого регистра, вход установки в О третьего регистра подключен к выходу второго элемен- 5 та ЗАПРЕТ, разрешакяций вход которого объединен с вторым входом второго элемента И и сдвигающим входом второго регистра , информационные входы которого являются вторыми

10 информационными входами устрой - ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

| Преобразователь кодов из системыОСТАТОчНыХ КлАССОВ B дВОичНыйпОзициОННый КОд | 1979 |

|

SU813408A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1996 |

|

RU2110147C1 |

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ГРЕЯ В ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ КОД | 2003 |

|

RU2248033C1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

Изобретение относится к области вычислительной техники. Применение его в устройствах обмена информацией между измерительными устройствами и ЭВМ позволит уменьшить общее количество оборудования за счет расширения функциональных возможностей преобразователя - обеспечения обратного преобразования из двоичного кода в код Грея. Преобразователь содержит четыре регистра, две группы элементов И, группу сумматоров по модулю два, группу элементов задержки и формирователь импульсов. Благодаря введению триггера, двух элементов И, двух элементов ЗАПРЕТ и двух элементов ИЛИ при подаче соответствующего управляв кяцего сигнала осуществляется.коммутация элементов, позволяющая получить как прямое, так и обратное преобразование. 1 ил. с @ «Л W

Уст.д

22

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР 824783, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кода Грея в двоичный код | 1984 |

|

SU1205311A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-23—Публикация

1985-02-25—Подача