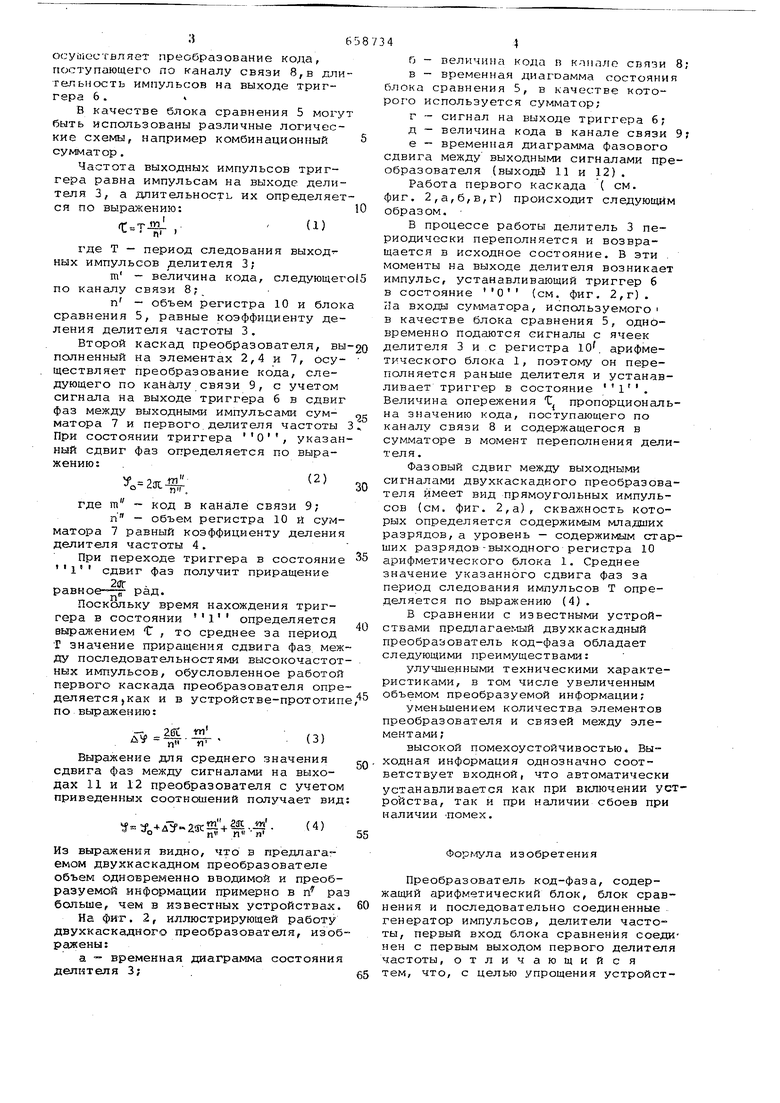

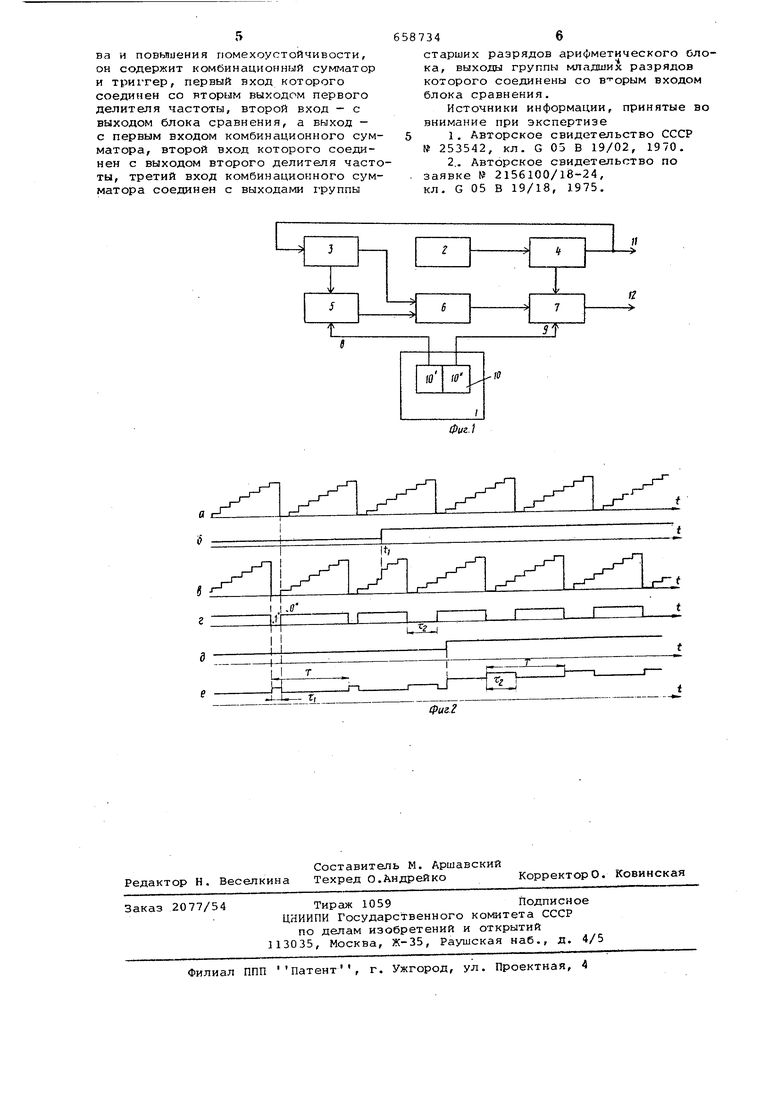

Изобретение относится к области вычислительной техники и может найти применение в системах программного управления металлорежущими станками. Известны двухкаскадные преобр зователи кода в фазу, предназначенные для использования в „сиедящих приводах с высокочастотными фазовыми датчиками обратной связи 11. Наиболее близким по техническому решению к предлагаемому является преобразователь код-фаза, содержащий арифметический блок, блок сравнения и последовательно соединенные генера тор импульсов и делители частоты, первый вход блока сравнения соединен с первым выходом первого делителя частоты 2. Недостатком известного устройства является его сложность, ограниченность диапазона изменения фазы и низ кая помехоустойчивость. Целью изобретения является упрощение и повышение помехоустойчивости устройства. Это достигается тем, что преобразователь содержит комбинацион ный сумматор и триггер, первый вход которого соединен со вторым выходом первого делителя частоты, второй вход - с выходом блока сравнения, а выход - с первым входом комбинационного сумматора, второй вход которого соединен с выходом второго делителя частоты, третий вход комбинационного сумматора соединен с выходами, группы старших разрядов арифметического блока, выходы группы младших разрядов, которого соединены со вторым входом блока сравнения. Блок-схема предлагаемого преобразователя приведена на фиг. 1, временные диаграммы его работы изображены на фиг. 2. Предлагаемый двухкаскадный преобразователь код-фаза, работающий под управлением арифметического блока 1, содержит генератор импульсов 2, первый делитель частоты 3, второй, делитель частоты 4, блок сравнения 5, триггер 6 и комбинационный сумматор7. Входная информация преобразователя по каналам связи 8 и 9 поступает с выходного регистра 10 арифметического блока на входы блока сравнения 5 и комбинационного сумматора 7. Цифрами 10 и 10 обозначены соответственно младшие и старшие разряды выходнрго регистра арифметического блока 1. Первый каскад преобразователя, выполненный на элементах 3,5 и 6 ;$ осутествляет преобразование кола, поступающего по каналу связи 8,в дли тельность импульсов на выходе триггера 6. « В качестве блока сравнения 5 могу быть использованы различные логические схемы, например комбинационный сумматор. Частота выходных импульсов триггера равна импульсам на выходе делителя 3, а длительность их определяет ся по выражению: rf-TJoi. , L-. „, ) где Т - период следования выходных импульсов делителя 3; т - величина кода, следующег по каналу связи 8 объем регистра 10 и бло сравнения 5, равные коэффициенту де ления делителя частоты 3. Второй каскад преобразователя, вы полненный на элементах 2,4 и 1, осу ществляет преобразование кода, следующего по каналу связи 9, с учетом сигнала на выходе триггера б в сдви фаз между выходными импульсами сумматора 7 и первого делителя частоты При состоянии триггера О, указа ный сдвиг фаз определяется по выражению: . V2a где m код в канале связи 9; п - объем регистра 10 и сум матора 7 равный коэффициенту делени делителя частоты 4. При переходе триггера в состояни 1 сдвиг фаз получит приращение равное- рад. Поскольку время нахождения триггера в состоянии определяется выражением С , то среднее за период Т значение приращения сдвига фаз ме ду последовательностями высокочасто ных импульсов, обусловленное работо первого каскада преобразователя опр деляется как и в устройстве-прототи по выражению: ., п 1 Выражение для среднего значения сдвига фаз между сигналами на выходах 11 и 12 преобразователя с учето приведенных соотношений получает ви a- rip astei+f ..Из выражения видно, что в предлагаемом двухкаскадном преобразователе объем одновременно вводимой и преобразуемой информации примерно в п раз больше, чем в известных устройствах.

На фит. 2, иллюстрирующей работу двухкаскадного преобразователя, изображены:

а - временная диаграмма состояния делителя 3; .

изобретения

Преобразователь код-фаза, содержащий арифметический блок, блок сравнения и последовательно соединенные генератор импульсов, делители частоты, первый вход блока сравнения соединен с первым выходом первого делителя частоты, отличающийся тем, что, с целью упрощения устройст4б - величина кода п к-тнале связи 8; в временная диагоамма состояния блока сравнения 5, в качестве которого используется сумматор; г - сигнал на выходе триггера 6; д величина кода в канале связи 9 е - временная диаграмма фазового сдвига между выходными сигналами преобразователя (выходи 11 и 12). Работа первого каскада ( см. фиг. 2,а,б,в,г) происходит следующим образом. Б процессе работы делитель 3 периодически переполняется и возвращается в исходное состояние. В эти моменты на выходе делителя возникает импульс, устанавливающий триггер 6 (см. фиг. 2, г) . в состояние На входы суь1матора, используемого в качестве блока сравнения 5, одновременно подаются сигналы с ячеек делителя 3 и с регистра 10. арифметического блока 1, поэтому он переполняется раньше делителя и устанавливает триггер в состояние . Величина опережения Т пропорциональна значению кода, поступающего по каналу связи 8 и содержащегося в сум-маторе в момент переполнения делителя. Фазовый сдвиг между выходными сигналами двухкаскадного преобразователя имеет вид прямоугольных импульсов (см. фиг. 2,а), скважность которых определяется содержимым младших разрядов,а уровень - содержимым старших разрядов-выходного регистра 10 арифметического блока 1. Среднее значение указанного сдвига фаз за период следования импульсов Т определяется по выражению (4) . В сравнении с известными устройствами предлагаемый двухкаскадный преобразователь код-фаза обладает следующими преимуществами: улучшенными техническими характеристиками, в том числе увеличенным объемом преобразуемой информации; уменьшением количества элементов преобразователя и связей между элементами;высокой помехоустойчивостью4 Выходная информация однозначно соответствует входной, что автоматически устанавливается как при включении устройства, так и при Нсшичии сбоев при наличии Помех.

5

ва и повьмения помехоустойчивости, он содержит комбинационный сумматор и три1тер, первый вход которого соединен со вторым выходом первого делителя частоты, второй вход - с выходом блока сравнения, а выход с первым входом комбинационного сумматора, второй вход которого соединен с выходом второго делителя частоты, третий вход комбинационного сумматора соединен с выходами группы

658734

старших разрядов арифметического блока, выходы группы младших разрядов которого соединены со входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР 253542, кл. G 05 В 19/02, 1970.

2.. Авторское свидетельство по заявке № 2156100/18-24, кл. G 05 В 19/18, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1979 |

|

SU951357A1 |

| Преобразователь сдвига фазы в код | 1984 |

|

SU1193812A1 |

| Цифровое устройство формирования фазового сдвига | 1974 |

|

SU516185A1 |

| Цифровой фазометр-частотомер | 1985 |

|

SU1265644A1 |

| Цифровой фазовый модулятор | 1983 |

|

SU1184081A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU830466A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Устройство для программного управления станками | 1975 |

|

SU607187A1 |

| Генератор псевдослучайных узкополосныхСигНАлОВ | 1979 |

|

SU840897A1 |

Авторы

Даты

1979-04-25—Публикация

1977-04-15—Подача