1

Изобретение предназначено для использования в области радиоизмерений и, в час1ностн, для имитации задержек радиолокационны.х сигналов.

Известно цифровое устройство формироваВИЯ фазового сдвига, содержащее задающий генератор, подключенный через первый делитель частоты к первому входу основного фазового детектора, второй вход которого подключен к выходу второго делителя частоты, установочный вход которого соединен е выходом управляющего генератора, и датчик кода фазы, старщие разряды которого подключены ко входам второго элемента сравнения, другие входы которого соединены с выходами второго делителя частоты, другие выходы второго делителя частоты гюдключены к выходам первого элемента сравнения.

Однако в известном устройстве требуемый фазовый сдвиг между выходными сигналами не может быть сформирован непосредственно, без дополнительных вычислений, из управляющего двоичного кода.

Цель изобретения - расширение функцнональных возможностей устройства.

Указанная цель достигается за счет того, что в устройство дополнительно введены преобразователь прямого кода в дополнительный, фазовый детектор, делитель напряжения и сумматор, причем первый вход дополнительного фазового детектора соединен с выходом первого элемента сравнения, второй вход дополнительного фазового детектора подключен к выходу первого делителя частоты, а выход упомянутого фазового детектора через делитель напряжения подключен к первому входу сумматора, второй вход которого соединен с выходом основного фазового детектора, а выход сумматора соединен со входом управляюluero генератора, при этом входы преобразователя прямого кода в дополнительный подключены к младщим разрядам датчика кода фазы, а выходы преобразователя прямого кода в дополнительный соединены со входами первого элемента сравнения.

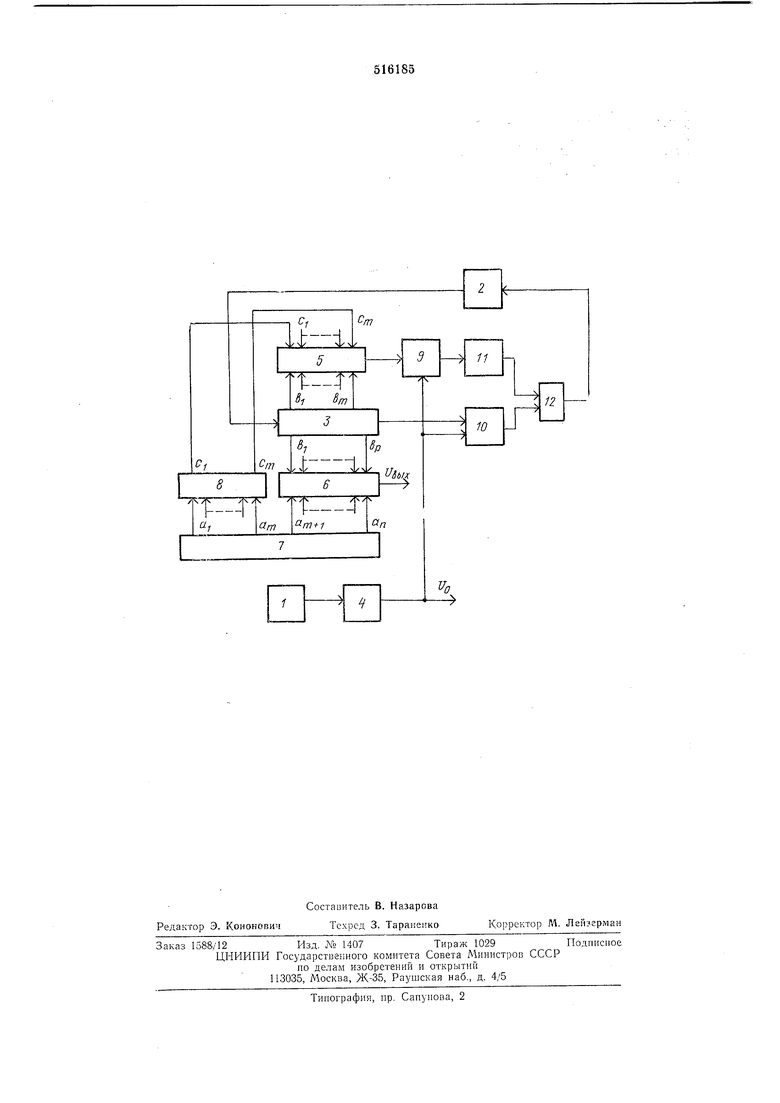

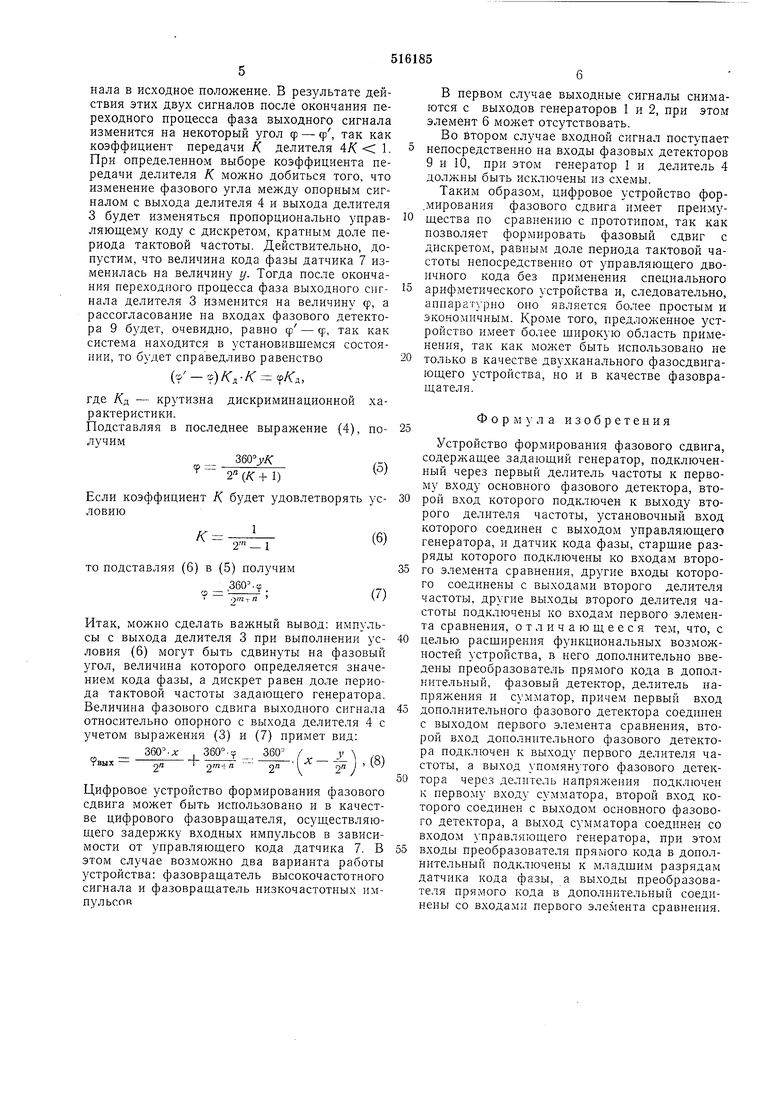

На чертеже нредставлена структурная электрическая схема цифрового устройства формирования фазового сдвига.

Устройство содержит задающий генератор 1, управляющий генератор 2, перестраиваемые по частоте второй 3 и первый 4 делители частоты, содержащие соответственно р и q двоичных разрядов, первый 5 и второй 6 элементы сравнения кодов, датчик 7 кода фазы, преобразователь 8 прямого кода в дополнительный, дополнительный 9 и основной 10 фазовые детекторы, делитель 11 напряжения и сумматор 12.

На чертеже введены следующие дополнительные обозначения; Иьит, flm+l . . . . йп - управляющий ДВОИЧНЫЙ код; aiОт - двоичный код т-младших разрядов датчика 7; Qm+lCln - двоичный КОД (я - ГП) старших разрядов датчика 7; bibmb-p - код с выходов р-разрядного делителя 3; . - выходной КОД првобразователя 8 нрямого кода в дополнительный. Управляющий генератор 2, второй делитель 3, первый элемент 5 сравнения кода, фазовые детекторы 9, 10, делитель напряжения 11 и сумматор 12 образуют систему фазовой автоподстройки частоты, которая осуществляет слежение за фазой выходного сигнала первого делителя 4. Управление управляющим генератором 2 осуществляется сигналом ошибки фазовых детекторов 9 и 10, поступающим с выхода сумматора 12. Весовые коэффициенты сумматора 12 различны благодаря наличию делителя напряжения 11 в цепи дополнительного фазового детектора 9, причем коэффициен,т передачи делителя напряжения 11 меньше единицы. В случае частотной или фазовой расстройки сигналов, действующих на входах фазовых детекторов 9, 10, возникает сигнал рассогласования, который воздействует на управляющий генератор 2 до тех пор, пока не выполняется равенство где /о - частота задающего генератора 1; f - частота управляющего генератора 2. Формирование выходных импульсов, сдвинутых относительно опорного сигнала, снимаемого с выхода первого делителя 4, производится при помощи элементов 5, 6 сравнения кода. Вначале рассмотрим более простой случай, когда значения т-младших разрядов управляющего кода, поступающего с выходов датчика 7, равны нулю. В этом случае выходной импульс элемента 5 сравнения кода синфазен выходному сигналу второго делителя 3, а выходные импульсы элемента 6 сравнения кода при нулевом управляющем коде совпадают по фазе с выходным сигналом первого делителя 4. Как известно, разность фаз сигналов на выходах фазового детектора в системе фазовой автоподстройки частоты в установившемся режиме зависит от типа дискриминационной характеристики фазового детектора. В дальнейшем будем исходить из того, что фазовые детекторы 9, 10 имеют пилообразную характеристику, линейную в диапазоне + 180°. В этом случае постоянный фазовый сдвиг между сигналами равен 180° и может быть легко скомпенсирован съемом выходного сигнала с инверсного выхода триггера старшего разряда делителя 3. При других дипах дискриминационной характеристики компенсация постоянного фазового сдвига не вызывает затруднений. С учетом вышеизложенного выходные импульсы элемента 6 сравнения кодов совпадают по фазе с выходными импульсами первого делителя 4 при нулевом управляющем коде. Формирование требуемого фазового сдвига осуществляется элементом 6 сравнения кодов, выходные импульсы которого вырабатываются в моменты совпадения кодов разрядов делителя 3 и датчика 7. Величина фазового сдвига может изменяться от О до 360° с дискретом, определяемым периодом частоты f и равным где срвых - величина фазового сдвига в градусах;X - значение (п - т)-старших разрядов кода фазы, выраженное в десятичной системе, определяемое по формуле X .-- а,п, 1 2 + а,„+2 2 I+ «н um+iа„ - двоичный код (п - - т)-старших разрядов датчика 7. Формирование фазовых сдвигов с дискретом, равным доле периода тактовой частоты, производится ири помощи элемента 5 сравнения кода преобразователя 8 и фазового детектора 9. Предположим, что необходимо сформировать фазовый угол, опредляемый кодом т-младших разрядов датчика 7, численное значение которого равно у, причем О у / . а,2 + а, - 2 + . - - . ,„ (3) где QIйт - двоичный код т-младших разрядов датчика 7. На входы элемента сравнения кодов 5 пост}пают следующие коды: т-младших разрядов делителя 3 и выходной код преобразователя 8, который формирует дополнительный код из прямого кода первых разрядов датчика 7. Элемеит сравнения кода 5 формирует импульсную последовательность, опережающую выходные импульсы второго делителя 3, на фазовый угол, определяемый значением у. Величина фазового сдвига на выходе элемента сравнения кодов 5 относительно выходного делителя 3 определяется выражением 0 -:-V. 2 Знак минус в выражении (4) показывает, что выходной сигнал элемента сравнения кодов 5 является опережающим. Фазовое рассогласование ф вызывает появление сигнала ошибки на выходе дополнительного детектора 9, что приводит к изменению частоты управляющего генератора 2, в результате чего фаза выходного сигнала делителя 3 будет отставать от своего первоначального значения. Этот фазовый сдвиг в свою очередь приведет к появлению сигнала ошибки на выходе основного фазового детектора 10, которая будет иметь знак, противоположный ошибке на выходе дополнительного фазового детектора 9, т. е.. бует стремиться вернуть фазу выходного сиг нала в исходное положение. В результате действия этих двух сигналов после окончания переходного процесса фаза выходного сигнала изменится на некоторый угол ф - ф, так как коэффициент передачи К. делителя 4/С 1. При определенном выборе коэффициента передачи делителя /С можно добиться того, что изменение фазового угла между опорным сигналом с выхода делителя 4 и выхода делителя 3 будет изменяться пропорционально управляющему коду с дискретом, кратным доле периода тактовой частоты. Действительно, допустим, что величина кода фазы датчика 7 изменилась на величину у. Тогда после окончания переходного процесса фаза выходного сигнала делителя 3 изменится на величину ф, а рассогласование на входах фазового детектора 9 будет, очевидно, равно ф - ф, так как система находится в установившемся состоянии, то будет справедливо равенство (ср-Ср)/Гд./( Ср/Сд, где /Сд - крутизна дискриминационной характеристики. Подставляя в последнее выражение (4), получим .-ч 2«(+1) Если коэффициент К. будет удовлетворять условиюто подставляя (6) в (5) получим - .360-У ./7 - .упгП ( Итак, можно сделать важный вывод: импульсы с выхода делителя 3 при выполнении условия (6) могут быть сдвинуты на фазовый угол, величина которого определяется значением кода фазы, а дискрет равен доле периода тактовой частоты задающего генератора. Величина фазового сдвига выходного сигнала относительно опорного с выхода делителя 4 с учетом выражения (3) и (7) примет вид: ).(8) Цифровое устройство формирования фазового сдвига может быть использовано и в качестве цифрового фазовращателя, осуществляющего задержку входных импульсов в зависимости от унравляющего кода датчика 7. В этом случае возможно два варианта работы устройства: фазовращатель высокочастотного сигнала и фазовращатель низкочастотных импульсорВ первом случае выходные сигналы снимаются с выходов генераторов I и 2, при этом элемент 6 может отсутствовать. Во втором случае входной сигнал поступает непосредственно на входы фазовых детекторов 9 и 10, при этом генератор 1 и делитель 4 должны быть исключены из схемы. Таким образом, цифровое устройство фор.мирования фазового сдвига имеет преимущества по сравнению с прототипом, так как позволяет формировать фазовый сдвиг с дискретом, равным доле периода тактовой частоты непосредственно от управляющего двоичного кода без применения специального арифметического устройства и, следовательно, аппаратурно оно является более простым и экономичным. Кроме того, предлол енное устройство имеет более широкую область применения, так как может быть использовано не только в качестве двухканального фазосдвигающего устройства, но и в качестве фазовращателя. Формула изобретения Устройство формирования фазового сдвига, содержащее задающий генератор, подключенный через первый делитель частоты к первому входу основного фазового детектора, второй вход которого подключен к выходу второго делителя частоты, установочный вход которого соединен с выходом управляющего генератора, и датчик кода фазы, старшие разряды которого подключены ко входам второго элемента сравнения, другие входы которого соединены с выходами второго делителя частоты, другие выходы второго делителя частоты подключены ко входам первого элемента сравнения, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него дополнительно введены преобразователь прямого кода в дополнительный, фазовый детектор, делитель напряжения и сумматор, причем первый вход дополнительного фазового детектора соединен с выходом первого элемента сравнения, второй вход дополнительного фазового детектора подключен к выходу первого делителя частоты, а выход упомянутого фазового детектора через делитель напрялсения подключен к первому входу сумматора, второй вход которого соединен с выходом основного фазового детектора, а выход сумматора соединен со входом управляющего генератора, при этом входы преобразователя прямого кода в дополнительный подключены к младшим разрядам датчика кода фазы, а выходы преобразователя прямого кода в дополнительный соединены со входами первого элемента сравнения.

Vn

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазосдвигающее устройство | 1980 |

|

SU998973A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Формирователь сложного сигнала с частотной и частотно-фазовой манипуляцией | 1982 |

|

SU1136323A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Система передачи дискретной информации частотно-манипулированными сигналами | 1986 |

|

SU1376262A1 |

Авторы

Даты

1976-05-30—Публикация

1974-07-12—Подача