к третьей группе входов сумматора, вь.1ходы сумма1 ора по;1,клю-;ень к jnrформациоь:ньп--1 входам третьего блока элементов I-, выходы KOToiDoro подключены к входам четиертого регистра j выходы четвертого регмстра подключены к В)Коду преобразозатедя и к информа1дио51НЫ1-1 входам четвертого блока элементов И, а;-.1Ходы которого подключены к информационным зход,ам первого регистра, вьгходь первого

8 2

регисм)., к чптвеп гру:;пе аходов с:умматпг)а , аьк p;ijo дифферен11ирую1де о элемя ьсдючен к уоравдиющи Х;;дам го и третьего ojiOKOB :)лемент через второй эд(;кент надсржк управляющему входу qeisjeivj-o ка г лементов И н к уст-авово-) Bxojxy г нггъегс счечч , а го элсм(-нга чад.е:)ЖК-1 :и.)дк:1юч;; нО1-гочно;чу ВХОДУ псргзого счеггч

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

ПРЕОБРАЗОВАТЕ:ЛЬ СДВИГА ФАЗЫ в код, содержащий первый и второй формирователи импульсов, входы которых соединены с источником входных сигналов, первый триггер, выход второго формирователя импульсов подключен к одному входу первого элемента И, выход которого подключен к счетному входу второго триггера, выхюды первого и второго триггеров через первый и второй дифференцирую1цие элементы подключены к входам третьего триггера, выход которого подключен к одному входу второго элемента И, другой вход которого соединен с выходом генератора импульсов, а выход подключен к счетному входу первого счетчика, выходы первого счетчика через первый дешифратор подключены к другому входу первого элемента И, второй счетчик, установочный вход которого соединен с установочным входом первого счетчика, нулевой вход первого триггера соединен с нулевым входом второго триггера, отличающийся тем, что, с це5:ью ггбвышения быстродействия, в него введены второй дешифратор, блок памяти, nepBbrfi,второй, третий и четвертьв регистры, сумматор, первый, второй, третий и четвертый блоки элементов И, третий счетчик, первьп) и второй элементы задержки, элемент ILBi, вьгход первого формирователя импульсов подключен к счетному входу первого триггера, выходы первого и второго дифференпирую1Щ1х элементов подключены к входам считывания и эаап1си блока памяти и через э.чемент 1ЛИ к счетному входу второго счетчика, выходы которого подключены к адресному входу блока памяти, а через BTopoft § дешифратор - к нулевому входу пер(Л вого триггера, входу первого элемента задержки, первому входу первого блока элементов Ник нулевьм входам первого и второго регистров, второй вход первого блока элементов И соеди ней с шиной нулевого потендиала, остальные входы - с выходами первого : счетчика, первая группа вькодов персо оэ вого блока элементоп И подключена к первой группе входов сумматора, а оо вторая группа выходов - к информапионным входам третьего счетчика, N3 счетньп вход которого соединен с выходом- второго элемента Г1, а выходы подключены к второй группе входов сумматора и к информационным входам второго блока элементов И, выходы второго блока элементов И подключены к информационным входам третьего регистра, выходы которого подключены к информационным входам блока памяти, выходы блока памяти подключены к информационным входам второго регистра, выходы которого подключены

J

Изобре.тенке относится, к автоматике и вычислительной технша; и может быть использовано для аналтоговы с источников инфррма /иан с Г1Ифровым вьгчксдите.пьным у ст :очством ,

изобретения - nojibmieiuie быстродействия преобразопа ел сдвига фазы в код:

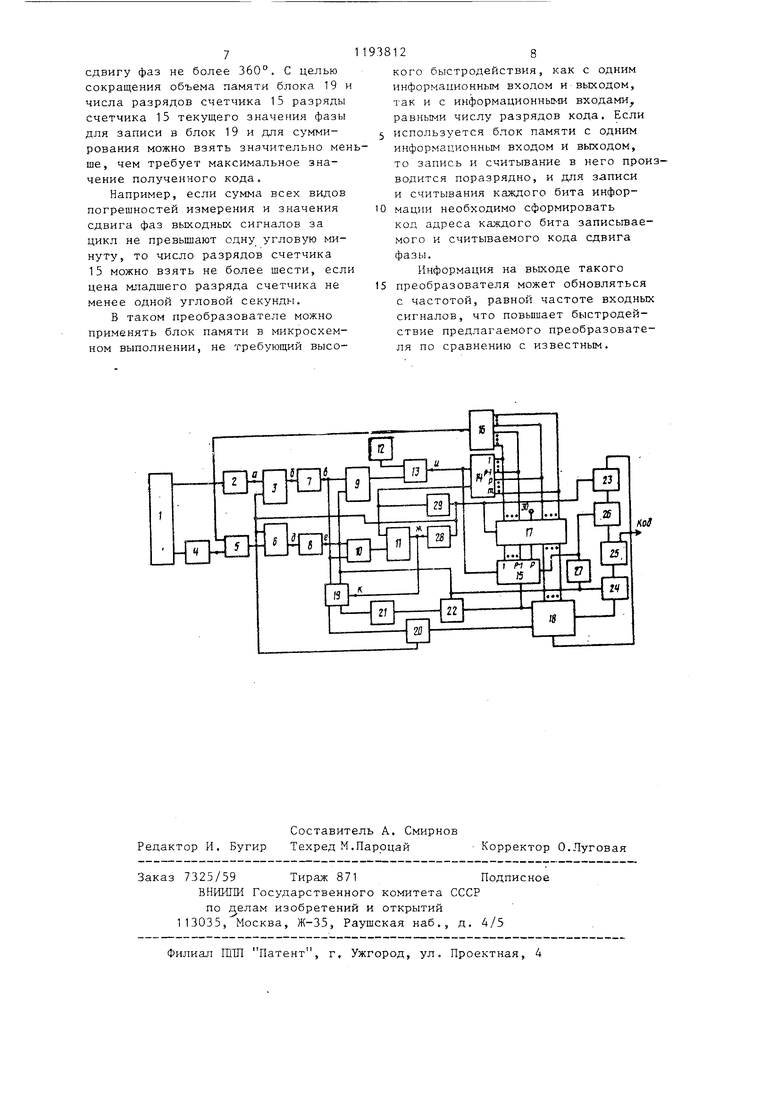

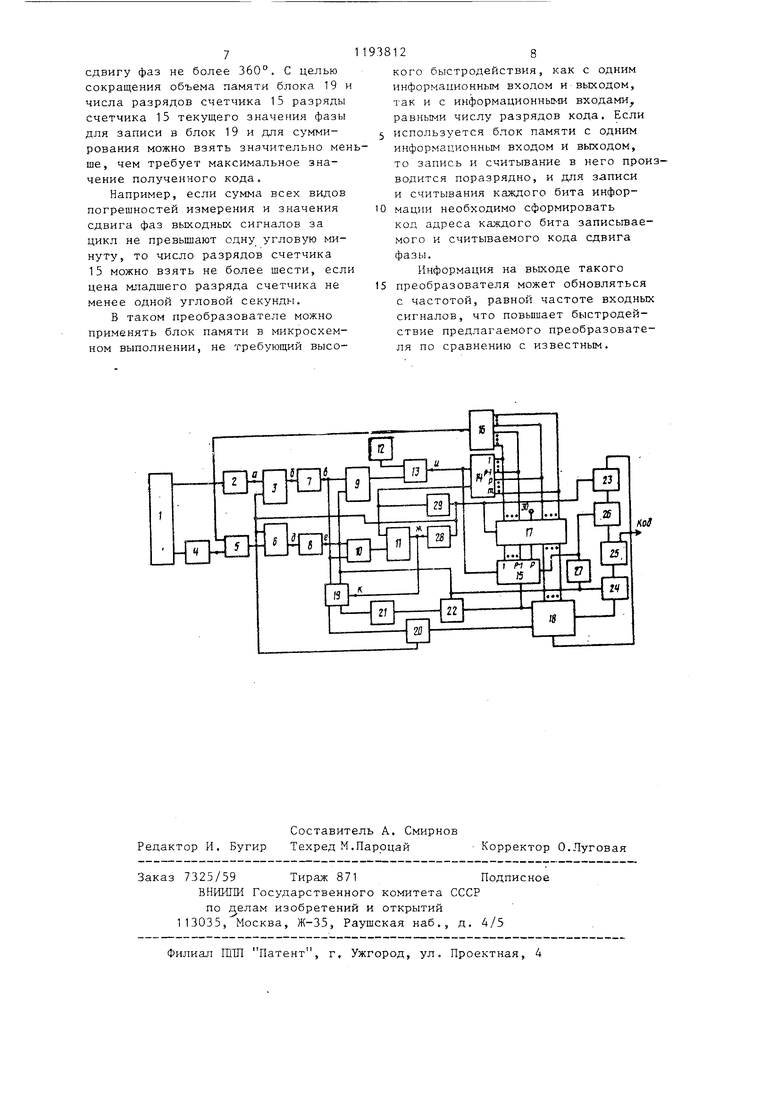

На чертеже приведо-на структурная схема предлагаемого гптаоОразоватслл

11реобразовате.гь содержит источни 1 сигналов (сдвинутых по фазе./, о/ти выход которого чере-1 тормирсшатеаи импуньсов соединен со cncTiibiM 15ход.) триггера .), а. друго -; через последовательно соединенные формировате:1Ь 4 имнудьсов и гзлеменг ii :) - со счет ным входом триггера о, .;ы триг-геоов 3 и 6 через диг ; Ьерендяру10 Хие элемент; / г . 5, фор-гУу-о; ;;; ир.ямс yro ibHbie узки.е иьтпульсм с jicui.):тельных перепадов выxoдп D: сягнв.лои триггеров, соединены с установо НЬ(-ми входами триггера 9, а через одемент ШШ 10 - со счетным входом счетчика 1 1 , ,Д reiUiparopa : ./: импульсов, вырабатыяающе;-о .;с угольные 1 мпульсы .- ън11й часто-ты через элемент И 13 сое.дг1иен со счетными зхода1.ш счетчиков i а. и 15. Управляющий вход элемента И 13 соединен с выходом триггера 9., Вькоды счетчика 14 соедикенЕ, через дешифратор 16 с управляющим входом элемента И 5, а через блок 1 элементов И - с информационным-и входами счетчика 15 и первой группой входов сумматора 18. Вход,ы считывания и записи блока 19 памяти ссеHJiUirlli С выходами ДИ1рфереНЬ,И;У101 :ИХ

3j.ieMiii:oii 7 и 8, адресньи:; хол:л с sbij-одами счетчика 1 ., ис; ключам ле; вып J а информационные и ;ixc,;;s;i - cooiBeTCraCHiKj с нходагчп ;е;истра 20 и С: выхо.;1;ам 5 регистра : , Bxo;t.i pei-истра 21 через бл;:ок 22 злемен-.:чл5 II соединены с второй групHOii ьх(;дов oyм ;aтopa 18 и инфорь а-Ц1-:ОНКЫг-11: БМХОДПчИ C4t-iiHKa : ., а Л:.::o;ii.; регистра 2;: сое/игнен;. г pej-jjft ipyiiioii входоь сумма:-ора Г-, етяертаи р/ниа входов суммач-о :, .-i 2 с..М:-f i- i. I- :jb).xo :aMi-i регистра с.: а ,b. -(Срез .-1едовате:;;..;:.:. сосдиii), 3.;i:.;K /о эл€;--1еатов п - i и . входа и рсл -1отру 2;, Exo;i ол;.-;а 9 иамкг;; сии овреме;;; ;. соединен ( -11ран.члюи;14М .,чми (.KI-H.; .2 i; .:J ;sjieM( о;; V; ii через ч.ламаит 27 заде1;жки с упра. ах одам;; оаока 2о эд;емен:ч)в И и с ус:та;1скочiiiji--. BXi.;.;i.oM c-)ef4WKa 15. BьDгoд j счет чикг il дешифратор 28 соедине Ы Ga,.B;) с H;- Leвым i входами pi-i г;.ч;;)ов 3 ii г. регист1)оя 2(1 ; 22, с вервьп входим блока i / элеме гго}; t у, с входом ojiGMeHTa 29 задерхкг. .о/ хоторО1-с; 1:оедЕ нен с ус:ано-во-чным входом счетчика 14 и счетчи-ка 11. Второй вход блока 17 соединен с 1ПИНОЙ 30 нулевого потенпиада.

Блок 17 зле-ментов И состоит из га + 1 элементов И. где m - число разрядов счетчика 14. Первые входы элемент-ов И блока 1 7 соединены с первым УХОДОМ. ;) .вторые входы га элементов И -- с тргп ъими входами 3 блока 17. Второй вход одного из элементов И блока 17 соединен с вт рым входом блока 17 и с шиной нуле вого потенциала, «а выход этого элемента И - с одним из вторььх; выходов блока 17 и с информационны входом старшего разряда счетчика р - 1 выходов элементов И (где р число разрядов счетчика 15) соединены с вторыми выходами блока 17, а остальные - с первыми выходами блока 17, Сумматор состоит из трех комбинационных сумматоров, причем первы комбинационньБ1 сумматор состоит из р разрядов, второй комбинационный сумматор - из (т - р + 1) разрядов а третий - из m разрядов. Первая и вторая группа входов первого комбинационного сумматора соединены соответственно с второй и третьей группами входов сумматора 18. Выход старшего разряда первого комби нацконного сумматора соединен с BTOpo i группой входов второго комб Аационного сумматора, первая групп входов которого соединена с первой группой входов сумматора 18. Первая группа входов младших разрядов третьего комбинационного сум мато1)а соединена с выходами р-1 младших разрядов первого комбиfiauHOHHoro сумматора, а остальные входы старших разрядов - с вьсходам третьего комбинационного сумматора. Вторая группа вхоцов третьего комбинационно1о сумматора соединена с четвертой rpynnoii HXOZIOB сумматора 18, а вьгхо;;ь - с выходам сумматора. Преобразователь работает следую щим образом. В конце предьи1ущего никла после установки в исходное состояние всех триггеров, счетчикон и регист ров выходно сигнал источника 1 сигналов через формирователь 2, вырабатывающий старт-импульсь:, устанавливает счетный триггер 3 в единичное состояние. Сформированный с положительного перепада триггера 3 дифференцирующим элементом 7 импульс устаьавливает три reii 9 в еди.ничное состояние, откры ая э.чемент И 13, и импульсы генератора i 2 посту1:ают на счетчики i4 и ;5. Когда код-б счетчике 1А 1р€-п;, величину, соответствую12щую половине полного значения фазы, дешифратор 16 открывает элемент И 5, разрешая прохождение стоп-импульсов с формирователя 4 на счетный вход триггера 6. Поделенные на два триггером 6 и сформированные ди4х|)еренцирую1дим элементом 8 стопимпульсы устанавливают триггер 9 в нулевое состояние, закрывая элемент Н 13 и прекращая поступление импульсов с генератора 12 до прихода очередного старт-импульса. Если измеряемый сдвиг фаз в начале цикла измерения меньше половины полного значения фазы, следуюiiirai непосредственно за старт-импуль . стоп-импульс исключается, ес;п1 же измеряемьй сдвиг фазы превышает половину полного значения сдвига фазы, то измеряемьй сдвиг фаз берется от старт-импульса до б.чижайшего стоп-импульса, и данньй принцип работы сохраняется до конца тек тцего цикла. Поделенные на два триггерами 3 и 6 старт- и стоп-импульсы через элемент i-UDi 10 поступают в счетчик 11. Цикл измерения заканчивается после п-кратного измерения мгно BeiiHOio значения сдвига фаз. СумMajMibul код п-кратпого измерения накапливается в счетчике 14, счет числа измерени производится счетчиком 1, где в конце цикла измерения собирается число 2п + 1, При этом возбуждается выход дешифратора 28, устанавливающий в исходное состоя ие триггеры 3 и 6, регистры 20 п 23 и через элемент 29 задержки счетчики 14 и 11. На счетчике 5 после ка: ;дого измерения устанавливается код текущего значения фазы. Импульсами с выхода дифференпирующего элемента 8 через блок 22 э.лементов И код со счетчика 15 переписывается в регистр 21, после чего счетчик 15 обнуляется. Теми же импульсами производится поразряд ая или параллельная запись в 6:ioK 19 памяти кода регистра 21. jV;pec записи вырабатывается г-;етчиком 11. Младший разряд счетчика 11 не участвует в формировании адреса кода записи и считывания. Первый текущий код фазы в цикле записывается по первому адресу, а (п-1)-й текущий код фазы - по (п-1)-му адресу. Текущий код п-го измерения в блок 19 памяти не записывается.

S

следовательно, блок 19 может иметь не более п-1 адресов.

Считывание с блока 19 памяти начинается одновременно с началом текущего измерения фазы и производится импульсами, сформированными дифференцирующим элементом 7.

В каждом цикле считывание начинается с первого адреса блока 19 памяти и предшествует записи по этому адресу нового текущего значения фазы. Считанная информация хранитс в регистре 20 в дополнительном коде В конце первого цикла измерения, перед установкой в исходное состояние импульсом дешифратора 28 счетчиков 14 и 11, суммарный код фазы со счетчика 14 через блок 17 элементов И, счетчик 15, сумматор 18, бло 24 элементов И записывается в регистрах 25 и 23. Усредненное значение выходного кода фазы получается путем деления суммарного кода регистра 25 на число п измерений в цикле. При п 2 деление производится простым сдвигом влево суммарного кода фазы на К двоичных разрядов.

В конце первого текущего измерения второго цикла на вторую группу входов сумматора 18 поступает код фазы первого текущего измерения, а на третью группу входов в дополнительном коде - значение фазы первого измерения первого цикла, которое хранилось в блоке 19 памяти. ..а выходах сумматора 18 получается разница кодов (п + 1)-го и первого измерений, которая суммируется с суммарным кодом регистра 25.

Суммарное значение кода фазы первого цикла имеет впд

N(1) N,j + .

Суммарное значение кода после первого измерения вт{зрого цикла

N (2) N,+ . .. Nf,, N(1) + (N,- N,).

После n + 1 измерения в регистре 25 накапливается суммарный код фазы п последних измерений.

Управляклцим импульсом, сформированн,1м в конце каждого измерения, сумма, полученная в сумматоре 18, через блок 24 элементов И записывается в регистре 25. Через время.

38126

определяемое -элементом 27 задержки, эта же сумма записывается в регистре 23, и производится обнуле1-:ие счетчика 15

5 В конце второго текущего измерения второго цикла на группу входов сумматора 18 поступает код фазы этого измерения, а на третью группу входов в дополнительном коде О значение фазы второго измерения первого цикла, которое хранилось в блоке 19 памяти. Получается разница кодов (п + 2)-го и второго измерений, которая суммируется с суммарным кодом регистра 25. Ив данном случае нетрудно доказать, что после п - 2 измерения в регистре 25 накапливается cyivrMapHbrfi код фазы п последних измерений.

20 Таким образом, во втором пикле после каждого измерения до 2п-1 измерения в регистре 25 }шкап:1ивается суммарный код последних измерений. После п-го измерения второго цикла

суммз.рный код фазы со счетчика

14 импульсом дешифратора 28 записьпзается в регистрах 25 и 23.

Запись кода счетчика 14 в регистрах 25 и 23 производится следующим образом. Импульсом дешифратора 28 через блок Г/ элементов И код (р-1) младших разрядов счетчика ; 4 записывается в счетчике 15, Ол,4ювремеино тем же импульсо -: устанавливаются в нулевое состояние регистры 20 и 23 и через один из элементов И блока 17 старший разряд счетчика 15. , гак как регистры 20 и 23 и стар) разряд счетчика , 5 содержат только нули, код с младших разрядов счетчлка 1 5 и осталь:1ых стар1у;-гк разрядов счетчика 14 через сумматор 18 ;i открытый блок 24 элементов И импульсом дифференцирующего элемента 8 записывается в регистрах 25 и 23 .

Таким обр.гзоМ; начиная с п-го измерения, з каждом последующем измерении мгновенного значения сдзига фаз в регистре 25 формируется суммарный код сдвига фаз последних п измерений, и, следовательно, быстродействие преобразователя становится равным частоте измерения мгновенного значения сдвига фаз.

Число разрядов счетчика 15 выбирается с таким расчетом, чтобы его максимальный вес соответствовал

7

сдвигу фаз не более 360. С целью сокращения объема памяти блока 19 числа разрядов счетчика 15 разряды счетчика 15 текущего значения фазы для записи в блок 19 и для суммирования можно взять значительно меше, чем требует максимальное значение полученного кода.

Например, если сумма всех видов погрешностей измерения и значения сдвига фаз выходных сигналов за цикл не превышают одну угловую минуту, то число разрядов счетчика 15 можно взять не более шести, если цена младшего разряда счетчика не менее одной угловой секунды.

В таком преобразователе можно применять блок памяти в микросхемном выполнении, не требующий высо3812g

кого быстродействия, как с одним информационным входом и выходом, так и с информационными входами равными числу разрядов кода. Если 5 используется блок памяти с одним информационньм входом и выходом, то запись и считывание в него производится поразрядно, и для записи и считывания каждого бита информации необходимо сформировать

код адреса каждого бита записьтаемого и считываемого кода сдвига фазы.

Информация на выходе такого

5 преобразователя может обновляться с частотой, равной частоте входных сигналов, что повышает быстродействие предлагаемого преобразователя по сравнению с известным.

| Способ преобразования угла поворота вала в код | 1977 |

|

SU739606A1 |

| А,Ахметжанова, М,: Энергия, 1978, с,186, рис,6,4. | |||

Авторы

Даты

1985-11-23—Публикация

1984-05-22—Подача