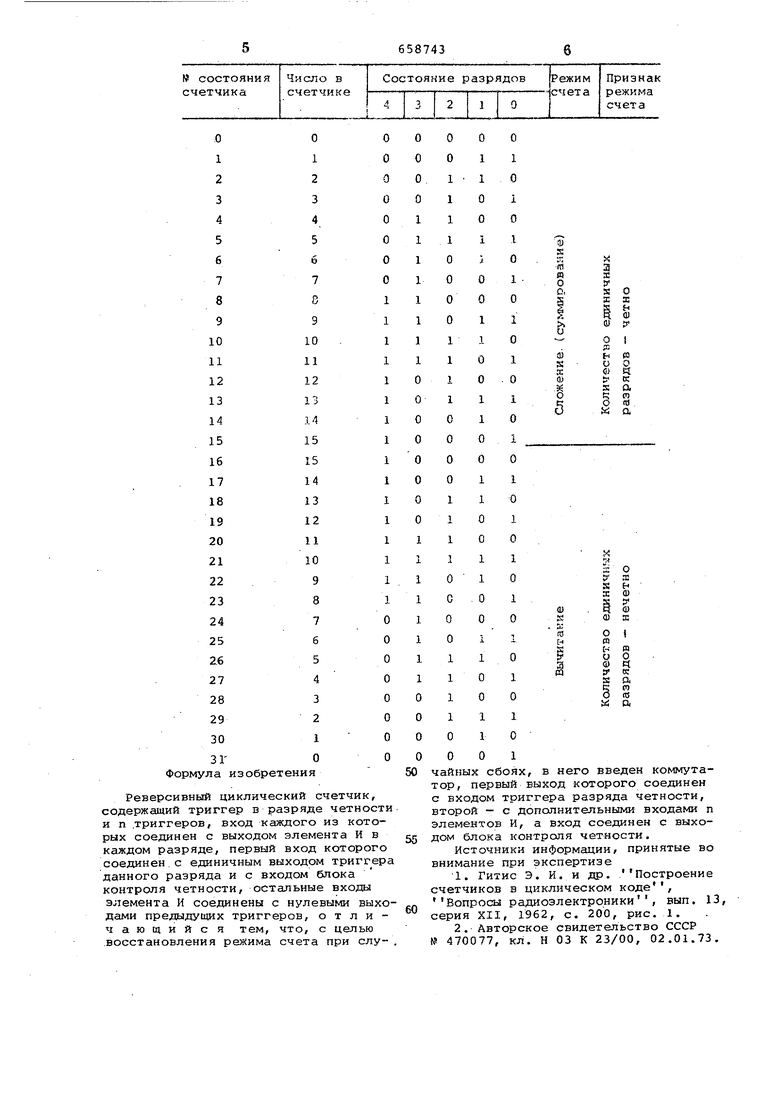

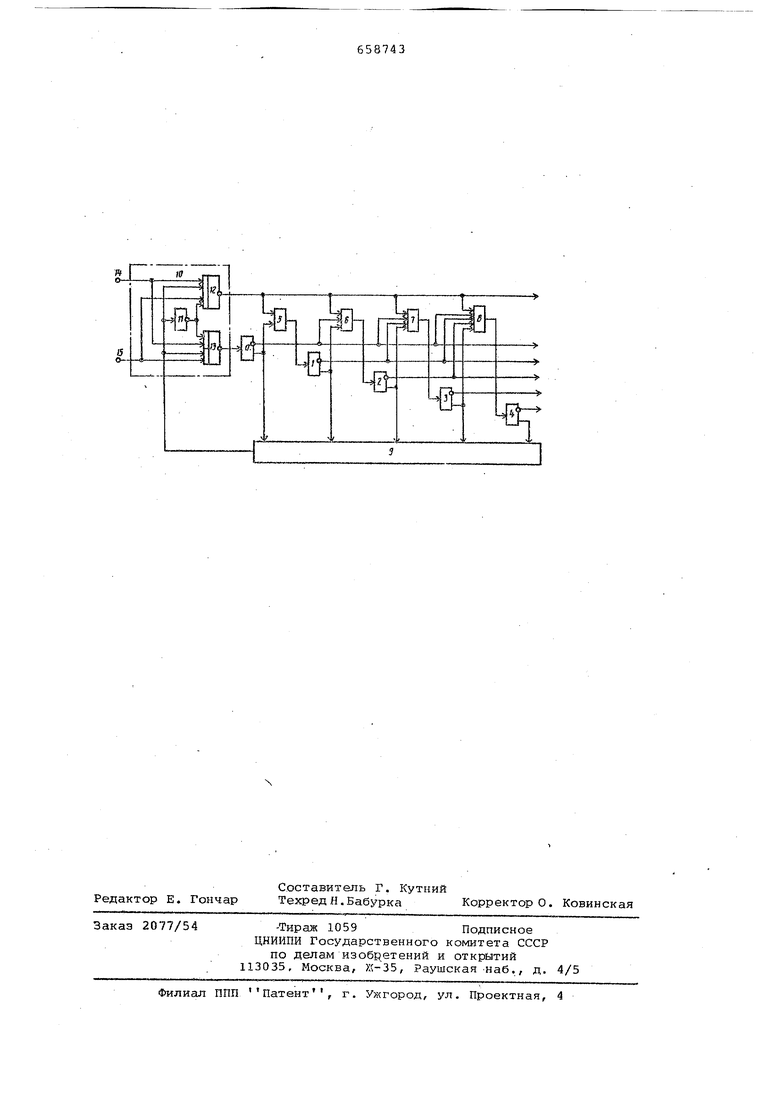

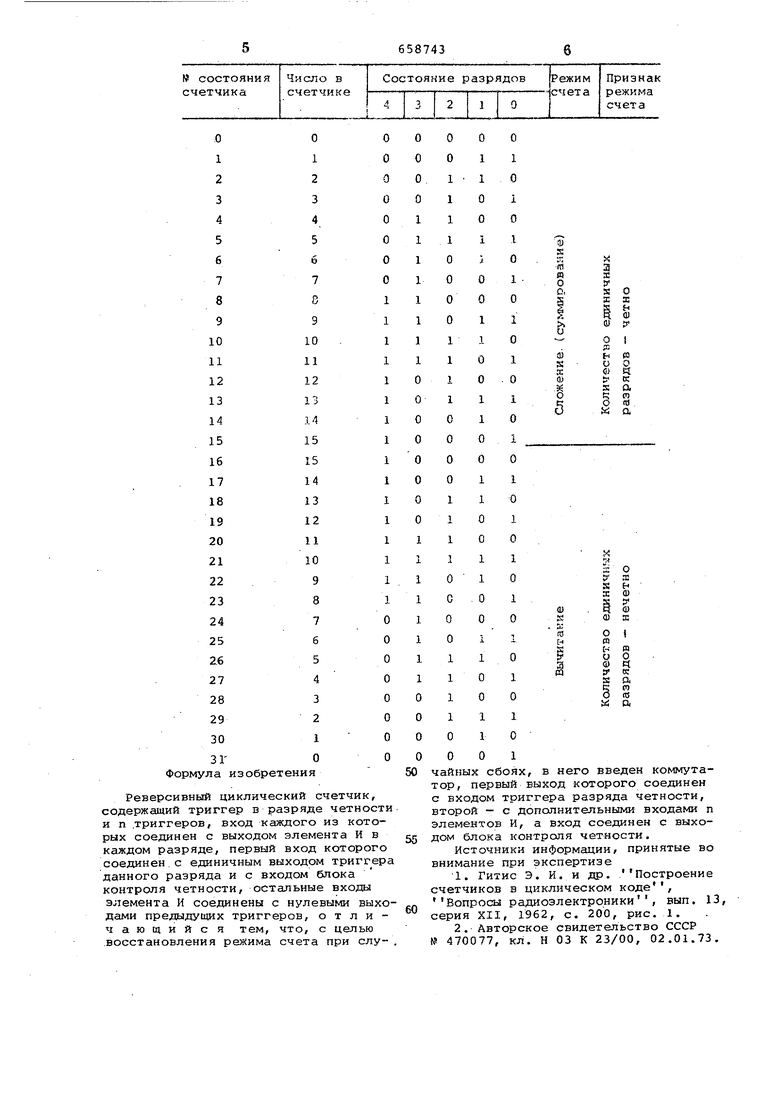

Изобретение относится к вычислительной технике и может быть использовано в устройствах дискретной обра ботки информации. Известен реверсивный циклический счетчик, содержащий триггер в разряд четности и триггеры с управляющими каскадами совпадения в разрядах счета 1. Однако в известном счетчике случайные возмущения могут вызвать изменение режима счета - перевести из режима сложения в режим вычитания или наоборот. Отсутствие контроля за режимом счета сохранит это нарушение и в последующем функционировании, так как поступающие реверсирующие импульсы каждый раз будут приводить счетчик в режим счета, противоположный требуемому. Известен также реверсивный циклический счетчик, содержащий триггер в разряде четности и п триггеров, вход каждого из которых соединен с выходом элемента И в каждом разряде, первый вход которого соединен с единичным выходом триггера данного разряда и с входом блока контроля четности, остальные входы элементов И соединены с нулевыми выходами предыдущих триггеров 2. Цель изобретения - восстановление режима счета при случайных сбоях. Достигается это тем, что в реверсивный циклический счетчик, содержащий триггер в разряде четности и п триггеров , вход каждого из которых соединен с выходом элемента И в каждом разряде, первый вход которого соединен с единичным выходом триггера данного разряда и с входом блока контроля четности, остальные входы элементов и соединены с нулевыми выходами предыдущих триггеров, введен коммутатор, первый выход которого соединен с входом триггера разряда четности, второйс дополнительными входами п элементов И, а вход соединен с выходом блока контроля четности. На чертеже приведена схема счетчика. Счетчик содержит триггер 0-разряда четности, триггеры 1-4 с управляющими каскадами элементов И 5-8 (совпадения) разрядов счета, блок 9 контрр ля четности разрядов и входной коммутатор 10, выполненный на элементе НЕ 11 и элементах 2И-2ИЛИ-НЕ 12,13. Импульсы.слежения подаются на вход 14, импульсы вычитания - на вход 15. Дпя пояснения функционирования предлагаемого счетчика в таблице при ведена последовательность изменения под воздействием счетных импульсов состояний 4-х разрядного нереверсивного циклического счетчика, выполкен :ного также на разрядах счета с управ ляющими каскадами эле ментов совпадения и с триггером в разряде 4eTHOj::TH .Для сопоставления разряды счетчика в таблице пронумерованы так же, как и на схеме предлагаемого реверсивного счетчика. Как видно из таблицы, нереверсивный циклический счетчик в процессе, счета последовательно проходит через области (режимы) сложения и вычитания. Отличительными признаками этих режимов являются сохранение Четного количества единичных разрядов (включая и разряд О четности) в режиме сложения и Нечетного --в режиме вычи тания. Реверсирование счета в циклическом счетчике заключается в принудительном переводе его ИЗ Области сложения в область вычитания и наоборот Методом реверсирования, использованным в предлагаемом счетчике, является изменение состояния одного из разрядов счета. При этом, в счетчике с раздельными входами импульсов сложения и вычктанир нужно изменять состояние того разряда, на входе которого продолжает сохраняться сигнал, вызвавший его переключение. В . случаер одновременно с реверсировайием счета, содержимое счетчика буде уменьшаться или увеличиваться на еди ницу. Так, если счетчик доработал в режиме вычитания до 29-го состояния (в счетчике число 2), то возбужденны окажется вход триггера 1. При поступлении импульса сложения нужно изменить состояние именно этого триггера, тогда счетчик перейдет в . состояние, т«е... одновременно с переводом в режим суммирования в счетчик добавляется единица (содержи мое счетчика стало равным трем), Таким же образом при переводе из режима сложения (см,, например, из 12-го состояния) в режим вычитания Число в счетчике уменьшается на единицу (изменяется состояние З-го раз:ряда счета и счетчик переходит в 20состояние). В предлагаемом реверсивном счетчике блок 9 контроля четности по состояниям триггеров 0-разряда 4 определяет режим счета (слохсение или вычитание) и управляет входным коммутатором 10, направляя входные HM- пульсы на реверсирование счета, если возбужденный вход счетчика не совпадает С режимом счета, или на продолжение счета в случае совпадения. При продолжении счета импульсы проходят 34 на вход триггера 0-разряда четности и в этом случае счетчик функционирует как обычный циклический счетчик. При реверсировании входной импульс, в качестве запрещающего, передается на дополнительные входы управляющих каскадов элементов И 5-8 совпадений и сигнал, имеющийся на входе триггера одного из разрядов счета, убираетсй на время действия этого импульса и опять разрешается после окончания его. В результате, по окончании-реверсирующего импульса триггер с возбужденным входом изменит свое состояние, т.е. счетчик перейдет в другой режим счета и одновременно содержимое его увеличится или уменьшится на единицу. Так, например, при наличии режима сложения блок 9 контроля четности выдает единичные уровни на ступень И элемента 2И-2ИЛИ-НЕ 12, пропускающего сигнал с входа 14 сложения, и на ступень И элемента 2И-2ИЛИ-НЕ 13, пропускающего сигнал с входа 15 вычитания. Вторые ступени И обоих элементов 2И-2ИЛИ-НЕ заперты проинвертированным на элементе 11 сигналом схемы контроля четности. В таком состоянии счетчика импульсы, появляющиеся на входе 14 сложения, через элемент 12 передаются на вход триггера 0-разряда четности (т.е. счетчик считает без изменения режима), а импульс с входа 15 вычитания через элемент 13 поступает на дополнительные входы управляющих каскадов элементов И 5-8 сспадения разрядов счета. В последнем случае происходит реверсирование счета с одновременным уменьшением содержимого счетчика на еДиницу-о В режиме вычитания логический уровень сигнала блока 9 контроля, четности меняется на обратный (будет логический нуль). Поэтому открытые в режиме сложения ступени И элементов 12 и 13 закрываются, а закрытые открываются. В этом режиме направление прохождения импульсов сложения и вычитания меняются местами по сравнению с режимом сложения. Импульсы с входа 14 сложения передаются через элемент 13 на реверсирование счета, а с входа 15 - на продолжение счета. В предлагаемом счетчике импульсы сложения и вычитания поступают на входы 14 и 15 в виде логических единиц и передаются на разряды счетчика проинвертированными в коммутаторе 10. Поэтому счетчик регистрирует не появление импульсов на входах, а их исчезновение. Такая организация счета позволяет переместить переходные процессы и паузы между входными импульсами, когда входной коммутатор заперт, и тем самым устранить состязания в счетчике.

Реверсивный циклический счетчик, содержащий триггер в разряде четности и п .триггеров, вход Кс1ждого из которых соединен с выходом элемента И в каждом разряде, первый вход которого соединен с единичным выходом тригг ера данного разряда и с входом блока контроля четности, остальные входы элемента И соединены с нулевыми выходами предыдущих триггеров, отличающийся тем, что, с целью восстановления режима счета при слу- .

тор, первый выход которого соединен с входом триггера разряда четности, второй - с дополнительными входами п элементов И, а вход соединен с выходом блока контроля четности.

Источники информации, принятые во внимание при экспертизе

1. Гитис Э. И. и др. Построение

счетчиков в циклическом коде , Вопросы радиоэлектроники , вып. 13, серия XII, 1962, с. 200, рис, 1.

2. Авторское свидетельство СССР № 470077, KJi. Н 03 К 23/00, 02.01.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля реверсивного счетчика | 1973 |

|

SU444186A1 |

| Цифровой дискриминатор средней частоты | 1985 |

|

SU1293835A1 |

| Генератор рекуррентной последовательности с самоконтролем | 1988 |

|

SU1550502A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| Устройство для контроля правильности электрического монтажа | 1984 |

|

SU1216782A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для программного управления | 1983 |

|

SU1160367A1 |

Авторы

Даты

1979-04-25—Публикация

1976-04-12—Подача