.Изобретение относится к аналргодискретному преобразованию и может быть использовано в аналого-цифровых преобразователях, предназначенных для измерения изменяющихся напряжений, обеспечивая при сравнительно простой технической реализации и высоком быстродействии повышенную достоверность результатов преобразования. Известен аналого-цифровой преобразователь с коррекцией динамических погрешностей по основному авт.св. № 660240, содержащий блок сравнения, включающий узлы с авнения, вычитания и сложения, генератор тактовых импульсов , распределитель тактовых импульсов, регистр кода, бЛок кодирования старших разрядов, логический блок коррекции, два преобразователя кода в напряжение, регистр-г)еверсивный счетчик, элементы 2, 2И-2ИЛИ, элементы совпадения, элементы НЕ и связи между нимирЗ К недостаткам этого устройства, как и других известных аналого-цифровых преобразователей с Коррекцией динамических погрешностей, относится низкая достоверность результатов преобразования и отсутствие обобщенного Параметра работоспособности устройст ва. Отсутствие контроля по текущим измерениям требует дополнительного времени и оборудования для проведения периодического контроля. Необходимость обобщенных параметров, характеризукяцих работоспособность отдельных узлов радиоэлектронных комплексов, определяется требованиями технической диагностики таких комплексов. Цель изобретения - повышение достоверности результатов преобразования. Поставленная цель достигается тем, что в аналого-цифровой преобразователь с коррекцией динамических погрешностей, содержащий основной и дополнительный преобразователи кода в напряжение с подключенными поразрядно регистрами, распределитель тактовых импульсов, вход которого соединен с выходом генератора тактовых импульсов , а его выходы соединены с входами разрядов регистров основного и дополнительного преобразователей кода в напряжение, аналоговый выход первого из которых соединен с входом перврго блока сравнения и первыми

ШодаииdjiokcJB су№1Й1р)б1ания и вычи- тания, а аналоговый выход дополни- , тельно соединен со вторыми входами блоков суммирования и вычитания, при этЬм выход последнего подключен ко входу второго блока сравнения, а выход блока суммирования ко входу третьего блока сравнения, сигнальный вход которого соединен с входной клеммой и с сигнальными входами первого и второго блоков сравнения; а входы блока кодирования старших разрядов соединены с соответствующими входами логического блока коррекции и с выходами первого и третьего блоков сравнения нёпос редственно и через логический элемент НЕ с выходом втор6г6 Йлока сравнения и с другими входами логического блока коррекции, содтветствукицие выходы которого подключены к счетным входам и к вkoдaм установки нулей младших разрядов регистра основного преобразователя кода в напряжение,tвходы установки единиц старших разрядов которого соединены с соответствующими входами блока кодирования старлих разрядов и с входами установки единиц регистра дополнительного преобразователя кода в напряжение, причем соответствукяцие выходы блока кодирования старших разрядов соединены с входами 2К+1 установки нулей старших разрядов и с входами 2К установки единиц старшего разряда регистра основного преобразователя кода в напряжение(где К - натуральный ряд чисел), вес второго разряда которого -выбран равным весу младшего разряда регистра дополнительного преобразователя кода в напряжение, причем блок кодирования старших разрядов содержит логические элементы И и 2И-2ИЛИ, ра.вные числу старших разрядов регистра основного преобраэбвателя кода в напряжение, при этом соответствующие входы логических элементов 2И-2ИЛИ соединены с соответствующими входными клеммами и С(5 ёТЬрыми входами логических элементов И, первые входы которых подключены к входным клеммам, логический блок кот рёкцйй содержитло ический элемент НЕ и логические элементы И, входы которых соединены с сЬответст вуедими В1Сбдными клеммами и между собой, введен дополнительный элемент 2И-2ИЛИ,

входы элементов И подключены к старшему выходу распределителя тактовых импульсов а вторые к выходам второго и третьего блоков сравнения.

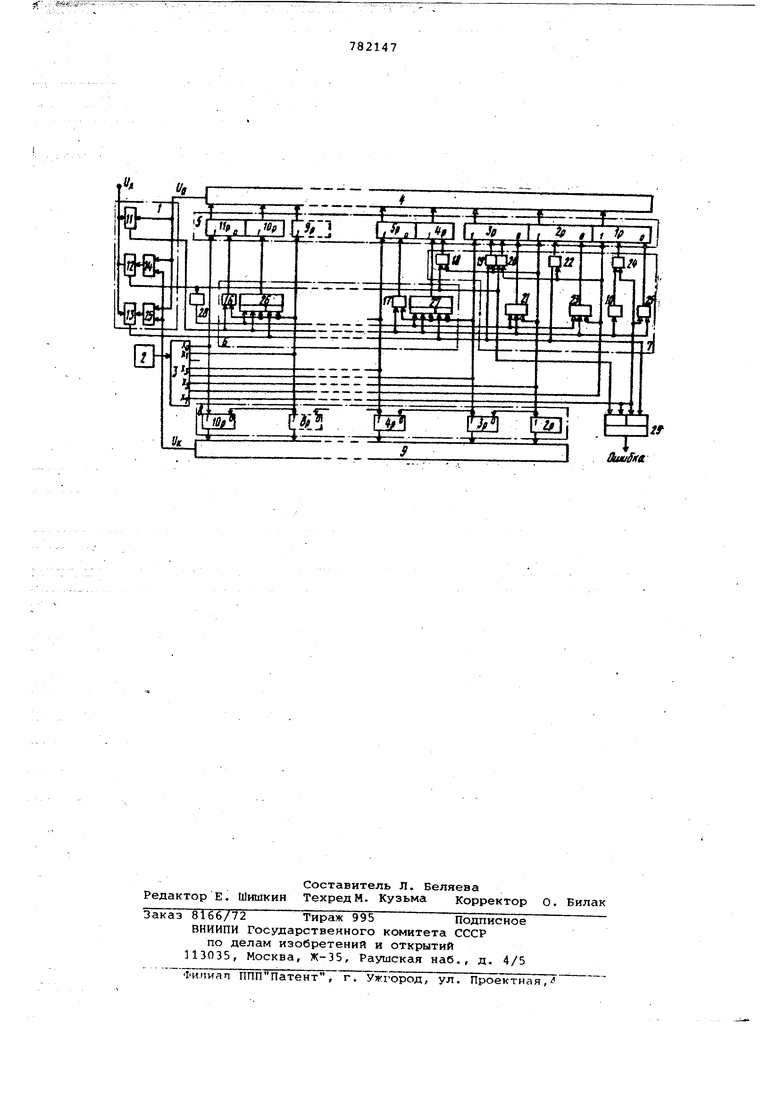

На чертеже представлена структурная схема аналого-цифрового преобразователя с коррекцией динамических погрешностей.

Устройство содержит., блок 1 сравнения, состоящий из элементов 11-13 сравнения и блоков 14 вычитания и 15 . сложения, генератор 2 тактовых импульсов, распределитель 3 тактовых им782147

пульсов, основной преобразователь 4 кода в Напряжение (ПКН), регистр-реверсивный счётчик 5, блок 6 .кодирования старших разрядов логический блок 7 коррекции, дополнительный pieгистр 8 кода и ПКН 9, логические элементы 2И-2ИЛИ 26 и 27, элементы Ьовпадения 16-25, элементы НЕ 10 и 28 и дополнительный элемент 2И-2ИЛИ.

Работа преобразователя ocsaцecтвляется следующим образом.

Импульсом XQ устанавливается начальное состояние. При этом старшие разряды регистров 5 и 8 устанавлийаются в единицы,все остальные разряды 5 регистров 5 иВ устанавливаются в нулевое положение (цепь установки нулей на чертеже не показана).Вес старшего разряда дополнительного ПКН соответствует весу младшего разряда из Q старшей пары разрядов основного регистра 5, т.е. разряду 10 основного ПКН. , ,

Элементы 11-13 сравнения вырабатывают сигналы 1, если , U,xUo-U. UX UO+UK, О, если . 5 , UX UO+UK.

Импульсами производится поразрядное уравновешивание .старших разрядов по два разряда за один такт, соответственно, lip и Юр, 9р и 8р, 0 7р и 6р, 5р и 4р.

Если в момент Х/ О через элемент 16 совпадения разряд 11 регистра 5 сбрасывается в нулевое состояние, если )р, то разряд 11 5 остается в единичном состоянии.

Импульсом Х разряд 10, младший из старшей пары разрядов регистра 5, устанавливается в единичное состояние через Элемент 2И-2ИЛИ 26 в слу. чае, если ) или .

Одновременно импульс Х,( устанавливает в .единичное состояние старший разряд следукяцей пары основного регистра 5, выключает старший разряд и 45 включает следующий по порядку разряд дополнительного регистра 8, вес которого соответствует весу младшего из пары определяемых в следующем такте разрядов основного ПКН, т.е. разряда 8. ,

Импульсом Х производится поразрядное уравновешивание разрядой 5 и 4, установка в единичное состояние разряда 3 регистра 5 и включение разсг ряда 3 дополнительного регистра .8.

На последних тактах Хг--Х происходит коррекция процесса поразрядного уравновешивания.

В момент действия Х напряжение U),; соответствует четырем единицам 60 младшего разряда. Если (in(i0 и

U;(, тр происходит коррекция на 4 единицы в сторону уменьшения, разряд 3 регистра 5 остается в единичном состоянии, так как элемент 21 65 совпадения -эвкрыт потенциалом с элемента НЕ 28 {отличие от ПКН без коррекции на + 4 единицы). ,

Импульс Xf проходит через элемент 18 совпадения на счетный вход вычитания в разряд 4 регистра 5 и уменьшает числов регистре на 8 единиц (отличие от ПКН без коррекции на -8 единиц, а результирующее отличие от ПКН без коррекции на - 4 единицы) .

Если и , то происходит коррекция на 4 единицы в сторону увеличения, так как элемент 21 закры потенциалом с элемента 11 сравнения, тогда импульс Х не проходит на вход установки нуля разряда 3, но проходи через элемент 19 на счетный вход 3 сложения регистра разряда 5 (отличие от ПКН без коррекции на +4 единицы). Если UgiUx UQ + U|, то коррекции не происходит. Импульс Х не проходит через элементы 21,19 и 18, так как имеются з.апрещающие потенциалы с элементов 11, 13 и 12 соответственно, разряд 3 регистра 5 остается в единичном состоянии.

Если UQ - и : и x-i и , то коррекции не происходит. Элементы 18 и 19 закрыты потенциалами с элементов 12 и 13 соответственно. Импульс Х проходит через элемент 21 совпадения и устанавливает разряд 3 регистра 5 в нулевое состояние.

Аналогично импульс Х производит коррекцию на +2 единицы младшего разряда в случае необходимос.Ти.

Импульсом Xg- в Дополнительном регистре 8 включается и остается включенным до конца измерения младший разряд. Имеющий равный вес с разрядом 2 основного регистра.

Последний импульс с распределителя Xf при устанавливает в нулевое состояние разряд 1 регистра, при поступает на счетный вход разряда 1 регистра 5 через элемент 24 и производит коррекцию на +1, Таким образом, импульс XY изменяет число в регистре 5 на +1 единицу.

на выходе элемента 29 выделяется импульс ошибки, если в момент действия импульса Х U отличается от Uo более, чем на две единицы младЕиего разряда. При UK импульс Ху проходит через правый элемент и элемента 29, при (i через левый элемент И, Uj при этом соответствует двум единицам младшего разряда,

Следовательно, в момент действия импульса Х- схема самоконтроля фик0сирует в случае исправной работы отклонение кода от истинного значения Ux не более чем на две единицы младшего разряда, а импульс Х приближает код к истинному значению еще на 5 единицу.

Таким образом происходит преобразование напряжения в код с коррекцией динамических ошибок и с самоконтролем без увеличения времени преобразования на самоконтроль.

0

Использование предложенного устройства позволяет повысить достоверность результатов преобразования,при этом аналого-цйфрювой преобразователь получает обобщенный параметр-сигнал

5 ошибка, по которому можно судить о работоспособности преобразователя,

Формула изобретения

Аналого-цифровой преобразователь с коррекцией динамических погрешностей по авт. ев, 660240, отличающийся тем, что, с целью повышения достоверности результатов контроля, введен дополнительный элемент 2И-2ИЛИ,первые вхоДы элементов И подключены к стариему выходу распределителя тактовых импульсов, а вторые к выходам второго и третьего блоков сравнеиий.

Источники инфс рмаций, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 660240, кл, Н 03 К 13/17, 01,08,76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU330538A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1091331A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Г. Г. ЖИВИЛОБ; ::-.:;B::^ji03MAfl'1!^'а:гни кя,;^^'^?-кАЯ'Ч.'г. | 1972 |

|

SU324705A1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

Авторы

Даты

1980-11-23—Публикация

1979-01-24—Подача