Изобретение относится к вычислительной технике и предназначено для построения устройств для решения задач математической физики, описываемых дифференциальными уравнениями в частных производных.

Цель изобретения - повышение точности решения.

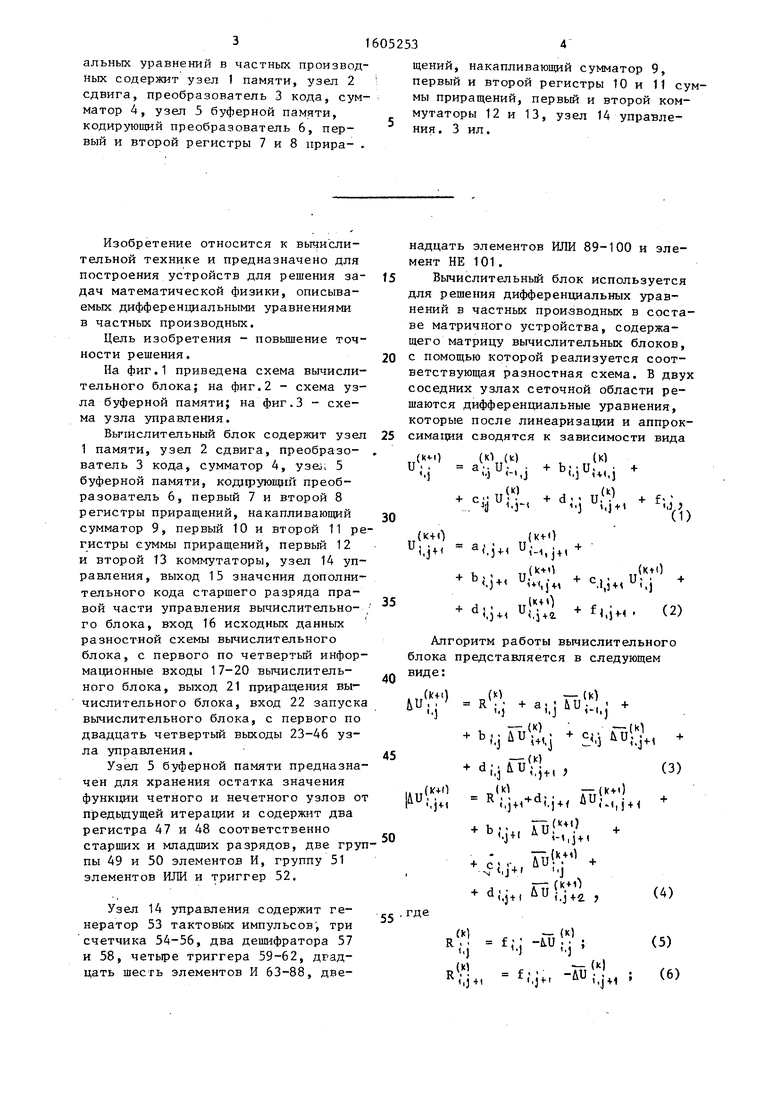

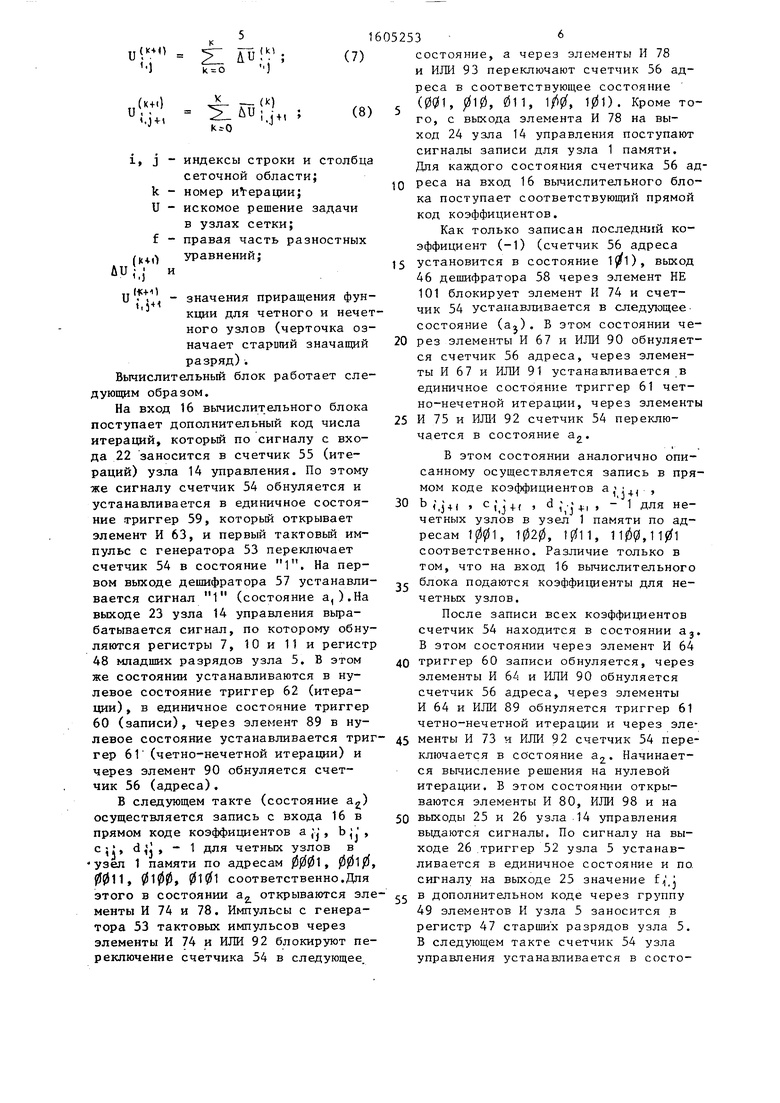

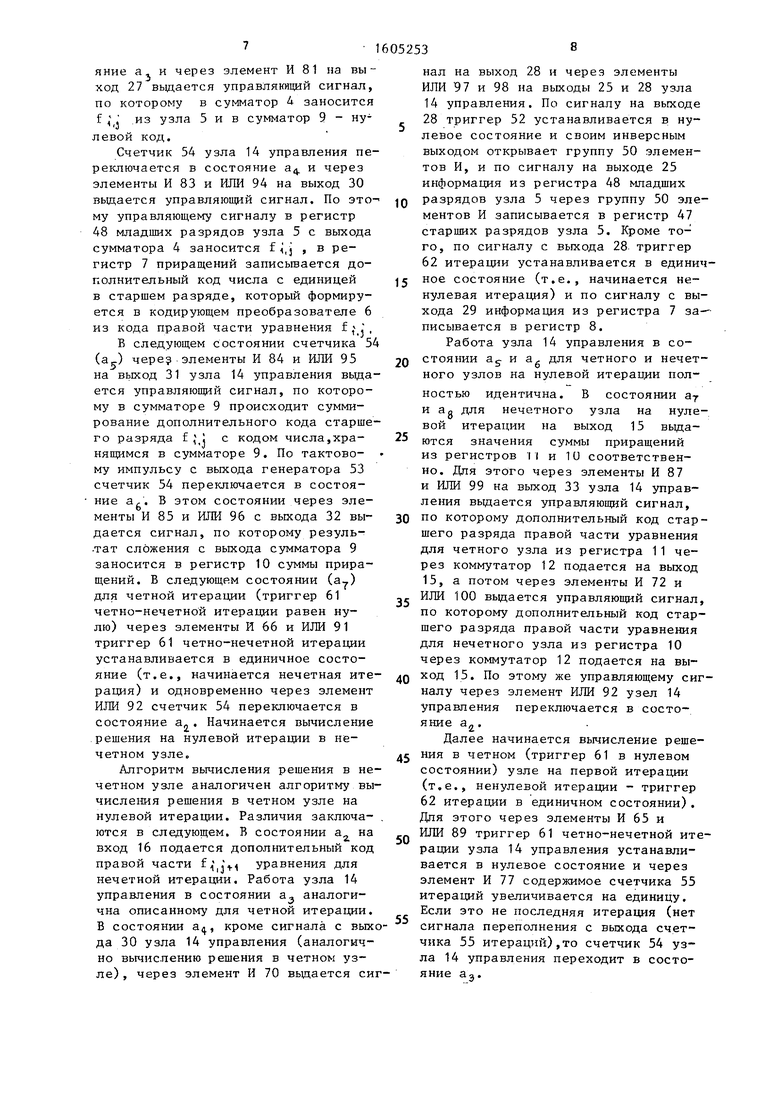

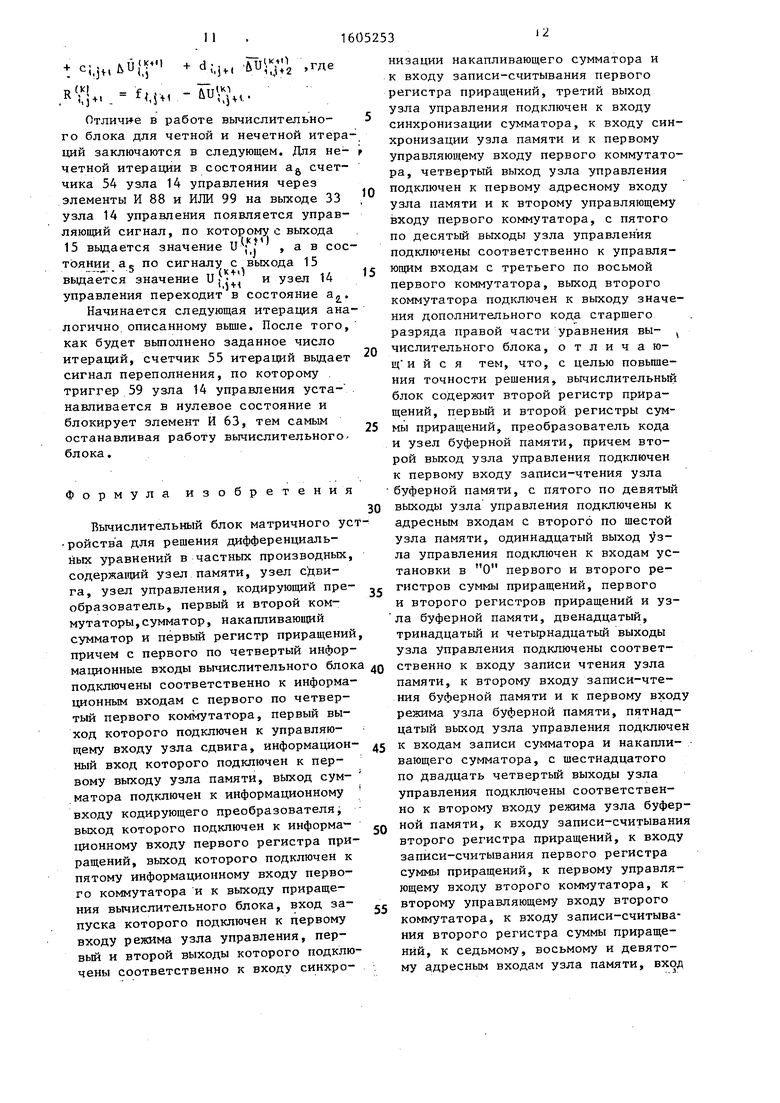

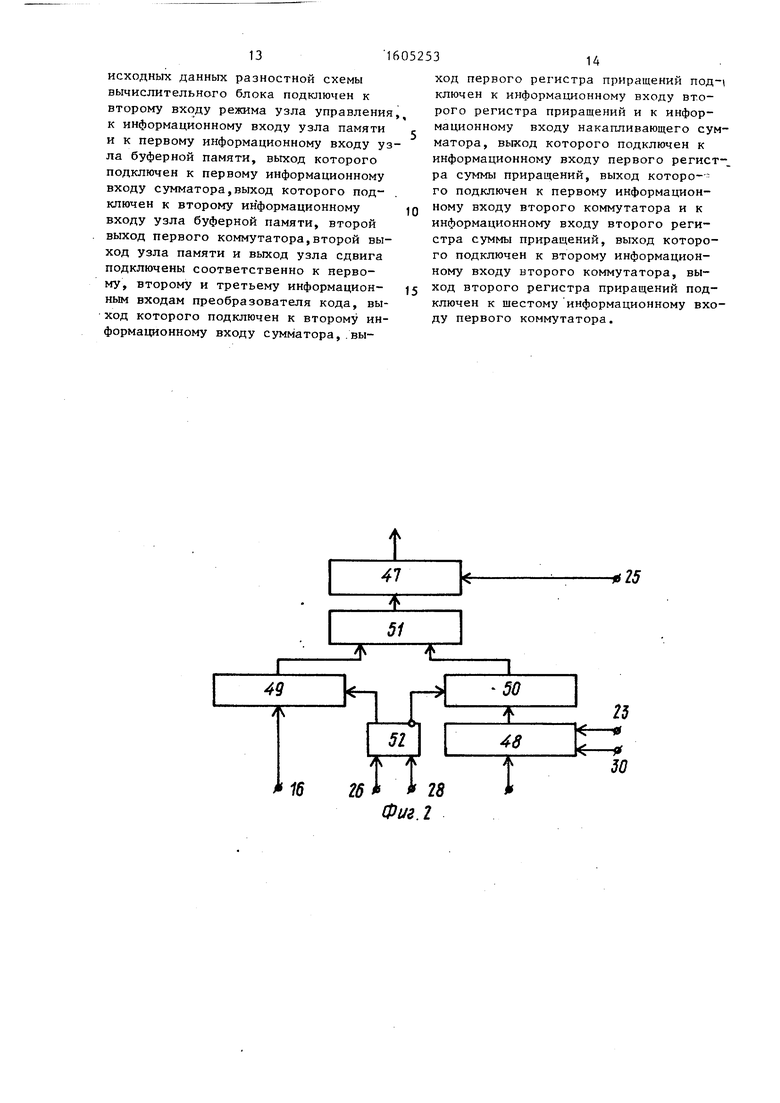

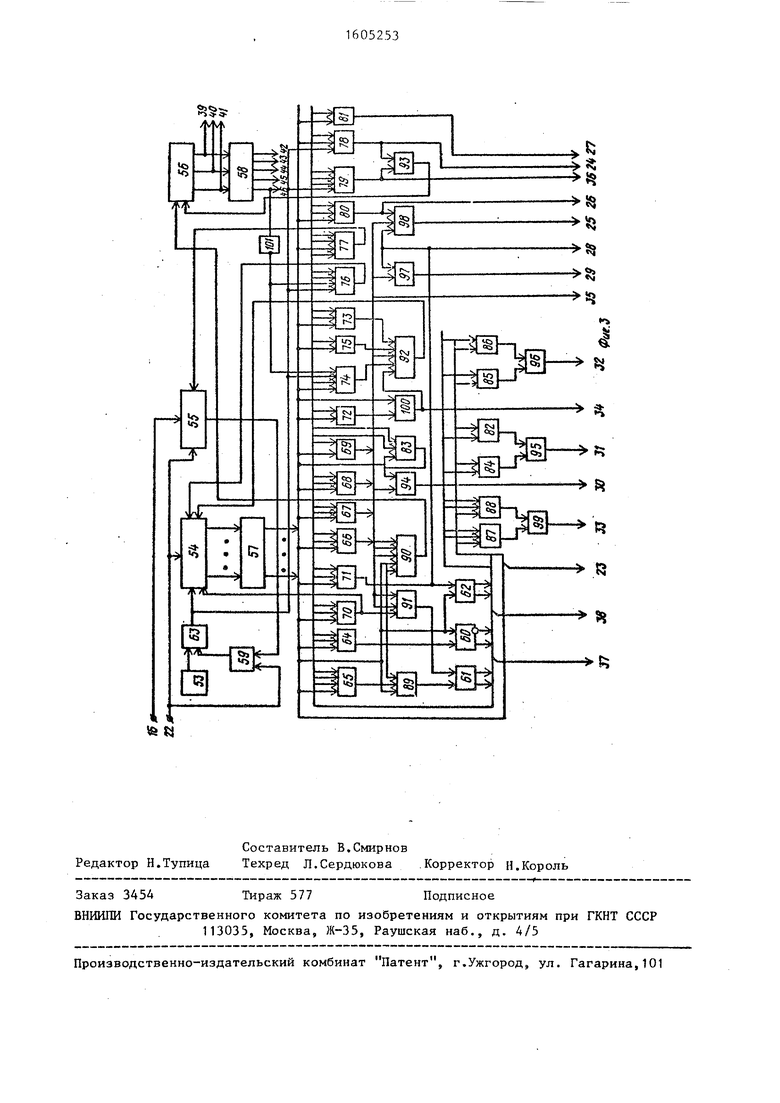

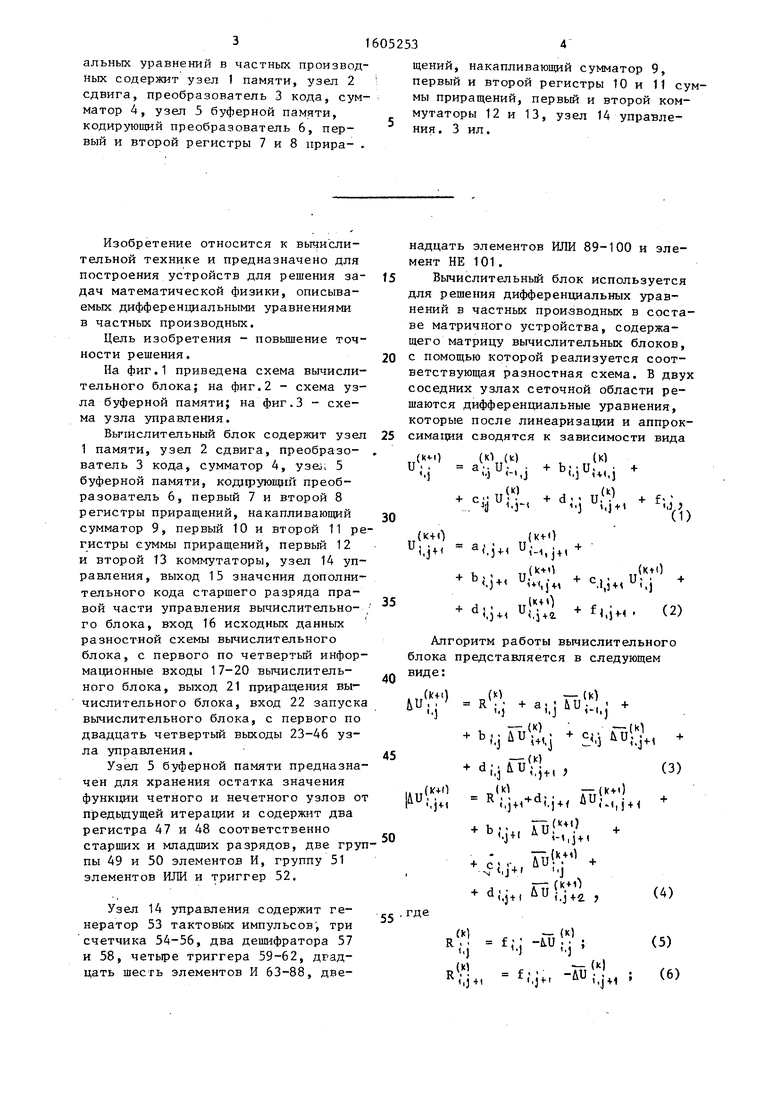

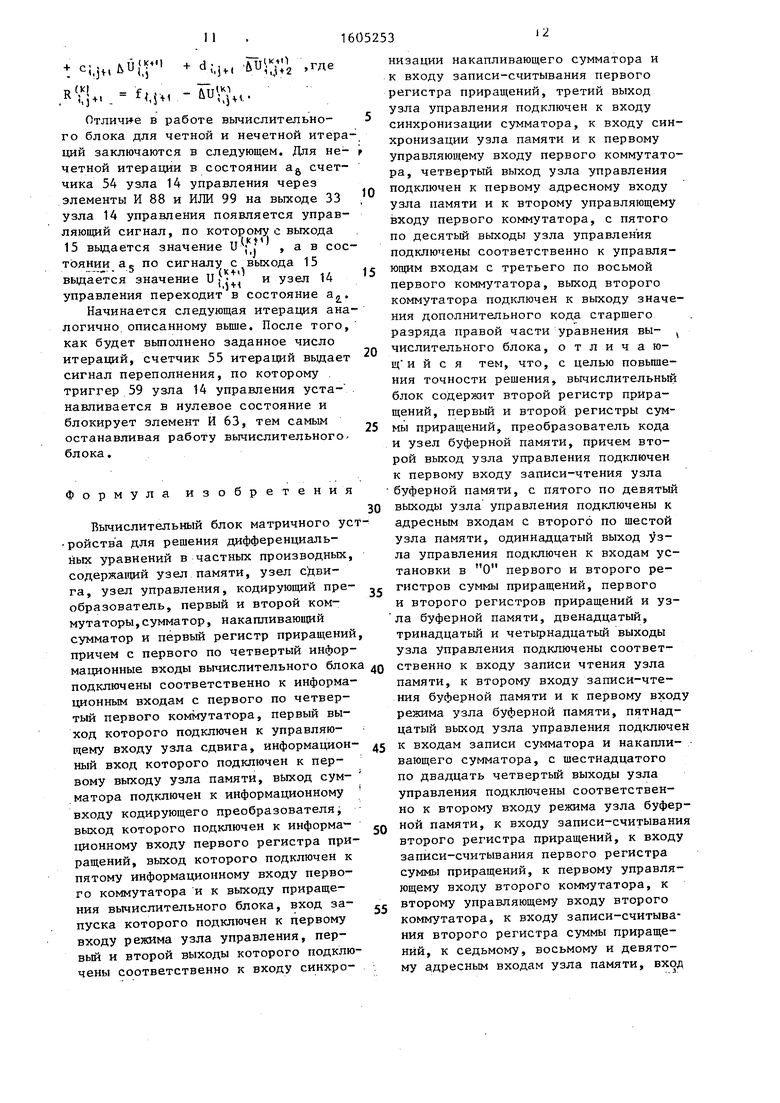

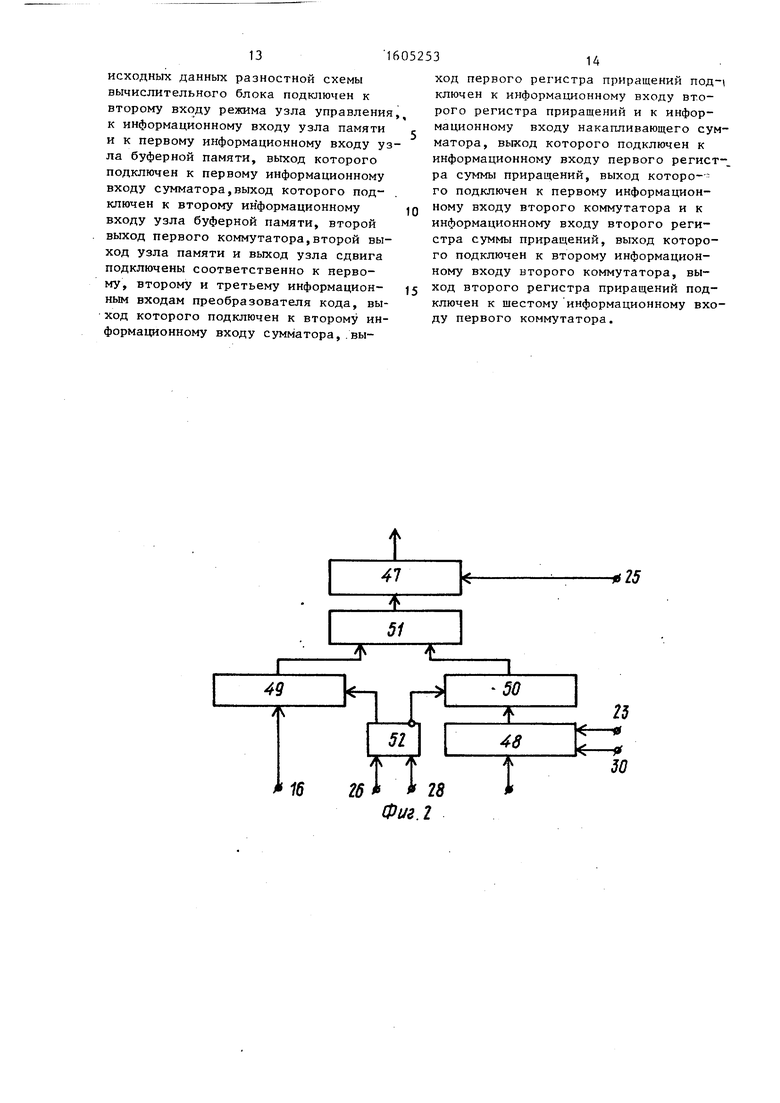

На фиг.1 приведена схема вычислительного блока; на фиг.2 - схема узла буферной памяти; на фиг.3 - схема узла управления.

Вьгшслительный блок содержит узел 1 памяти, узел 2 сдвига, преобразо- ватель 3 кода, сумматор 4, узео1 5 буферной памяти, кодирующий преобразователь 6, первый 7 и второй 8 регистры приращений, накапливающий сумматор 9, первый 10 и второй 11 регистры суммы приращений, первый 12 и второй 13 коммутаторы, узел 14 управления, выход 15 значения дополнительного кода старшего разряда правой части управления вычислительно- го блока, вход 16 исходных данньпс разностной схемы вычислительного блока, с первого по четвертый информационные входы 17-20 вычислительного блока, выход 21 приращения вычислительного блока, вход 22 запуска вычислительного блока, с первого по двадцать четвертый выходы 23-46 узла управления.

Узел 5 буферной памяти предназначен для хранения остатка значения функции четного и нечетного узлов от предьщущей итерации и содержит два регистра 47 и 48 соответственно старших и младших разрядов, две груп пы 49 и 50 элементов И, группу 51 элементов ИЛИ и триггер 52.

Узел 14 управления содержит генератор 53 тактовьтх импульсов, три счетчика 54-56, два дешифратора 57 и 58, четыре триггера 59-62, дгад- цать шесть элементов И 63-88, две

надцать элементов ИЛИ 89-100 и элемент НЕ 101.

Вычислительньй блок используется

для решения дифференциальных уравнений в частных производных в составе матричного устройства, содержащего матрицу вычислительных блоков,

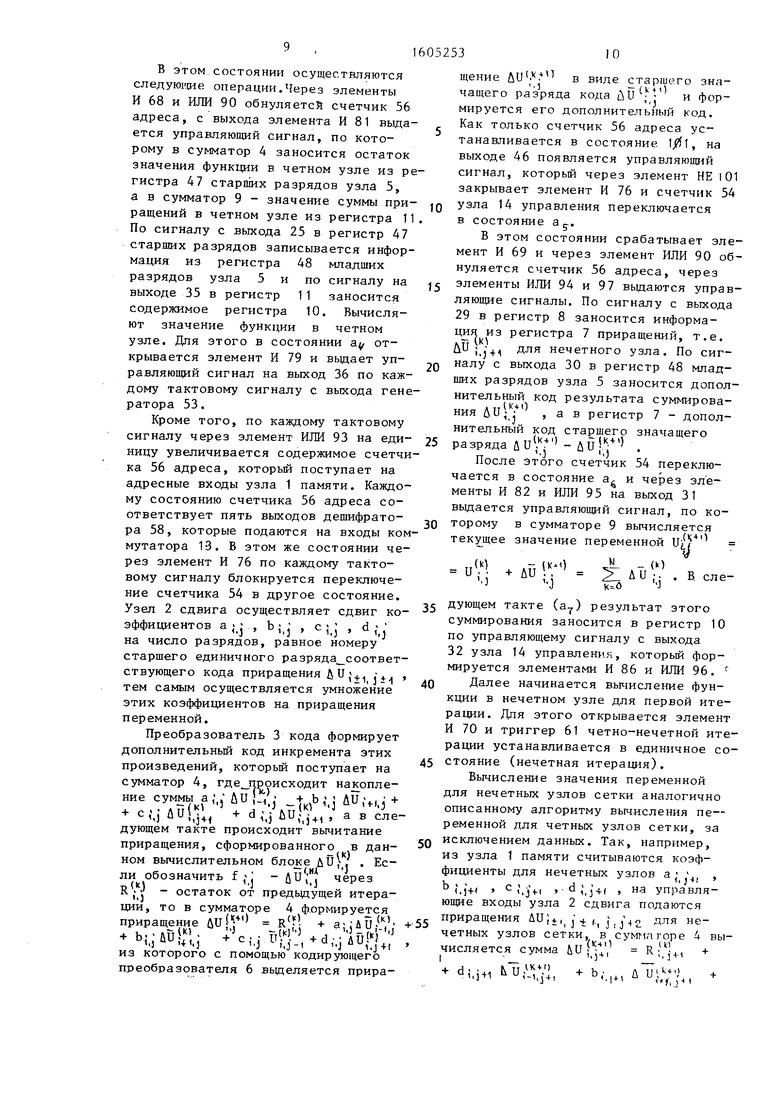

с помощью которой реализуется соответствующая разностная схема. В двух соседних узлах сеточной области решаются дифференциальные уравнения, которые после линеаризации и аппроксимации сводятся к зависимости вида

()(Kl (к)(к)

V -bj,u;,,j .

r.. -.

(к+О (ки)

i, t.J-n iH,j + (

ьф, , .o,.,,u,:; .

dl,,, + f.j,, . (2)

Алгоритм работы вычислительного блока представляется в следующем

40

,) ,.. .

.jUj ;,; -SjAuS j i

d,-&uV-, )(3)

- ч...

50

55

. где

b|.i., ruf-,

%ci.„ . ii.j,, ,

-ч„(K ... -(I

(,J+(

f..jf, -ли

t ,JM 5

(4)

(5) (6)

и ..

.

1, j k и f( ли,-, и

P

k o

(k)

ли

l+i

(8)

индексы строки и столбца

сеточной области;

номер итерации;

искомое решение задачи

в узлах сетки;

правая часть разностных

уравнений;

и

(K+il

i,

значения приращения функции для четного и нечетного узлов (черточка означает старший значащий разряд).

Вычислительный блок работает следующим образом.

На вход 16 вычислительного блока поступает дополнительный код числа итераций, которьш по сигналу с входа 22 заносится в счетчик 55 (итераций) узла 14 управления. По этому же сигналу счетчик 54 обнуляется и устанавливается в единичное состояние триггер 59, который открывает элемент И 63, и первый тактовьм импульс с генератора 53 переключает счетчик 54 в состояние 1. На первом выходе дешифратора 57 устанавливается сигнал 1 (состояние а,).На выходе 23 узла 14 управления вырабатывается сигнал, по которому обнуляются регистры 7, 10 и 11 и регистр 48 младших разрядов узла 5. В этом же состоянии устанавливаются в нулевое состояние триггер 62 (итерации) , в единичное состояние триггер 60 (записи), через элемент 89 в ну1605253 6

(7) состояние, а через элементы И 78

и ИЛИ 93 переключают счетчик 56 адреса в соответствующее состояние (001, , 011, t 101). Кроме того, с выхода элемента И 78 на выход 24 узла 14 управления поступают сигналы записи для узла 1 памяти. Для каждого состояния счетчика 56 реса на вход 16 вычислительного блока поступает соответствующий прямой код коэффициентов.

Как только записан последний коэффициент (-1) (счетчик 56 адреса

5 установится в состояние 1/1), выход 46 дешифратора 58 через элемент НЕ 101 блокирует элемент И 74 и счетчик 54 устанавливается в следующее- состояние (aj) . В этом состоянии че20 рез элементы И 67 и ИЛИ 90 обнуляется счетчик 56 адреса, через элементы И 67 и ИЛИ 91 устанавливается в единичное состояние триггер 61 четно-нечетной итерации, через элементы

25 И 75 и ИШ1 92 счетчик 54 переключается в состояние а,.

В этом состоянии аналогично описанному осуществляется запись в прямом коде коэффициентов а, ,, ,

30 b,,j + , , ., , d,. , - 1 для нечетных узлов в узел 1 памяти по адресам 1001, 1020, 1011, 11fi(/l,1101 соответственно. Различие только в том, что на вход 16 вычислительного

22 блока подаются коэффициенты для нечетных узлов.

После записи всех коэффициентов счетчик 54 находится в состоянии а. В этом состоянии через элемент И 64

40 триггер 60 записи обнуляется, через элементы И 64 и ИЛИ 90 обнуляется счетчик 56 адреса, через элементы И 64 и ИЛИ 89 обнуляется триггер 61 четно-нечетной итерации и через эле(8)

В этом состоянии аналогично описанному осуществляется запись в прямом коде коэффициентов а, ,, ,

b,,j + , , ., , d,. , - 1 для нечетных узлов в узел 1 памяти по адресам 1001, 1020, 1011, 11fi(/l,1101 соответственно. Различие только в том, что на вход 16 вычислительного

блока подаются коэффициенты для нечетных узлов.

После записи всех коэффициентов счетчик 54 находится в состоянии а. В этом состоянии через элемент И 64

триггер 60 записи обнуляется, через элементы И 64 и ИЛИ 90 обнуляется счетчик 56 адреса, через элементы И 64 и ИЛИ 89 обнуляется триггер 61 четно-нечетной итерации и через эле

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для преобразования Адамара цифровой последовательности | 1987 |

|

SU1462355A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

Изобретение относится к вычислительной технике и предназначено для построения устройств для решения задач математической физики, описываемых дифференциальными уравнениями в частных производных. Целью изобретения является повышение точности решения. Цель достигается тем, что вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных содержит узел 1 памяти, узел 2 сдвига, преобразователь 3 кода, сумматор 4, узел 5 буферной памяти, кодирующий преобразователь 6, первый и второй регистры 7 и 8 приращений, накапливающий сумматор 9, первый и второй регистры 10 и 11 суммы приращений, первый и второй коммутаторы 12 и 13, узел 14 управления. 3 ил.

левое состояние устанавливается триг- 45 менты И 73 и ИЛИ 92 счетчик 54 перегар 61(четно-нечетной итерации) и через элемент 90 обнуляется счетчик 56 (адреса).

В следующем такте (состояние а) осуществляется запись с входа 16 в прямом коде коэффициентов а ;j , b,., cj , d ;j , - 1 для четных узлов в узел 1 памяти по адресам 0001, 0010, (J011, 0100, 0101 соответственно.Для

ключается в состояние а. Начинается вьиисление решения на нулевой итерации. В этом состоянии открываются элементы И 80, ИЛИ 98 и на

50 выходы 25 и 26 узла 14 управления выдаются сигналы. Ло сигналу на выходе 26 триггер 52 узла 5 устанавливается в единичное состояние и по сигналу на выходе 25 значение f,| i

этого в состоянии а, открываются элементы И 74 и 78. Импульсы с генератора 53 тактовых импульсов через элементы И 74 и ИЛИ 92 блокируют переключение счетчика 54 в следующее.

менты И 73 и ИЛИ 92 счетчик 54 переключается в состояние а. Начинается вьиисление решения на нулевой итерации. В этом состоянии открываются элементы И 80, ИЛИ 98 и на

выходы 25 и 26 узла 14 управления выдаются сигналы. Ло сигналу на выходе 26 триггер 52 узла 5 устанавивается в единичное состояние и по сигналу на выходе 25 значение f,| i

в дополнительном коде через группу 49 элементов И узла 5 заносится в регистр 47 старших разрядов узла 5. В следующем такте счетчик 54 узла управления устанавливается в состояние я и через элемент И 81 на выход 27 выдается управлякиций сигнал, по которому в сумматор 4 заносится f; из узла 5 и в сумматор 9 - ну J

левой код.

Счетчик 54 узла 14 управления переключается в состояние а, и через элементы И 83 и ИЛИ 94 на выход 30 выдается управляющий сигнал. По это- му управляющему сигналу в регистр 48 младших разрядов узла 5 с выхода сумматора 4 заносится f ,j , в регистр 7 приращений записьшается дополнительный код числа с единицей в старшем разряде, который формируется в кодирующем преобразователе 6 из кода правой части уравнения f , . ,

В следующем состоянии счетчика 54 (а) чере элементы И 84 и ИЛИ 95 на вьгход 31 узла 14 управления выдается управляюшдй сигнал, по которому в сумматоре 9 происходит суммирование дополнительного кода старшего разряда f ,; с кодом числа,хранящимся в сумматоре 9. По тактовому импульсу с выхода генератора 53 счетчик 54 переключается в состоя- ние а,. В этом состоянии через элеО

менты И 85 и ИЛИ 96 с выхода 32 выдается сигнал, по которому резуль- -тат сложения с выхода сумматора 9 заносится в регистр 10 суммы приращений. В следующем состоянии (а) для четной итерации (триггер 61 четно-нечетной итерации равен нулю) через элементы И 66 и ИЛИ 91 триггер 61 четно-нечетной итерации устанавливается в единичное состояние (т.е., начинается нечетная итерация) и одновременно через элемент ИЛИ 92 счетчик 54 переключается в состояние а,. Начинается вычисление решения на нулевой итерации в нечетном узле.

Алгоритм вычисления решения в нечетном узле аналогичен алгоритму вы- числе1шя решения в четном узле на нулевой итерации. Различия заключа- ются в следующем. В состоянии а, на вход 16 подается дополнительный код правой части fi|i4i уравнения для нечетной итерации. Работа узла 14 управления в состоянии а аналогична описанному для четной итерации. В состоянии а/, кроме сигнала с выхода 30 узла 14 управления (аналогично вычислению решения в четном узле) , через элемент И 70 вьщается сиг

5

5

нал на выход 28 и через элементы ИЛИ 97 и 98 на выходы 25 и 28 узла 14 управления. По сигналу на выходе 28 триггер 52 устанавливается в нулевое состояние и своим инверсным выходом открывает группу 50 элементов И, и по сигналу на выходе 25 информация из регистра 48 maдшиx разрядов узла 5 через группу 50 элементов И записывается в регистр 47 старших разрядов узла 5. Кроме того, по сигналу с выхода 28 триггер 62 итерации устанавливается в единичное состояние (т.е., начинается ненулевая итерация) и по сигналу с выхода 29 информация из регистра 7 за--- писывается в регистр 8.

Работа узла 14 управления в соQ стоянии а. и а, для четного и нечетного узлов на нулевой итераиди полностью идентична. В состоянии а и ад для нечетного узла на нулевой итерации на выход 15 выдаются значения суммы приращений из регистров II и 10 соответственно. Для этого через элементы И 87 и ИЛИ 99 на выход 33 узла 14 управления вьщается управляющий сигнал, по которому дополнительный код старшего разряда правой части уравнения для четного узла из регистра 11 через коммутатор 12 подается на выход 15, а потом через элементы Е 72 и

J ИЛИ 100 выдается управляющий сигнал, по которому дополнительный код старшего разряда правой части уравнения для нечетного узла из регистра 10 через коммутатор 12 подается на вы0 ОД По этому же управляющему сигналу через элемент ИЛИ 92 узел 14 управления переключается в состояние а.

Далее начинается вычисление реше5 ния в четном (триггер 61 в нулевом состоянии) узле на первой итерации (т.е., ненулевой итерации - триггер 62 итерации в единичном состоянии). Для этого через элементы И 65 и ИЛИ 89 триггер 61 четно-нечетной итерации узла 14 управления устанавливается в нулевое состояние и через элемент И 77 содержимое счетчика 55 итераций увеличивается на единицу. Если это не последняя итерация (нет сигнала переполнения с выхода счетчика 55 итераций),то счетчик 54 узла 14 управления переходит в состояние а,.

0

0

5

В этом состоянии осуществляются следуювде операции.Через элементы И 68 и ИЛИ 90 обнуляетсй счетчик 5 адреса, с выхода элемента И 81 выдется управляющий сигнал, по которому в сумматор 4 заносится остато значения функции в четном узле из гистра 47 старших разрядов узла 5, а в сумматор 9 - значение суммы прращений в четном узле из регистра По сигналу с выхода 25 в регистр 4 старших разрядов записывается информация из регистра 48 младших разрядов узла 5 и по сигналу на выходе 35 в регистр 11 заносится содержимое регистра 10. Вычисляют значение функции в четном узле. Для этого в состоянии а, открывается элемент И 79 и вьщает управляющий сигнал на выход 36 по каждому тактовому сигналу с выхода генратора 53.

Кроме того, по каждому тактовому сигналу через элемент ИЛИ 93 на еди ницу увеличивается содержимое счетчка 56 адреса, которьм поступает на адресные входы узла 1 памяти. Каждому состоянию счетчика 56 адреса соответствует пять выходов дешифратора 58, которые подаются на входы комутатора 13. В этом же состоянии через элемент И 76 по каждому тактовому сигналу блокируется переключение счетчика 54 в другое состояние. Узел 2 сдвига осуществляет сдвиг коэффициентов ajj , b;,j , , на число разрядов, равное номеру старшего единичного разряда соответ ствующего кода приращения Л U j. .-. тем самым осуществляется умножение этих коэффициентов на приращения переменной.

Преобразователь 3 кода формирует дополнительнью код инкремента этих произведений, которьй поступает на

сумматор 4, где происходит натопле- ,uuL;..b,..juU,4,,. .)

-MUUIV - -d-juuJ-,,;a дующем такте происходит вычитание приращения, сформированного

в слев дан- . ЕСном вычислительном блоке ли обозначить -flu l J через R I .j остаток от предьщущей итерации, то в сумматоре 4 формируется приращение R + a:;AU/V;

.b,.,,i .- Г-й а и -;;

ИЗ которого с помощью кодирующего преобразователя 6 вьщеляется прира

10

o

5

0

5

зна10154

щение Ди .х Я в виде старшего чащего разряда кода и формируется его дополнительный код. Как только счетчик 56 адреса устанавливается в состояние , на выходе 46 появляется управляющий сигнал, который через элемент НЕ закрывает элемент И 76 и счетчик узла 14 управления переключается в состояние а.

В этом состоянии срабатывает элемент И 69 и через элемент ИЛИ 90 обнуляется счетчик 56 адреса, через элементы ИЛИ 94 и 97 вьщаются управ- ляюшле сигналы. По сигналу с выхода 29 в регистр 8 заносится информа- 7 приращений, т.е. 0-и

ция из регистра

ли J ,-j., для нечетного узла. По сигналу с выхода 30 в регистр 48 младших разрядов узла 5 заносится дополнительный код результата суммирования ли-j , а в регистр 7 - дополнительный код старшего значащего разряда йи Л - йи.) .

После этого счетчик 54 переключается в состояние а и через элементы И 82 и ИЛИ 95 на выход 31 вьщается управляющий сигнал, по которому в сумматоре 9 вычисляется текущее значение переменной U/Г

V

и

(К1

М

- Г

4- - )

в сле25

35

(а)

40

55

,

дующем такте U-,,; результат этого суммирования заносится в регистр 10 по управляющему сигналу с выхода 32 узла 14 управления, которьм формируется элементами И 86 и ИШ1 96. Далее начинается вычисление функции в нечетном узле для первой итерации. Для этого открывается элемент И 70 и триггер 61 четно-нечетной итерации устанавливается в единичное со- 45 стояние (нечетная итерация).

Вычисление значения переменной для нечетных узлов сетки аналогично описанному алгоритму вычисления пе- ременной для четных узлов сетки, за 50 исключением данных. Так, например, из узла 1 памяти считываются коэффициенты для нечетных узлов а b , ;,, . с

, , ,,J+

а ( , на управля- 2 сдвига подаются для не(,1-|-( - ,j4t ющие входы узла

приращения Ли; + , j ,. . четных узлов сетки, в cywiarope 4 вычисляется сумма Ьи , R;, ., +

IKit)

di,i.i , .b,

u U ,)

n} , ) (

rFiii tO

t i. M. .д

R

(K

,,j.. f 1 - (..

Отлич1 е в работе вычислительного блока для четной и нечетной итераций заключаются в следующем. Для не- четной итерации в состоянии а счетчика 54 узла 14 управления через элементы И 88 и ИЛИ 99 на выходе 33 узла 14 управления появляется управляющий сигнал, по которому с выхода 15 вьодается значение , а в состоянии а 5 по сигналу с выхода 15 выдае тся значение и узел 14 управления переходит в состояние а

Начинается следующая итерация аналогично, описанному выше. После того, как будет вьшолнено заданное число итераций, счетчик 55 итераций выдает сигнал переполнения, по которому триггер 59 узла 14 управления уста- навливается в нулевое состояние и блокирует элемент И 63, тем самым останавливая работу вычислительного- блока.

о р м у л а

изобретения

Вычислительный блок матричного уст- ойств а для решения дифференциаль- ньтх уравнений в частных производных, содержащий узел памяти, узел сдвига, узел управления, кодирующий пре- образователь, первый и второй коммутаторы, сумматор, накапливающий сумматор и первый регистр приращений, причем с первого по четвертый информационные входы вычислительного блока Q подключены соответственно к информационным входам с первого по четвертый первого коммутатора, первый выход которого подключен к управляющему входу узла сдвига, информацион- 45 ный вход которого подключен к первому выходу узла памяти, вьгход сум- j матора подключен к информационному входу кодирующего преобразователя,

выход которого подключен к ИНфОрМа- JQ

ционному входу первого регистра приращений, вькод которого подключен к пятому информационному входу первого коммутатора и к вьпсоду приращения вычислительного блока, вход за- пуска которого подключен к первому входу режима узла управления, первый и второй выходы которого подключены соответственно к входу синхро

5

0

Q 45

JQ

низации накапливающего сумматора и к входу записи-считывания первого регистра приращений, третий выход узла управления подключен к входу синхронизации сумматора, к входу синхронизации узла памяти и к первому управляющему входу первого коммутатора, четвертый выход узла управления подключен к первому адресному входу узла памяти и к второму управляющему входу первого коммутатора, с пятого по десятый выходы узла управления подключены соответственно к управляющим входам с третьего по восьмой первого коммутатора, выход второго коммутатора подключен к выходу значения дополнительного кода старшего разряда правой части уравнения вы- числительного блока, о т л и ч а ю- щ и и с я тем, что, с целью повьппе- ния точности решения, вычислительный блок содержит второй регистр приращений, первый и второй регистры суммы приращений, преобразователь кода и узел буферной памяти, причем второй выход узла управления подключен к первому входу записи-чтения узла буферной памяти, с пятого по девятый выходы узла управления подключены к адресным входам с второго по шестой узла памяти, одиннадцатый выход узла управления подключен к входам установки в О первого и второго регистров суммы приращений, первого и второго регистров приращений и уз- ла буферной памяти, двенадцатый, тринадцатый и четырнадцатый выходы узла управления подключены соответственно к входу записи чтения узла памяти, к второму входу записи-чтения буферной памяти и к первому входу режима узла буферной памяти, пятнадцатый выход узла управления подключен к входам записи сумматора и накапливающего сумматора, с шестнадцатого по двадцать четвертый выходы узла управления подключены соответственно к второму входу режима узла буферной памяти, к входу записи-считывания второго регистра приращений, к входу записи-считывания первого регистра суммы приращений, к первому управляющему входу второго коммутатора, к второму управляющему входу второго коммутатора, к входу записи-считывания второго регистра суммы приращений, к седьмому, восьмому и девятому адресным входам узла памяти, вход

исходных данных разностной схемы вычислительного блока подключен к второму входу режима узла управлени к информационному входу узла памяти и к первому информационному входу ула буферной памяти, выход которого подключен к первому информационному входу сумматора,выход которого подключен к второму ин формационному входу узла буферной памяти, второй выход первого коммутатора,второй выход узла памяти и выход узла сдвига подключены соответственно к первому, второму и третьему информационным входам преобразователя кода, выход которого подключен к второму информационному входу сумматора,.вы

ход первого регистра приращений под- ключен к информационному входу второго регистра приращений и к информационному входу накапливающего сумматора, выкод которого подключен к информационному входу первого регист- ра суммы приращений, выход которо- го подключен к первому информационному входу второго коммутатора и к информационному входу второго регистра суммы приращений, выход которого подключен к второму информационному входу второго коммутатора, выход второго регистра приращений подключен к шестому информационному входу первого коммутатора.

Зг

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство для решения дифференциальных уравнений | 1985 |

|

SU1277134A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1989-01-03—Подача