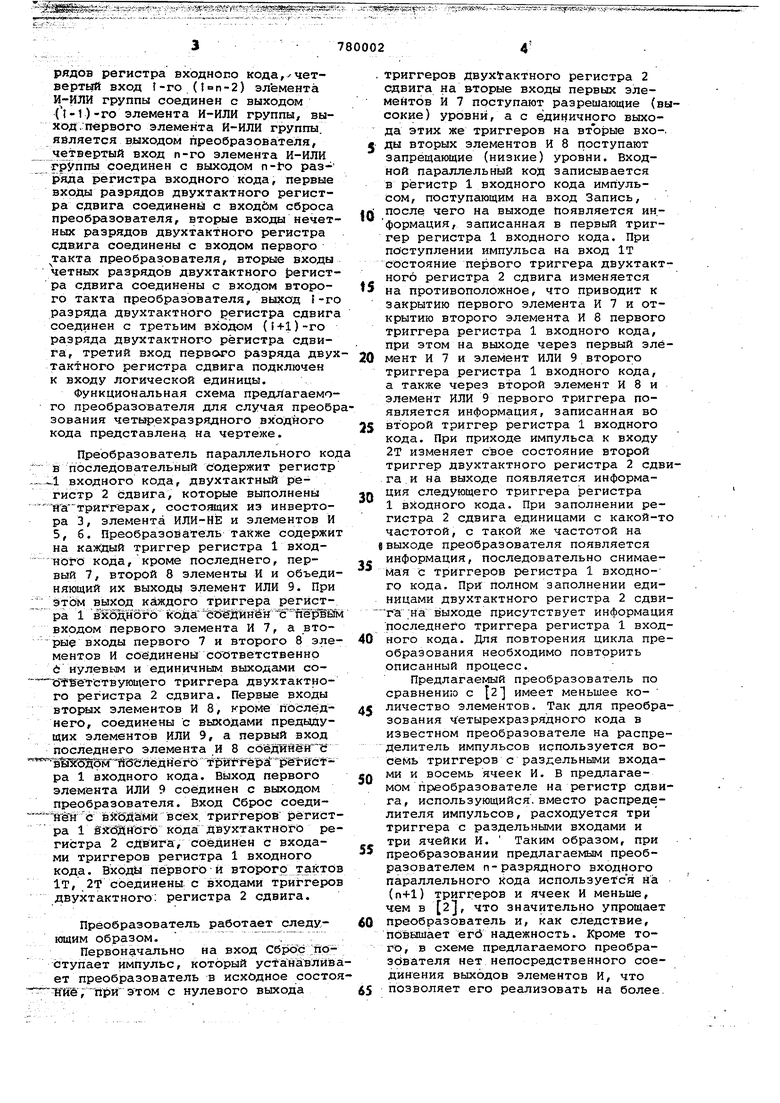

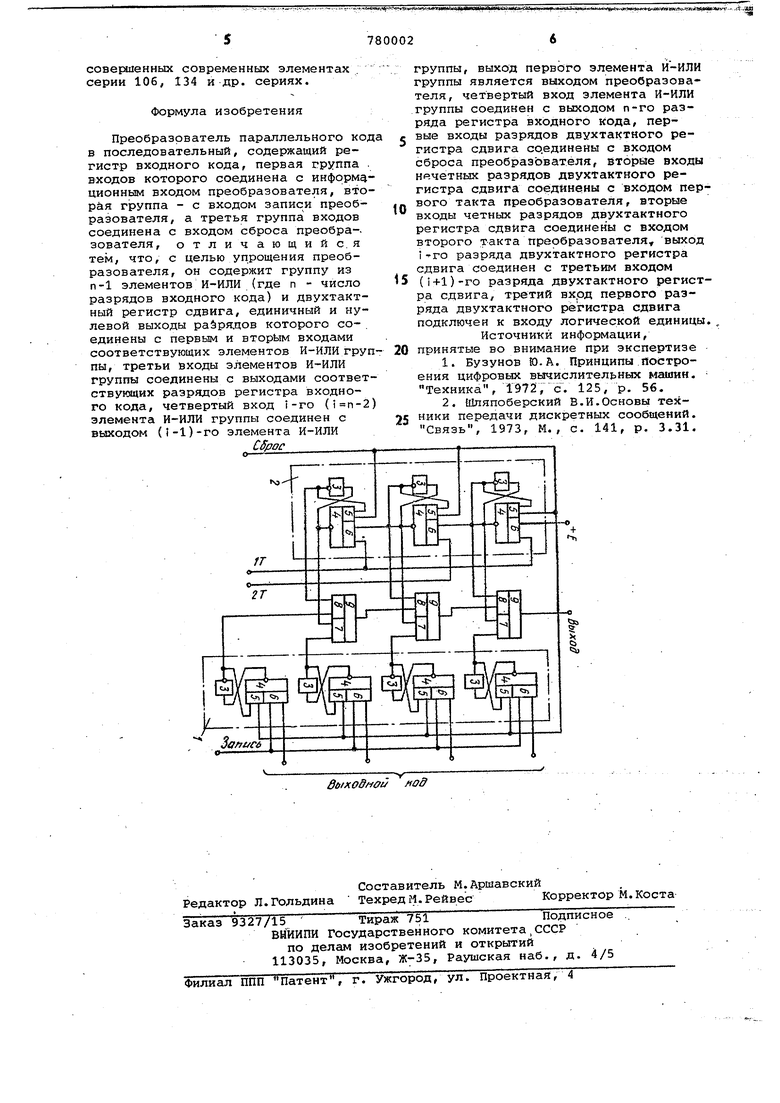

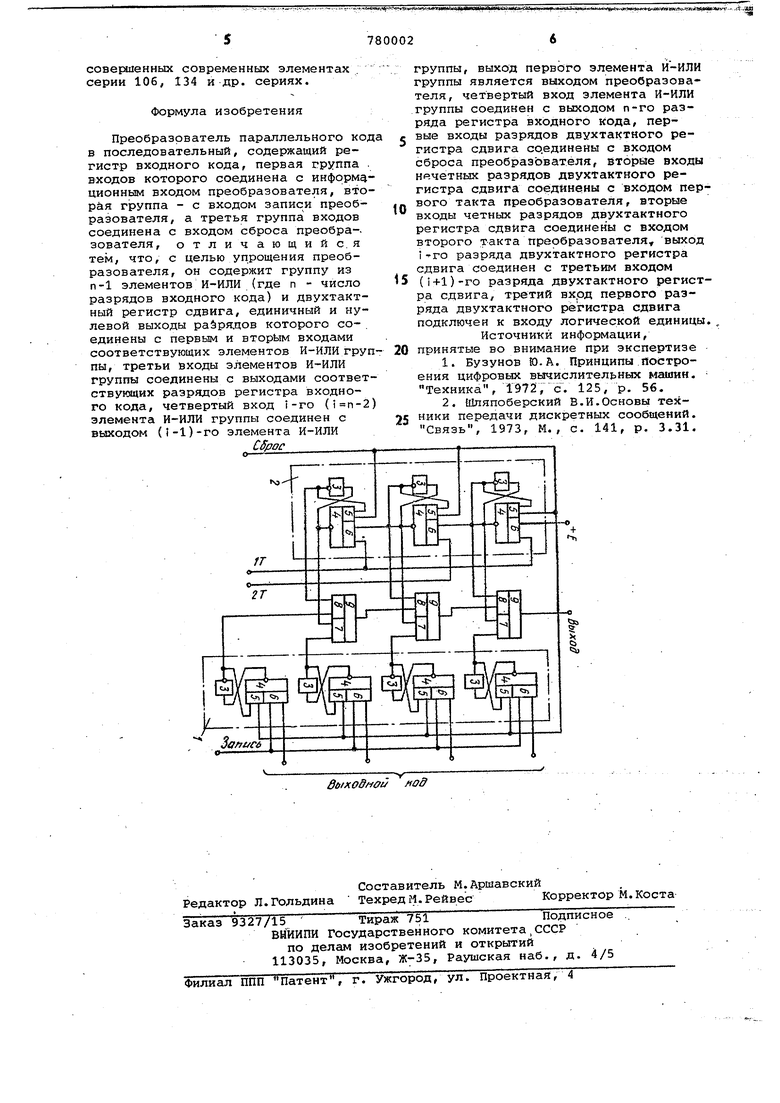

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении, преобразователей кодов и устройств сопряженмя. Известен преобразователь параллельного кода в последовательный l, содержащий триггеры, группу элементов ИЛИ, группу элементов И и группу элементов задержки, причем выходы предыдущих триггеров преобразователя соединены через элементы И, ИЛИ и элементы задержки с входами последую1иих триггеров. Недостаток этого преобразователя состоит в наличии элементов задержки , которые уменьшают быстродей ствие и надежность, а так же сужают функциональные возможности преобразователя. Наиболее близким решением данной задачи по технической сущности и схем ному решению является преобразователь параллельного кода в последова тельный 2, содержащий регистр вхо ного кода, первая группа входов которого соединена с информационным входом преобразователя, вторая груп па входов соединена с входом записи преобразователя, а третья группа вх дов соединена с входом сброса преобразователя. Кроме того, преобразо5аТ.ель содержит сдвиговый регистр и группу вентилей, входы которых соединены с выходами регистров, а выходы подключены к выходу преобразователя. Недостаток данного преобразователя состоит в его сложности. Целью изобретения является упрощение преобразователя. Поставленная цель достигается тем, что преобразователь параллельного кода в последовательный, содержащий регистр входного кода, первая группа входов которого соединена с информационным входом преобразователя, вторая группа - с входом записи преобразователя, а третья группа входов соединена с входом сброса преобразователя, дополнительно содержит группу из п-1 элементов И-ИЛИ, (где п - число разрядов входного кода) и двухтактный регистр сдвига, единичный, и нулевой выходы разрядов которого соедийены с первым и вторым входами соответствующих элементов И-ИЛИ группы третьи входы Элементов И-ИЛИ группы соединены с выходами соответствующих раз780002рядов регистра входного кода,Четвертьзй вход -го (f-n-2) элемента И-ИЛИ группы соединен о выходом 0-1)-го элемента И-ИЛИ группы выход, первого элемента И-ИЛИ группы, является выходом преобразователя, четвертый вход п-го элемента И-ИЛИ группы соединен с выходом раз рйда регистра входного кода, первые входы разрядов двухтактного регистра сдвига соединены с входбм сброса преобразователя, вторые входы нечет ных разрядов двухтактного регистра сдв.ига соединены с входом первого такта преобразователя, вторые входы четных разрядов двухтактного )егист ра сдвига соединены с входом второго такта преобразователя, выход {-г разряда двухтактного регистра сдвиг соединен с третьим входом (i +1)-го разряда двухтактного регистра сдвига, третий вход первсй о разряда дву тактного регистра сдвига подключен к входу логической единицы. Функциональная схема предлагаемого преобразователя для случая преобр зования четьфехразрядного входного кода представлена на чертеже. Преобразователь параллельного ко и последовательный содержит регистр „, входного кода, двухтактный регистр 2 сдвига, которые выполнены йа. ТрИГгврах, состоящих иэ инвертора 3, элемента ИЛИ-НЕ и элементов И 5, 6. Преобразователь также содержи на казедый триггер регистра 1 входного кода,кроме последнего, первый 7, второй 8 элементы И и объеди няющий их выходы элемент ИЛИ 9. При этом выход каждого триггера регистра 1 1Ш(а Шедйн1Г е 1теЩШ входом первого элемента И 7, а вторые входы первого 7 и второго 8 эле ментов И соединена соответственно U нулевым и единичным выходами со ШВетствукяцего триггера двухтактного регистра 2 сдвига. Первые входы вторых элементов ИВ, кроме последнего, соединены с выходами предыдущих элементов ИЛИ 9, а первый вход последнего элемента И 8 соёДййён е 1ШШ Г«еейёдНёго ра 1 входного кода. Выход первого элемента ИЛИ 9 соединен с выходом преобразователя. Вход Сброс соеди- №ё&С взгбдамй всех, триггер ов регист ра 1 ЙхШнОго кода двухтактного ре гистра 2 сД1зйга, соединен с входами триггеров регистра 1 входного кода. Входы первогои второго такто 1т, 2Т соединены, с входами триггеро двухтактного; регистра 2 сдвига. Преобразователь работает следующим образом. -..у Первоначально на вход Сбрюс поступает импульс, который уста;навлйв ет преобразователь в исходное состо Т1йё; прйэтом с нулевого выхода триггеров двухтактного регистра 2 сдвига на вторые входы первых элементов И 7 поступают разрешающие (высокие) уровни, а с единичного выхода этих же триггеров на вторые вхо-. ды вторых элементов И 8 поступают запрещающие (низкие) уровни. Входной параллельный код записывается в регистр 1 входного кода импульсом, поступающим на вход Запись, после чего на выходе появляется ин.формация, записанная в первый триггер регистра 1 входного кода. При поступлении импульса на вход 1т состояние первого триггера двухтактного регистра 2 сдвига изменяется на противоположное, что приводит к закрытию первого элемента И 7 и открытию второго элемента И 8 первого триггера регистра 1 входного кода, при этом на выходе через первый элемент И 7 и элемент ИЛИ 9 второго триггера регистра 1 входного кода, а также через второй элемент И 8 и элемент ИЛИ 9 первого триггера появляется информация, записанная во второй триггер регистра 1 входного кода. При приходе импульса к входу 2т изменяет свое состояние второй триггер двухтактного регистра 2 сдвига и на выходе появляется информация следующего триггера регистра 1 входного кода. При заполнении регистра 2 сдвига единицами с какой-то частотой, с такой же частотой на выходе преобразователя появляется информация, последовательно снимаемая с триггеров регистра 1 входного кода. При полном заполнении единицами двухтактного регистра 2 сдвиг ана выходе присутствует информация последнего триггера регистра 1 входного кода. Для повторения цикла преобразования необходимо повторить описанный процесс. Предлагаемый преобразователь по сравнению с 2 имеет меньшее количество элементов. Так для преобразования Четырехразрядного кода в известном преобразователе на распределитель импульсов используется восемь триггеров с раздельными входами и восемь ячеек И. В предлагаемом преобразователе на регистр сдвига, использующийся.вместо распределителя импульсов, расходуется три триггера с раздельными входами и три ячейки И. Таким образом, при преобразовании предлагаемым преобразователем п-разрядного входного параллельного кода используеТся йа (п+1) триггеров и ячеек И меньше, чем в 2, что значительно упрощает преобразователь и, как следствие, повышает егб надежность. Кроме того, в схеме предлагаемого преобразователя нет непосредственного соединения выходов элементов И, что позволяет его реализовать на более. соверяаенньк современных элементах серии 106, 134 и др. сериях. Формула изобретения Преобразователь параллельного ко в последовательный, содержащий регистр входного кода, первая группа входов которого соединена с информ ционным входом преобразователя, вто рая группа - с входом записи преобразователя, а третья группа входов соединена с входом сброса преобра-. зователя, отличающийс.я тем, что, с целью упрощения преобразователя, он содержит группу из п-1 элементов И-ИЛИ (где п - число разрядов входного кода) и двухтактный регистр сдвига, единичный и нулевой выходы райря,цов которого соединены с первым и BTopbiM входами соответствующих элементов И-ИЛИ гру пы, третьи входы элементов И-ИЛИ группы соединены с выходами соответ ствующих разрядов регистра входного кода, четвертый вход -го ( элемента И-ИЛИ группы соединен с выходом (i-l)-ro элемента И-ИЛИ

Buixod/iou /1Од

780002 группы, выход первого элемента Й-ИЛИ группы является выходом преобразователя, четвертый вход элемента И-ИЛИ группы соединен с выходом п-го разряда регистра входного кода, первые входы разрядов двухтактного регистра сдвига соединены с входом сброса преобразователя, вторые входы нечетных разрядов двухтактного регистра сдвига соединены с вхсэдом первого такта преобразователя, вторые входы четных разрядов двухтактного регистра сдвига соединены с входом второго такта преобразователя, выход iro разряда двухтактного регистра сдвига соединен с третьим входом (i+l)-ro разряда двухтактного регистра сдвига, третий вкрд первого разряда двухтактного регистра сдвига подключен к входу логической единицы. Источники информации, принятые во внимание при экспертизе 1.Бузунов Ю.А, Принципы йостроения цифровых вычислительных машин. Техника, 19727 с 125, р. 56. 2.Шляпоберский В.И.Основы техНИКИ передачи дискретных сообщений. Связь, 1973, М., с. 141, р. 3.31.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Преобразователь параллельного кода в последовательный | 1982 |

|

SU1075253A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

Авторы

Даты

1980-11-15—Публикация

1977-10-11—Подача