СКОРО элемента И, причем выход триггера соединен через элемент задержки с вторым входом третьего логического элемента И и непосредственно с первым входом четвертого логического элемента И, выход третьего логического элемента И - с входом управления блока логических элементов И, а выход четвертого логического элемента И - с первым управляющим входом управляемого делителя частоты, дополнительно введены счетчик, коммутатор, блок вычитания, регистр и блок выделения периода. Вход блока выделения периода соединен с шиной второго входного сигнала, первый выход подключен к второму входу первого логического элемента И, а второй выход - к второму управляющему входу управляемого делителя частоты и второму входу второго логического элемента И. При этом один вход регистра соединен с выходом управляемого делителя частоты и одним входом блока вычитания, второй вход которого подключен к входу триггера, а выход блока вычитания соединен с входом дополнительного счетчика, выходом подключенного к управляющему входу коммутатора, информационные входы которого соединены с шинами опорной частоты и ее гармоник, а выход - с вторым входом четвертого логического элемента И, причем второй вход регистра соединен с выходом третьего логического элемента И.

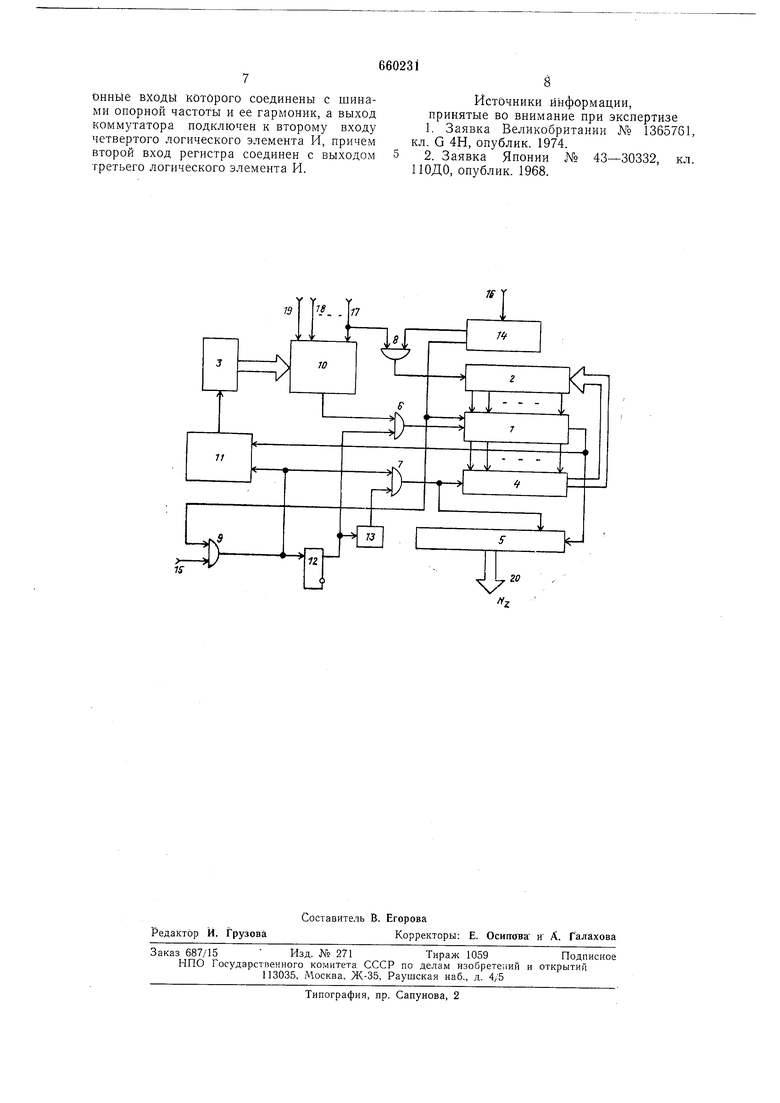

Структурная электрическая схема описываемого преобразователя приведена на чертеже.

Преобразователь содержит управляемый делитель 1 частоты, счетчики 2, 3, блок 4 логических элементов И, регистр 5, логические элементы И 6-9, коммутатор 10, блок 11 вычитания, триггер 12, элемент 13 задержки, блок 14 выделения периода.

На входные шины 15, 16 поданы входные сигналы, на шины 17, 18, 19 - опорная частота и ее гармоники.

Выходной код снимается с выхода 20.

Принцип работы устройства заключается в следующем.

Модулирующая зависимость устройства имеет вид

.К

ЛА -.

где Мг - выходной двоичный код; FX, Ру - входные частоты;

п - разрядность тока Л гРеально в устройстве вместо деления стот FX на Fy производится деление их риодов, т. е.

л..

где

Ту /.ру - период частоты Ру-, Тх I/FX - период частоты FX.

Для нормальной работы устройства должно выполняться условие

у макс - л МИН

В работе устройства можно выделить два этапа: преобразование периода Ту в двоичный код NT ; деление Ту на Тх, в результате чего определяется выходной код ЛгВ исходном состоянии счетчики 2, 3 и управляемый делитель 1 частоты установлены в «О, а в регистр 5 записана «1 во второй разряд. Кодирование периода Ту производится путем его заполнения высокой опорной частотой FO с помощью блока 14 выделения периода Ту, логического элемента И 8 и счетчика 2. Блок выделения периода, основу которого составляет двухразрядный суммирующий счетчик (не показан), функционирует таким образом, что на первом его выходе высокий потенциал появляется в течение отрезка времени между первым и вторым импульсами частоты Ру (т. е. в течение периода частоты), а на втором его выходе - после окончания первого периода той же ча-стоты. Поэтому с приходом первого импульса частоты Fy открывается логический элемент И 8 и в счетчике 2 накапливается код Лсч,1 пропорциональный периоду Ту, от О до величины . T.F,.

С приходом второго импульса частоты Ру логический элемент И 8 закрывается, прекращая поступление импульсов частоты FO в счетчик 2. На этом заканчивается процесс кодирования периода Ту.

Далее начинается второй этап: деление Ту на TX- Второй импульс частоты Ру, вызывая появление высокого потенциала на втором выходе блока 14 выделения периода, производит перепись кода N Ту из счетчика 2 в управляемый делитель 1 частоты и, кроме того, открывает логический элемент И 9.

Процесс деления состоит из повторяющихся одинаковых шагов: вычитание из делимого делителя и удвоение полученного остатка.

В предлагаемом устройстве деление реализуется следующим образом.

Первый (после открывания логического элемента И 9) импульс частоты РХ устанавливает триггер 12 в «1. При этом опорная частота Ро с коммутатора 10 через логический элемент И 6 начинает поступать на счетный вход управляемого делителя 1 частоты, списывая его содержимое от величины jVr до «О. К моменту прихода следующего (второго) импульса частоты РХ содержимое управляемого делителя I частоты Муяч, уменьшается на величину РоТх и становится равным

. -- , - T,,F,::. F, (Г, - Г,), где , - код остатка АТ Ту - Тх после первого шага деления.

Второй импульс частоты FX, пройдя логический элемент И 7, открывает блок 4 логических элементов И, через который код /УЛГ, переписывается в счетчик 2. Кроме того, этот же импульс записывает в младший разряд регистра 5. Итак, на первом шаге деления уже реализовано вычитание из делимого Ту делителя Т и получен остаток ATi. Так как делимое оказалось больше делителя, старшей цифре частного нрисвоено значение «1. Далее должно производиться вычитание Тх из удвоенного первого остатка 2АГ1. Делается это так. После переноса кода остатка , из управляемого делителя 1 частоты в счетчик 2 код Лудч продолжает описываться имнульсами частоты FO от величины , ДО нуля. В момент обнуления в него переписывается входной код. В данном устройстве входным является код, хранящийся в счетчике 2. Так как в счетчике 2 в этот отрезок времени хранится код , то он переписывается в управляемый делитель 1 частоты, и снова повторяется процесс уменьшения его содержимого () от величины N т, до нуля. Пришедший на этом отрезке времени третий импульс частоты FX, как и второй ее импульс, производит перепись из управляемого делителя

Iчастоты в счетчик 2 очередного (второго) остатка равного

N,T,2N,T.-T,.

Третий импульс частоты FX, как и второй импульс, записывает «1 в первый разряд регистра 5. Записанная ранее «1 к этому времени уже сдвигается во второй разряд регистра 5 с помощью импульса выходной частоты (), образовавшегося в момент обнуления управляемого делителя частоты. В рассмотренных двух шагах деления делимое (Ту и 2ATi) больше делителя 7. поэтому на каждом шаге очередной цифре частного присваивается значение «1 и проводится сдвиг кода частного влево. Пример выбран так, что удвоенный второй остаток меньше делителя, т. е.

2ДГ,Г,.

Поэтому после второго обнуления управляемого делителя частоты в третьем периоде частоты FX (т. е. после пришедших подряд двух импульсов удч) на выходе блока

I1вычитания появляется импульс, который записывается в счетчик 3. С коммутатора 10 поступает уже частота Fo/2, и поэтому следующий импульс частоты удч появляет ЛГ2

ся спустя время, равное- ,

0/2 т. е. 2А72. Так как в данном примере

ДГ, + АГ, + 2ЛГ,Г„

то на выходе блока 11 вычитания оказывается еще один импульс, который, изменив

код в счетчике 3, переключает коммутатор на выдачу частоты Foi2.

В соответствии с этим следующий период частоты /-удч будет в два раза больше

предыдущего. Если теперь ДГ2 + АГ2 -f + 2А72 + 4АГ2 TX, то процесс повторится. Иначе, как в данном примере, повторится ситуация, аналогичная первым двум щагам деления.

Предлагаемое устройство позволяет за счет небольшого усложнения схемы одновременно с выполнением операции деления произвести преобразование частоты в код. Использование его в качестве устройства

сопряжения частотных датчиков в ЦВМ дает возможность разгрузить последнюю от наиболее трудоемкой для нее операции деления.

Формула изобретения

Преобразователь отношения двух частот в код, содержащий управляемый делитель частоты, входы разрядов которого соединены с выходами разрядов счетчика, выходы

разрядов управляе.мого делителя частоты соединены с входами блока логических элементов И, выходы которого соединены с входами разрядов счетчика, информационный вход которого соединен с выходом первого логического элемента И, один вход которого подключен к шине опорной частоты, второй логический элемент И, один вход которого подключен к щине первого входного сигнала, а выход второго логического элемента И соединен с входом триггера и первым входом третьего логического элемента И, выход триггера соединен через элемент задержки с вторым входом третьего логического элемента И и непосредственио с первым входом четвертого логического элемента И, причем выход третьего логического элемента И соединен с входом управления блока логических элементов И, а выход четвертого логического элемента И соединен с первым управляющим входом управляемого делителя частоты, отличающийся тем, что, с целью повышения точности, в него дополнительно введены счетчик, коммутатор, блок вычитания, регистр

и блок выделения периода, вход которого соединен с шиной второго входного сигнала, первый выход блока выделения периода подключен к второму входу первого логического элемента И, а второй выход блока выделения периода соединен с вторым управляющим входом управляемого делителя частоты и вторым входом второго логического элемента И, при этом один вход регистра соединен с выходом управляемого делителя частоты и одним входом блока вычитания, второй вход которого подключен к входу триггера, а выход блока вычитания соединен с входом дополнительного счетчика, выход которого соединен с управляющим входом коммутатора, информационные входы которого соединены с шинами опорной частоты и ее гармоник, а выход коммутатора подключен к второму входу четвертого логического элемента И, причем второй вход регистра соединен с выходом третьего логического элемента И. Источники информации, принятые во внимание при экспертизе 1.Заявка Великобритании N° 1365761, кл. G 4Н, опублик. 1974. 2.Заявка Янонии № 43-30332, кл. ПОДО, опублик. 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Способ измерения мгновенных значений частоты электрического сигнала и устройство для его осуществления | 1987 |

|

SU1503022A1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления | 1983 |

|

SU1130860A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для управления шаговым двигателем | 1990 |

|

SU1693708A1 |

| Цифровой измеритель магнитной индукции | 1990 |

|

SU1755221A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для последовательного деления | 1986 |

|

SU1304017A1 |

Авторы

Даты

1979-04-30—Публикация

1976-04-22—Подача