00

о

00 О)

Изобретение относится к вычислительной технике -и может быть использовано в цифровых приборах для обработки результатов измерений, например, в составе Автоматических систем управления и контроля.

Известно устройство для деления, содержащее регистр делимого, регистр делителя, буферный регистр, ключ, входы которого подключены к первым выходам регистра делителя и буферного регистра соответственно, выход ключа подключен к входу счетчика частного и счетному входу триггера, блок фиксации окончания деления, вход которого подключен к выходу регистра делимого, распределитель импульсов, элемент ИЛИ и две группы поразрядных элементов И, последовательно соединенных один с другим 1J

Недостатками такого устройства являются малое быстродействие и низкая точность, связанная с возникновением сбоев при наличии в делителе нескольких находящихся рядом нулей.

Наиболее,близким по технической сущности к изобретению является устройств9 для деления, которое содержит коммутатор тактовых импульсов, счетчик делимого, блок фиксации окончания деления, счетчик делителя, блок задания кода делителя, счетчик частного и блок сравнения, состоящий из поразрядных узлов сравнения C2J.

Известное устройство обладает более высоким быстродействием, что достигается уменьшением числа счетных импульсов, необходимых для выполнения одного цикла вЬиитания, рав кого суммарному времени задерлу«и распространения сигналов в устройстве, определяющегося временной задержкой сигналов в блоке сравнения, обладающем наинизшим быстродействием по сравнению с другими структурными элементами устройства. Поэтому быстродействие известного устройства для деления ограничивается инерционностью входящего в него блока сравнения .

Цель изобретения - упрощение устройства и повышение его быстродействия.

Поставленная цель достигается тем, что в устройстве для деления, содержащем коммутатор, счетчик делимого, блок фиксации окончания деления, блок задания, кода делителя, многодекадный счетчик делителя, счетчик частного, причем информационный вход коммутатора соединен с тактовым входом устройства, а выходы соединены с входами разрядов счетчика делимого, выход которого подключен к входу блока фиксации окончания деления, вычитающие входы декад.многодекадного счетчика делителя подключены к выходам коммутатора, установочные входы декад многодекадного счетчика делителя подключены к выходам блока задания кода делителя, поразрядные выходы многодекадного счетчика делителя подключены к управляющим входам коммутатора, выход старшего разряда многодекадного счетчика делителя соединен с входом разрешения записи многодекадного счетчика делителя и с входом счетчика частного.

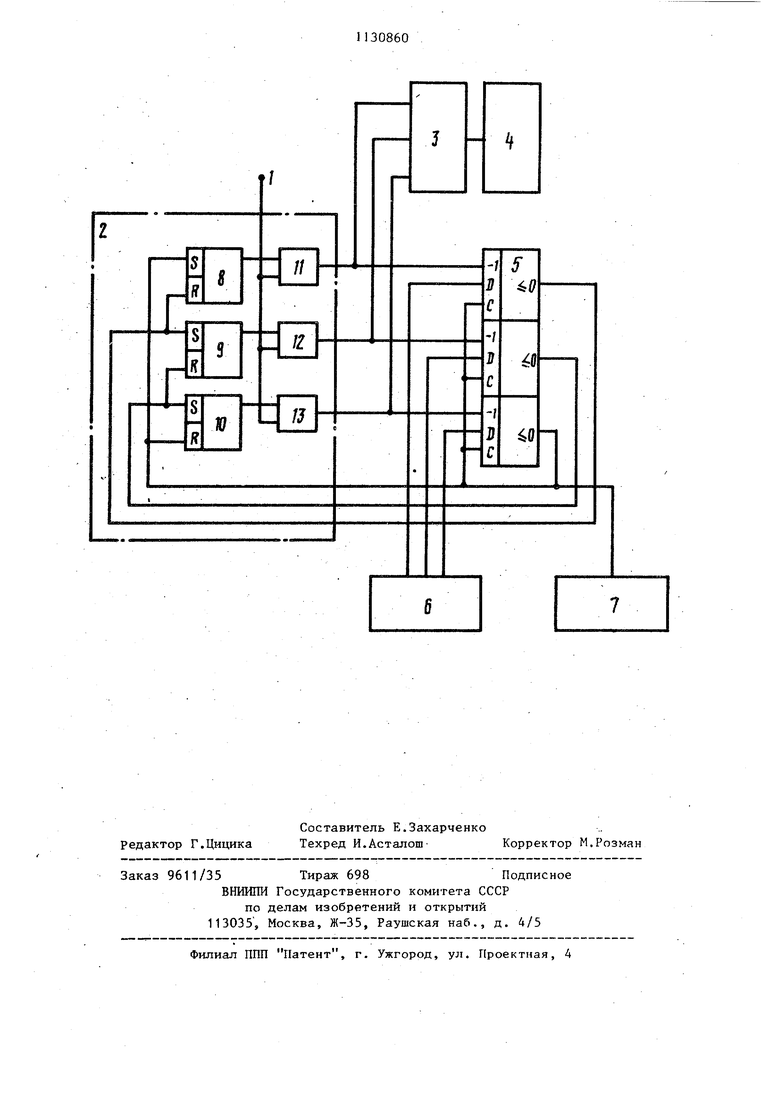

На чертеже приведена функциональная схема устройства.

Устройство для деления содержит тактовый вход 1, коммутатор 2, счетчик 3 делимого, блок 4 фиксации окончания деления, многодекадный счетчик 5 делителя, блок 6 задания кода делителя и счетчик 7 частного.

Коммутатор 2 состоит из нескольких, по числу разрядов, Р -триггеров 8-10 и стольких же элементов И 11-13, причем вход R первого (младшего) триггера 8 соединен с входом S второго триггера 9, вход R второго триггера 9 - с входом 5 третьего и так далее, а вход Е последнего (старшего) триггера соединен с входом S первого триггера. Выходы триггеров подключены к первым входам элементов И, вторые входы которых объединены и являются входом коммутатора, а R-входы триггеров являются управляющими входами коммутатора 2,. которые подключены к поразрядным выходам О многодекадного счетчика 5 делителя. Выход счетчика 3 подключен к блоку 4 фиксации окончания деления. Установочные входы многодекадного счетчика 5 соединены с блоком 6 задания кода делителя. Старший поразрядный выход О многодекадного счетчика 5 делителя подключен к входу разрешения записи этого же счетчика и к входу счетчика 7 частного, с которого снимается результат деления.

3 n

Устройство работает следующим образом.

В момент запуска устройства в счетчик 5 записывается код делителя с блока 6 задания кода делителя. Тактовые импульсы с входа 1 поступают на поразрядные входы счетчика.3 делимого и многодекадного счетчика 5 делителя через коммутатор 2. При этом тактовые импульсы проходят на выход того элемента И 11-13, соответствующий которому триггер 8-10 находится в состоянии логической 1V Например, тактовые импульсы поступают с выхода элемента 11 на входы первых разрядов счетчиков 3 и 5, которые работают в режиме вычитания. . Процесс продолжается до обнуления первого разряда счетчика. 5. В этот момент на первом выходе счетчика 5 появится сигнал, переключающий триггер 9 в состояние О, а триггер 10, в состояние 1. После этого тактовые импульсы проходят на вторые входы счетчиков 3 и 5. Так. устройство работает до тех пор, пока старший фазряд счетчика 5 не будет равен О. По сигналу с выхода старшего разряда счетчика 5 коммутатор вновь подключает к тактовому входу 1 первые разряды счетчиков 3 и 5, в счетчик 5 еще раз переписывается код делителя из блока задания кода делителя, и в счетчик 7 частного записьшается 1. На этом один цикл вычитания операции деления заканчивается, и начинается второй аналогичный цикл. Операция деления заканчивается после того, как счетчик 3 делимого достигает состояния О, которое фиксируется блоком 4.

В случае, когда один из разрядов делителя равен нулю, устройство

0.

работает следующим образом. После обнуления предьщущего, не равного нулю разряда счетчика делителя,. ; триггер следующего .разряда, н.апример 10, переключается в состояние 1. Соответствующийэтому триггеру элемент И 13 пропускает фронт тактового импульса с входа 1 на вход счетчика 5. Поскольку соответствующий разряд счетчика 5 равен нулю, то на его выходе -$ О одновременно с фронтом .тактового импульса (если пренебречь временем распространения) появляется сигнал, который переключает триггер 10 в состояние О, а триггер 11 - в состояние 1. Если и следующий разряд кода делителя равен нулю, то триггер 11 возвращается в состояние О. При этом счетчик 3 не должен срабатывать от импульсов, длительность которых меньще длительности тактовых импульсов. Предлагаемое устройство позволя-; ет производить операцию деления в

произвольной форме счисления: шестнадцатиричной, десятичной и другие в зависимости от конструкции применяемых блоков.

Многодекадный счетчик делителя

используется в режиме вычитания и в нем задействованы входы параллель-;ной записи информации и выходы переполнения О. Это существенно упрощае.т устройство и значительно

уменьшает время задержки распространения тактовых импульсов от тактог вого входы устройства до управляющий входов коммутатора.

Таким образом, предлагаемое устройство является более простым по сравнению с известными устройствами и обладает более высоким быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1979 |

|

SU809176A1 |

| Устройство для деления | 1980 |

|

SU903867A1 |

| Устройство для деления | 1983 |

|

SU1166100A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Устройство для деления | 1976 |

|

SU590738A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее коммутатор, счетчик делимого, многодекадный счетчик делителя, блок фиксации окончания деления, блок задания кода делителя, счетчик частного, причем информационный вход KOMMytaTopa соединен с тактовым входом устройства, а выходы соединены с входами разрядов счет-, чика делимого, выход которого подключен к входу блока фиксации окончания деления, отличающееся тем, что, с целью упрощения устройства, вычитающие входы декад многодекадного счетчика делителя подключены к выходам коммутатора, а установочные входы декгщ многодекадного счетчика делителя подключены к выходам блока задания кода делителя, поразрядные выходы многодекадного счетчика делителя подключены к управляющим входам ком3 мутатора, выход старшего разряда многодекадного счетчика делителя соединен с входом разрешения записи многодекадного счетчика делителя -и с входом счетчика частного.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления | 1980 |

|

SU903867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления | 1979 |

|

SU809176A1 |

| G 0.6 F 7/52, 1981 (прототип). | |||

Авторы

Даты

1984-12-23—Публикация

1983-09-28—Подача