(54) ЗАПОМИНАЮ ЦЕЕ УСТЮЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU905857A1 |

| Запоминающее устройство с последовательным доступом | 1982 |

|

SU1070606A2 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

Изобретение относнтся к вычислительной тех |нике и может быть использовано в запоАШианяцих устройствах вычислительных комплексов. Известны постоянные запоминающие устройства, содержащие ячейки запоминающих элементов и устройство управления, обеспечивающее поиск и считьгаание информации. Устройство управления состоит из регистра адреса, дешифратора и усилителей считывания. Дешифратор в соответствии с кодом адреса выбирает одну ячейку, а усилители считывания усиливают сигнал с этой ячейки до необходимого уровня Ц Недостаток известных устройств заключается в том, что обращение к ячейке запоминающих элементов и считьтание информации одновременно может происходить только по одному ад ресу. При обращении по разным адресам считывание информации происходит последовательно, при этом суммарное время выборки имеет боль шое значение. Наиболее близкой по технической сущности к предлагаемому устройству является матрица с пословной выборкой и одной ступенью дешифрации, содержащая запоминающие элементы входы которых подключены адресными шинами разных координат к выходу дешифратора адреса, а выходы соединены общей разрядной шиной, другой конец которой прнсоединен ко входу блока считьгаания. При поступлении на дешифратор адреса кода адреса возбуждается определенная шина дешифратора и состояние (логический О или 1) с запоминающего элемента, подключенного к данной адресной шине может быть сздтано по общей разрядной шине (2. Указанное устройство обеспечивает обращение к запоминающим элементам и считывание информации в каждый момент времени только по одному адресу. Обращаться и считывать информацию независимо и одновременно по разным ащксам невозможно. Таким образом общее время выборки по разным адресам имеет большое значение и определяется суммой времени выборки по каждому адресу отдельно. Цель изобретения - повышетше быстродействия устройства. Поставленная цель достигается тем, тго в запоминающее устройство, содержащее элементы

памяти, выходы которых подключены ко входу блока считывания, адресный блок, дополнительно введены дополнительные блоки считывания, входы которых подключены ко входу блока считьшания, аналоговые сумматоры, выходы которых подключены ко входам соответствующих элементов памяти, а одни входы - к выходам адресного блока, и дополнительные адресные блоки, выходы которых подключены к соответствующим другим входам аналоговых сумматоров.

Кроме того, элемент памяти содержит ключ, триггер и согласующий элемент, вход которого подключен к выходу ключа, а вход ключа подключен к выходу триггера.

Адресный блок содержит ключи, дешифратор и генератор, выход которого подключен к одним входам ключей, вторые входы ключей подключены к соответствующим выходам дещифратора.

Блок считьгеания содержит последовательно соединенные полосовой фильтр и преобразователь уровня.

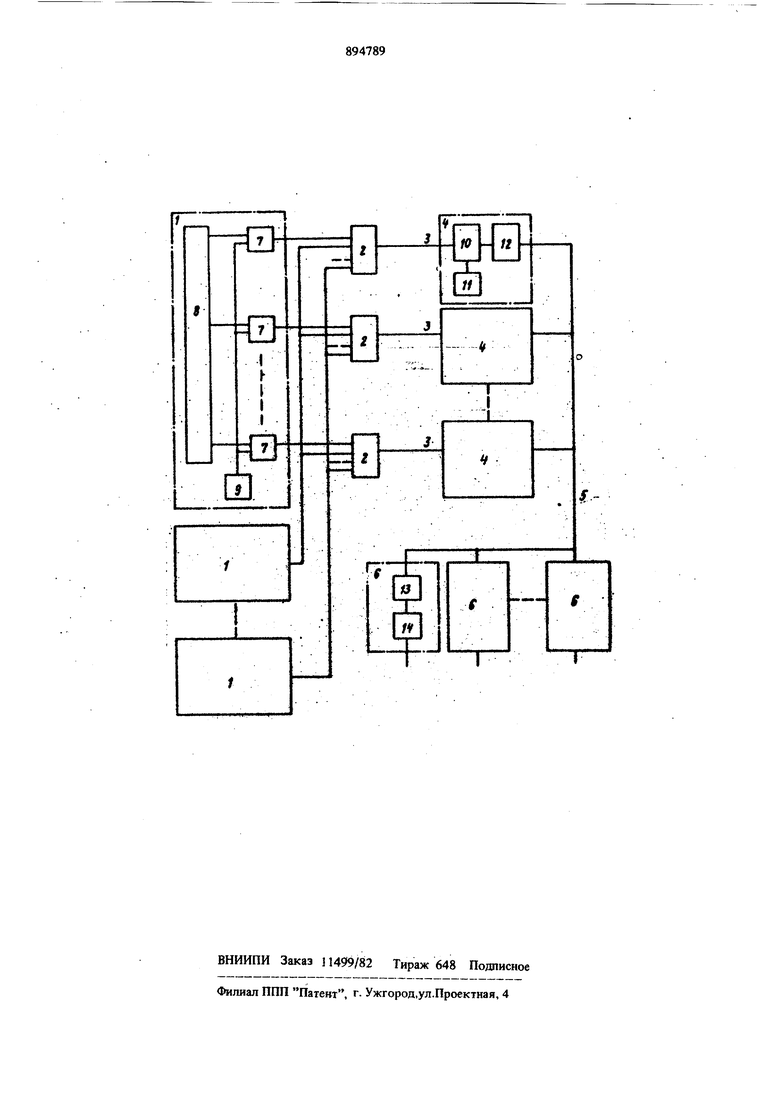

На чертеже представлена схема изобретения.

Устройство содержит адресные блоки 1, аналоговые сумматоры 2, адресные щины 3, элементы 4 памяти, общую разрядную шину 5, блоки 6 считывания, ключи 7, дешифратор 8, генератор 9, ключи 10, триггер 11, согласующие элементы 12, полосовые фильтры 13, преобразователи 14 уровня.

Устройство работает следующим образом.

В устройстве количество адресных блоков 1 равно количеству блоков 6 считьтания. В состав каждого адресного блока 1 входит генератор 9, причем значения частот генераторов 9 не равны между собой. В состав каждого блока 6 считывания входит полосовой фильтр 13, В полосе пропускания фильтров 13 находятся соответственно частоты генератора 9 блока адреса 1.

В режиме считывания при поступлении кодов адреса на вход одного или нескольких адресных блоков 1 на соответствующих выходных шинах каждого из них появляется гармоническое колебание с частотой, определяемой генератором 9 данного адресного блока 1. Эти колебания поступают на входы соответств)гющих аналоговых сумматоров 2 данной координаты, с входа которых сигналы, равные сумме входных гармонических колебаний, поступают на входы элементов 4 памяти. В зависимости от состояни опрашиваемых элементов 4 памяти входные синалы появляются или не появляются на их выходах. Сигналы с выходов опрапшваемых элементов 4 памяти через общую шину 5 поступают на входы блоков 6 считывания, в которых осуществляется частотная селекция входных сигналов и преобразование выделенных сигналов в логический уровень.

Одновременное независимое обращение по одному или разным адресам элементов 4 памяти путем подачи кодов адреса на определенное количество адресных блоков 1 и определение состояния этих элементов 4 на выходах блоков 6 считывания обеспечивается тем, что адресные блоки 1 вырабатывают сигналы опроса в виде гармонических колебаний разных частот, имеющих различный спектр, а выделение этих сигналов из общего происходит за счет частотного разделения системой полосовых фильтров

13в блоках 6 считывания. Каждому адреснолту блоку 1 соответствует один блок 6 считывания,

полосовой фильтр 13 которого пропускает сигналы с частотой задающего генератора 9 данного блока 1 адреса. Рассмотрим их работу более подробно.

При поступлении кода адреса на вход дешифратора 8 на одном из его выходов появляется логический сигнал, который поступает на первый вход соответствующего ключа 7. На вторые входы последнего поступает гармоническое колебание с частотой генератора 9. Логический сигнал с выхода дешифратора 8 является разрешающим для ключа 7 и гармоническое колебание появляется на его выходе, т.е. на выходной шине блока 1 адреса. Это

колебание поступает на вход аналогового сумматора 2 данной координаты и с его выхода по адресной шине 3 поступает на вход элемента 4 памяти. В триггере элемента 4 памяти хранится 1 бит информации. Если триггер находится в нулевом состояшш, то ключ 10 закрыт и на его выход никакие сигналы не проходят, а если в триггере II хранится логическая 1, то сигнал с последнего поступает на ключ Ш и держит его в открытом состоянии. В этом случае входной сигнал через

ключ 10 и согласующий элемент 12 поступает в общую разрядную шину 5, с выхода которой сигнал поступает на входы блоков 6 считывания, причем входом каждого блока 6 считывания является полосовой фильтр 13. Тар5 моническое колебание появится на выходе только того полосового фильтра, в полосе пропускания которого находится частота данного колебания, т.е. частота задающего генератора 9 блока адреса 1. Далее этот сигнал с выхода

0 фильтра 13 поступает на вход преобразователя

14уровня, на выходе которого он преобразуется в логический сигнал.

Использование в устройстве в качестве сигналов опроса гармонических колебаний разных 5 частот и их частотное разделение на выходе общей разрядной щины 5 позволяет одновременно обращаться и считывать информацию со многих элементов 4 памяти по негасимым кана|лам. При этом поле памяти, образованное из элеН ментов 4 памяти, остается обилим.

Применение предлагаемого запоминающего устройства позволяет существенно уменьшить общее время выборки, т.е. повысить его быстродействие, при этом отпадает необходимость поочередного обращения к общему полю памяти и установлению приоритета при обращении. Независимость обращения в предлагаемом устройстве позволяет использовать его в качестве запоминающего устройства в системах с больщим количеством конфликтных ситуащ1Й при обращении в память.

Формула изобретения

Источники информации,

принятые во внимание при экспертизе 1. Гольденберг Л. М, и др. Цифровые устройства на интегральных схемах в технике связи. М., Связь, 1979, с. 101.

Авторы

Даты

1981-12-30—Публикация

1980-04-03—Подача