Изобретение относится к вычислитель- ной и измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Цель изобретения - повышение быстродействия цифроаналогового преобразователя.

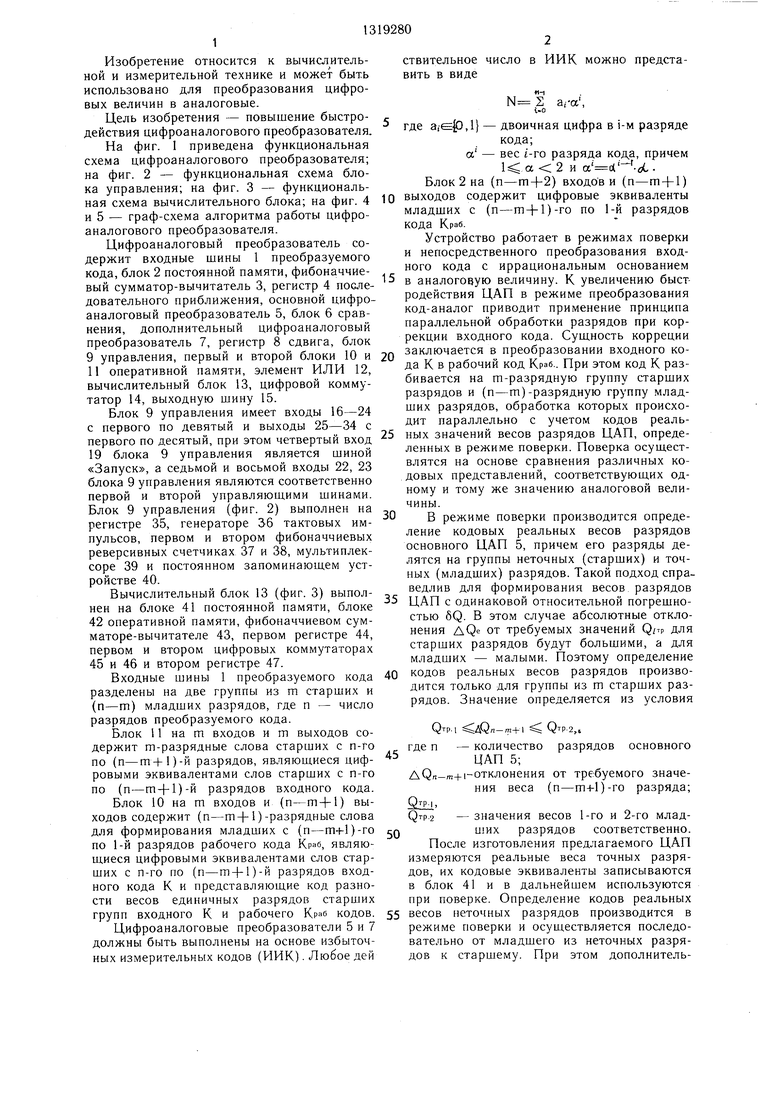

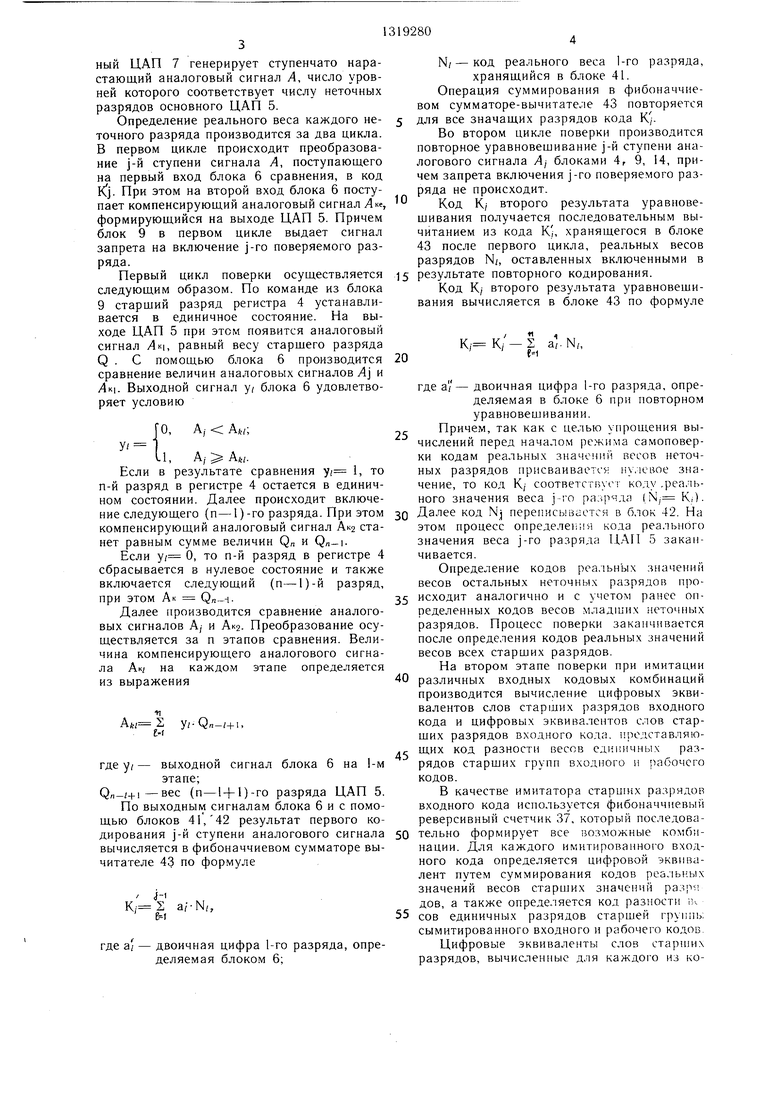

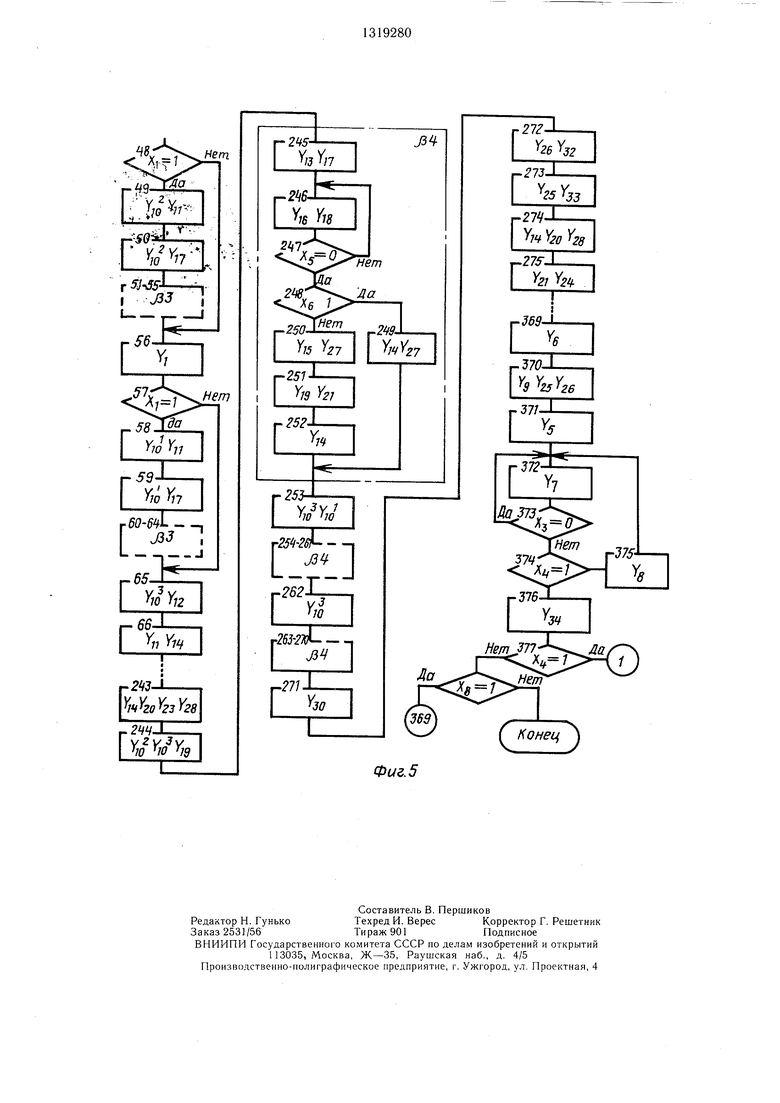

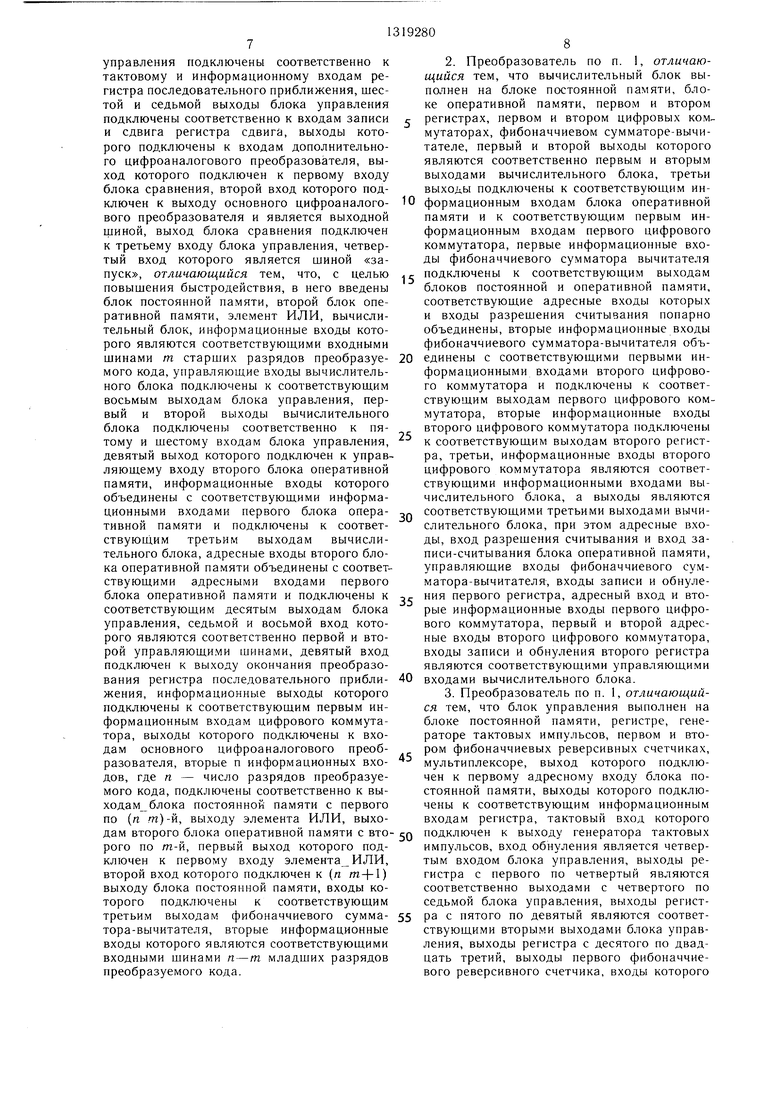

На фиг. 1 приведена функциональная схема цифроаналогового преобразователя; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема вычислительного блока; на фиг. 4 и 5 - граф-схема алгоритма работы цифро- аналогового преобразователя.

Цифроаналоговый преобразователь содержит входные шины 1 преобразуемого кода, блок 2 постоянной памяти, фибоначчие- вый сумматор-вычитатель 3, регистр 4 последовательного приближения, основной цифро- аналоговый преобразователь 5, блок 6 сравнения, дополнительный цифроаналоговый преобразователь 7, регистр 8 сдвига, блок 9 управления, первый и второй блоки 10 и 11 оперативной памяти, элемент ИЛИ 12, вычислительный блок 13, цифровой коммутатор 14, выходную шину 15.

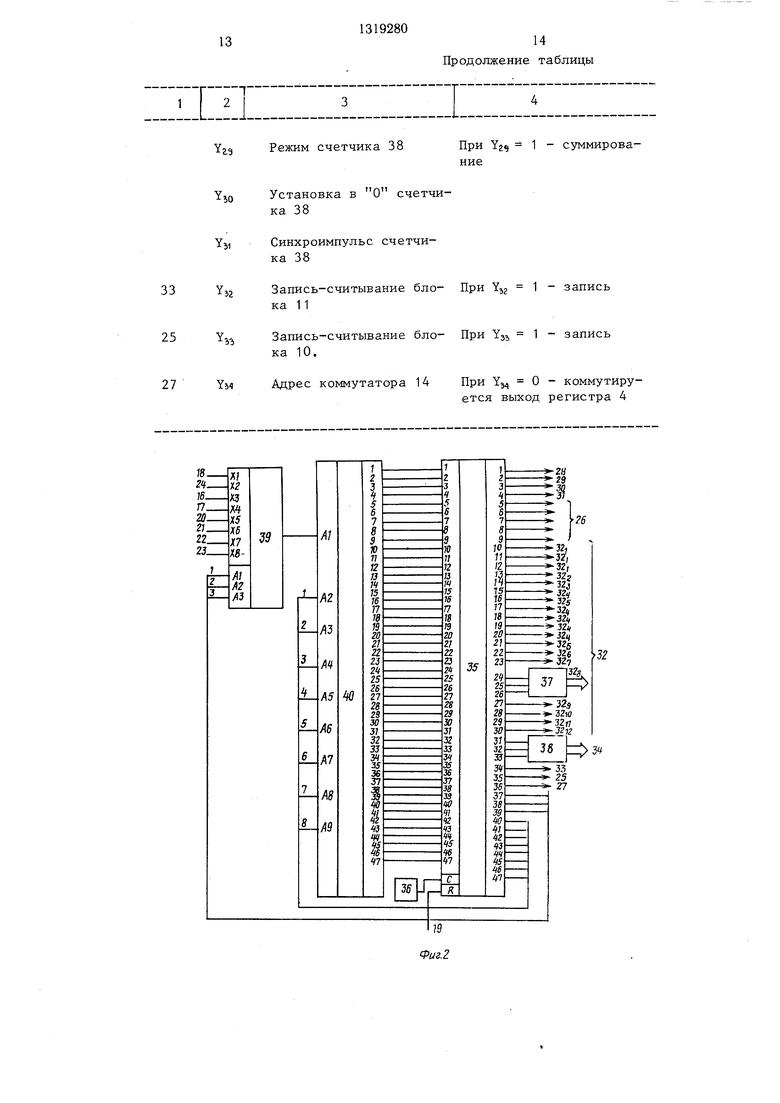

Блок 9 управления имеет входы 16-24 с первого по девятый и выходы 25-34 с первого по десятый, при этом четвертый вход 19 блока 9 управления является шиной «Запуск, а седьмой и восьмой входы 22, 23 блока 9 управления являются соответственно первой и второй управляюшими шинами. Блок 9 управления (фиг. 2) выполнен на регистре 35, генераторе 36 тактовых импульсов, первом и втором фибоначчиевых реверсивных счетчиках 37 и 38, мультиплексоре 39 и постоянном запоминаюшем устройстве 40.

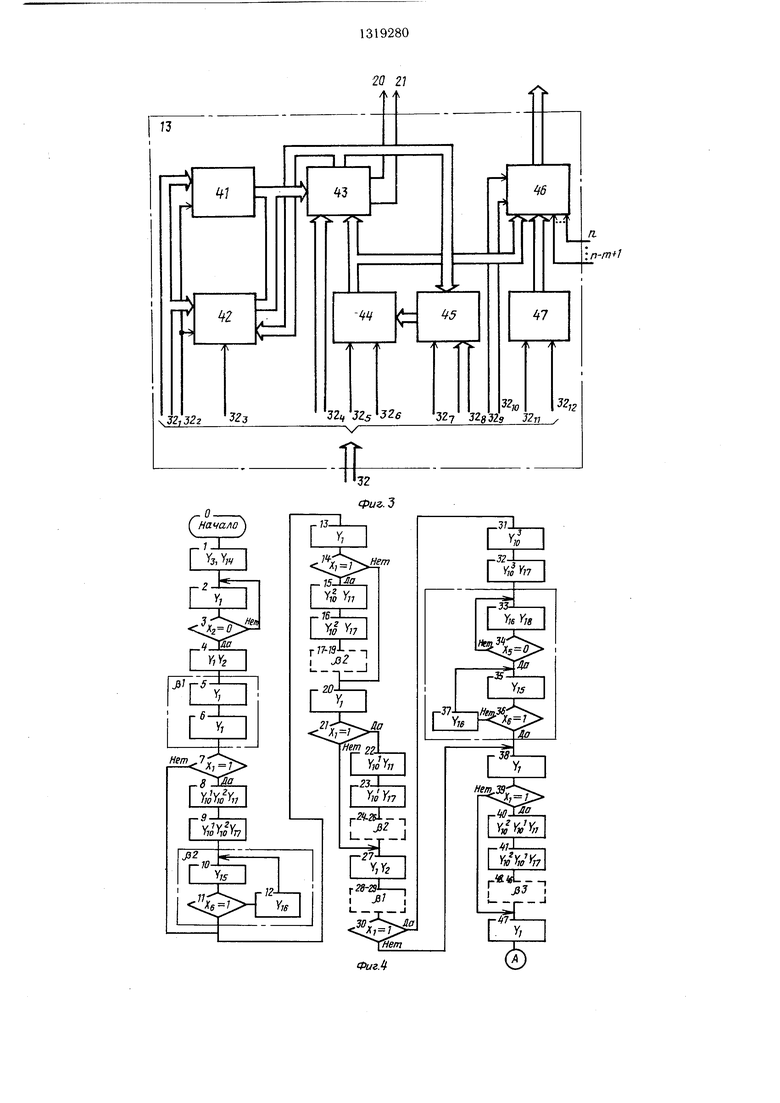

Вычислительный блок 13 (фиг. 3) выполнен на блоке 41 постоянной памяти, блоке 42 оперативной памяти, фибоначчиевом сум- маторе-вычитателе 43, первом регистре 44, первом и втором цифровых коммутаторах 45 и 46 и втором регистре 47.

Входные шины 1 преобразуемого кода разделены на две группы из m старших и (п-т) младших разрядов, где п - число разрядов преобразуемого кода.

Блок 11 на m входов и m выходов содержит т-разрядные слова старших с п-го по (п-ш+1)-й разрядов, являюш,иеся цифровыми эквивалентами слов старших с п-го по (п-т + 1)-й разрядов входного кода.

Блок 10 на m входов и (п-m-f-1) выходов содержит (п-01+1)-разрядные слова для формирования младших с (п-т-)-1)-го по 1-й разрядов рабочего кода Краб, являющиеся цифровыми эквивалентами слов старших с п-го по (п-т + 1)-й разрядов входного кода К и представляюшие код разности весов единичных разрядов старших групп входного К и рабочего Краб кодов.

Цифроаналоговые преобразователи 5 и 7 должны быть выполнены на основе избыточных измерительных кодов (ИИК). Любое дей

число в ИИК можно предста -1

i-o

ara,

0

5

0

5

где а,-ер,1} - двоичная цифра в i-м разряде

кода;

а - вес i-ro разряда , причем 1.а 2 и (.оС.

Блок 2 на (п-ni-|-2) входов и () выходов содержит цифровые эквиваленты младших с (п-ш+1)-го по 1-й разрядов кода Краб.

Устройство работает в режимах поверки и непосредственного преобразования входного кода с иррациональным основанием в аналоговую величину. К увеличению быстродействия ЦАП в режиме преобразования код-аналог приводит применение принципа параллельной обработки разрядов при коррекции входного кода. Сушность корреции заключается в преобразовании входного кода К в рабочий код Краб.. При этом код К разбивается на ш-разрядную группу старших разрядов и (п-т)-разрядную группу младших разрядов, обработка которых происходит параллельно с учетом кодов реальных значений весов разрядов ЦАП, определенных в режиме поверки. Поверка осуш,ест- влятся на основе сравнения различных кодовых представлений, соответствующих одному и тому же значению аналоговой величины.

В режиме поверки производится определение кодовых реальных весов разрядов основного ЦАП 5, причем его разряды делятся на группы неточных (старших) и точных (младших) разрядов. Такой подход справедлив для формирования весов разрядов 5 ЦАП с одинаковой относительной погрешностью 6Q. В этом случае абсолютные отклонения AQe от требуемых значений Q/тр для старших разрядов будут большими, а для младших - малыми. Поэтому определение кодов реальных весов разрядов производится только для группы из ш старших разрядов. Значение определяется из условия

0

0

о 5

5

Qrp. 1 ДРл-m-(-l QTP 2,t

где п - количество разрядов

основного

- количество

ЦАП 5;

дР„ т+1-отклонения от требуемого значения веса (п-т4-1)-го разряда;

2iH.

QTp.2 - значения весов 1-го и 2-го младших разрядов соответственно. После изготовления предлагаемого ЦАП измеряются реальные веса точных разрядов, их кодовые эквиваленты записываются в блок 41 и в дальнейшем используются при поверке. Определение кодов реальных весов неточных разрядов производится в режиме поверки и осуществляется последовательно от младшего из неточных разрядов к старшему. При этом дополнительный ЦАП 7 генерирует ступенчато нарастающий аналоговый сигнал А, число уровней которого соответствует числу неточных разрядов основного ЦАП 5.

Определение реального веса каждого не- 5 точного разряда производится за два цикла. В первом цикле происходит преобразование j-й ступени сигнала А, поступающего на первый вход блока 6 сравнения, в код . При этом на второй вход блока 6 поступает компенсирующий аналоговый сигнал Лке, 0 формирующийся на выходе ЦАП 5. Причем блок 9 в первом цикле выдает сигнал запрета на включение j-ro поверяемого разряда.

N/ - код реального веса 1-го р хранящийся в блоке 41.

Операция суммирования в фибо вом сумматоре-вычитателе 43 повт для все значащих разрядов кода К/.

Во втором цикле поверки произв повторное уравновешивание j-й ступе логового сигнала AJ блоками 4, 9, 1 чем запрета включения j-ro поверяемо ряда не происходит.

Код К; второго результата ур щивания получается последовательн читанием из кода К/, хранящегося в 43 после первого цикла, реальных разрядов N/, оставленных включенн

Первый цикл поверки осуществляется 15 результате повторного кодирования.

следующим образом. По команде из блока 9 старщий разряд регистра 4 устанавливается в единичное состояние. На выходе ЦАП 5 при этом появится аналоговый сигнал Лк|, равный весу старшего разряда Q . С помощью блока 6 производится 20 сравнение величин аналоговых сигналов Лj и Лк1. Выходной сигнал у; блока 6 удовлетворяет условию

Код К; второго результата уравн вания вычисляется в блоке 43 по ф

К/ К;-2 a,.N,,

где а /- двоичная цифра 1-го разряда деляемая в блоке 6 при пов уравновешивании.

У/

А; А,; А/ А,.

Если в результате сравнения у( 1, то п-й разряд в регистре 4 остается в единичном состоянии. Далее происходит включеПричем, так как с целью упрощения вычислений перед началом режима самоповерки кодам реальных значениГ весов неточных разрядов присваивается нулевое значение, то код К/ соответствует коду .реального значения веса j-ro разряда lNj: К,).

ние следующего (п-1)-го разряда. При этом зо код NJ переписывается в блок 42. На

компенсирующий аналоговый сигнал Ак2 станет равным сумме величин Qn и Qn-i.

Если у/ О, то п-й разряд в регистре 4 сбрасывается в нулевое состояние и также включается следующий (п-1)-й разряд,

при этом АК .

Далее производится сравнение аналоговых сигналов А, и Ак2. Преобразование осуществляется за п этапов сравнения. Величина компенсирующего аналогового сигнала АК; на каждом этапе определяется из выражения

этом процесс определе11 Я кода реального значения веса j-ro разряда ЦАП 5 закапчивается.

Определение кодов реа, 1ьпь1х значений весов остальных неточных разрядов про- 35 исходит аналогично и с учетом ранее определенных кодов весов млад|иих неточных разрядов. Процесс поверки заканчивается после определения кодов реальных значений весов всех старших разрядов.

На втором этапе поверки при имитации 40 различных входных кодовых комбинаций производится вычисление цифровых эквивалентов слов старших разрядов входного кода и цифровых эквивалентов слов старших разрядов входного кода, представляю- г щих код разности весов ед1-:ничных разрядов старших групп входного н рабочего кодов.

и

A, К

y/-Qn /+i,

На втором этапе поверки при имитации 40 различных входных кодовых комбинаций производится вычисление цифровых эквивалентов слов старших разрядов входного кода и цифровых эквивалентов слов старших разрядов входного кода, представляю- г щих код разности весов ед1-:ничных разрядов старших групп входного н рабочего кодов.

В качестве имитатора старших разрядов входного кода используется фибоначчиевый реверсивный счетчик 37, который последовагде у/ - выходной сигнал блока 6 на 1-м

этапе;

Qn-i+i-вес (п-l-fl)-ro разряда ЦАП 5. По выходным сигналам блока бис помощью блоков 41, 42 результат первого кодирования j-й ступени аналогового сигнала 50 тельно формирует все возможные комбл- вычисляется в фибоначчиевом сумматоре вы-нации. Для каждого имитированного входного кода определяется цифровой эквивалент путем суммирования кодов реа.чькых значений весов старших значений разря. дов, а также определяется код разности IK сов единичных разрядов старшей группь. сымитированного входного и рабочего кодов

читателе 43 по формуле

(-1

a/-N,,

55

где а/ - двоичная цифра 1-го разряда, определяемая блоком 6;

Цифровые эквиваленты слов старших разрядов, вычисленные для каждого из коN/ - код реального веса 1-го разряда, хранящийся в блоке 41.

Операция суммирования в фибоначчие- вом сумматоре-вычитателе 43 повторяется для все значащих разрядов кода К/.

Во втором цикле поверки производится повторное уравновешивание j-й ступени аналогового сигнала AJ блоками 4, 9, 14, причем запрета включения j-ro поверяемого разряда не происходит.

Код К; второго результата уравнове- щивания получается последовательным вычитанием из кода К/, хранящегося в блоке 43 после первого цикла, реальных весов разрядов N/, оставленных включенными в

результате повторного кодирования.

Код К; второго результата уравновешивания вычисляется в блоке 43 по формуле

К/ К;-2 a,.N,,

где а /- двоичная цифра 1-го разряда, определяемая в блоке 6 при повторном уравновешивании.

Причем, так как с целью упрощения вычислений перед началом режима самоповерки кодам реальных значениГ весов неточных разрядов присваивается нулевое значение, то код К/ соответствует коду .реального значения веса j-ro разряда lNj: К,).

код NJ переписывается в блок 42. На

этом процесс определе11 Я кода реального значения веса j-ro разряда ЦАП 5 закапчивается.

Определение кодов реа, 1ьпь1х значений весов остальных неточных разрядов про- исходит аналогично и с учетом ранее определенных кодов весов млад|иих неточных разрядов. Процесс поверки заканчивается после определения кодов реальных значений весов всех старших разрядов.

На втором этапе поверки при имитации различных входных кодовых комбинаций производится вычисление цифровых эквивалентов слов старших разрядов входного кода и цифровых эквивалентов слов старших разрядов входного кода, представляю- щих код разности весов ед1-:ничных разрядов старших групп входного н рабочего кодов.

В качестве имитатора старших разрядов входного кода используется фибоначчиевый реверсивный счетчик 37, который последовательно формирует все возможные комбл- нации. Для каждого имитированного вход55

Цифровые эквиваленты слов старших разрядов, вычисленные для каждого из кодов, записываются в блок 11, а коды разности весов единичных разрядов старших групп входного и рабочего кодов - в блок 10.

Адрес блоков 10 и 11 задается фибонач- чиевым реверсивным счетчиком 38. Блок 11 должен содержать группу старших разрядов рабочего кода. Причем эта кодовая комбинация определяется так, что сумма реальных весов единичных разрядов этой группы меньше или равна сумме весов разрядов, образуюш,их адрес. Разность этих сумм Ю представляется в виде кода и записывается в блок 10.

Работа устройства на втором этапе поверки осуш,ествляется следующим образом.

По сигналам блока 9 обнуляются регистры 44 и 47, фибоначчиевый сумматор-вычи- татель 43. Фибоначчиевый реверсивный счетчик 37 устанавливается в нулевое состояние. С помош.ью цифрового коммутатора 45 содержимое фибоначчиевого реверсивного счетчика 37 записывается в регистр 44, 20 остальные разряды которого заменяются нулями.

Затем в фибоначчиевый сумматор-вычи- татель 43 записывается содержимое регистра 44 и код реального веса старшего раз10 с помощью блока 3 суммируется с группой младших (п-т) разрядов, поступающих на второй информационный вход блока 3, и поступает на вход блока 2. С помощью блока 2 формируются младщих (п-т-(-1) разряды кода Крав (п-т + 1)-й разряд кода Краб определяется при помощи элемента ИЛИ 12 в результате логического сложения младшего 11 и старшего 2 разрядов блоков. Код с выходов блоков 11, 12 и 2 поступает на вход коммутатора 14. После коммутации код Краб поступает на вход ЦАП 5, в результате чего на выходной шине 15 уст- ройства появится аналоговая величина, соответствующая входному коду К.

Блок 9 управления выполнен на базе по- следовательностной схемы с использованием постоянного запоминающего устройства.

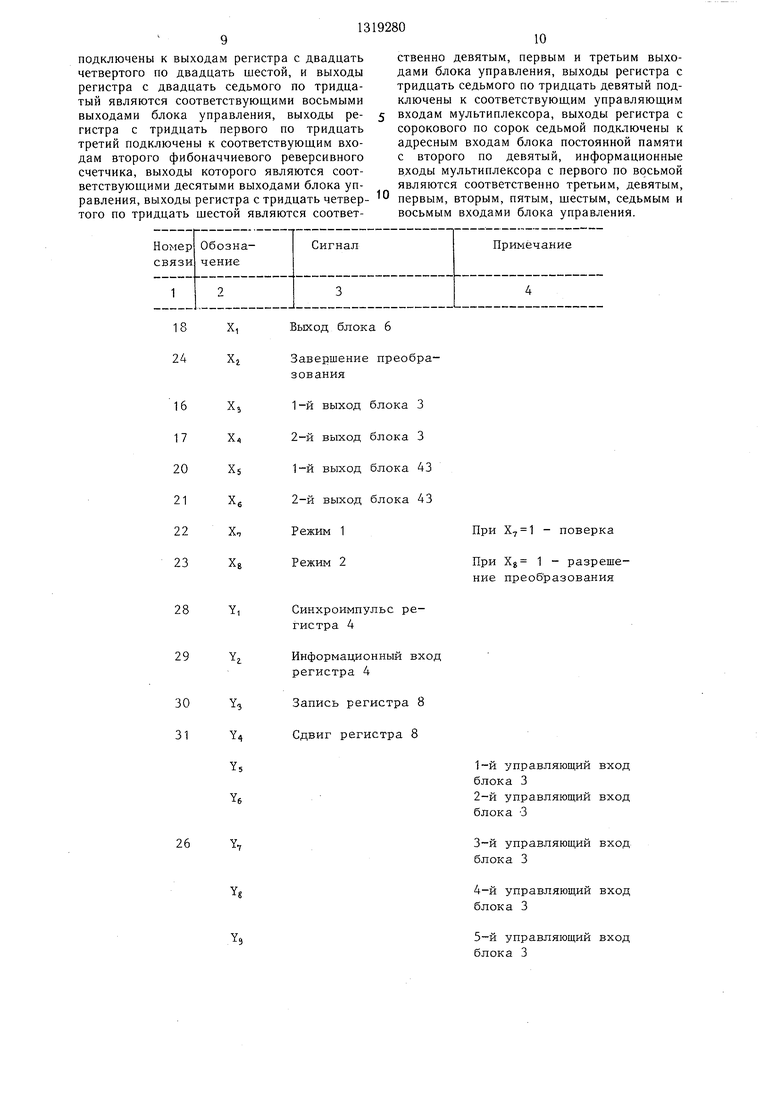

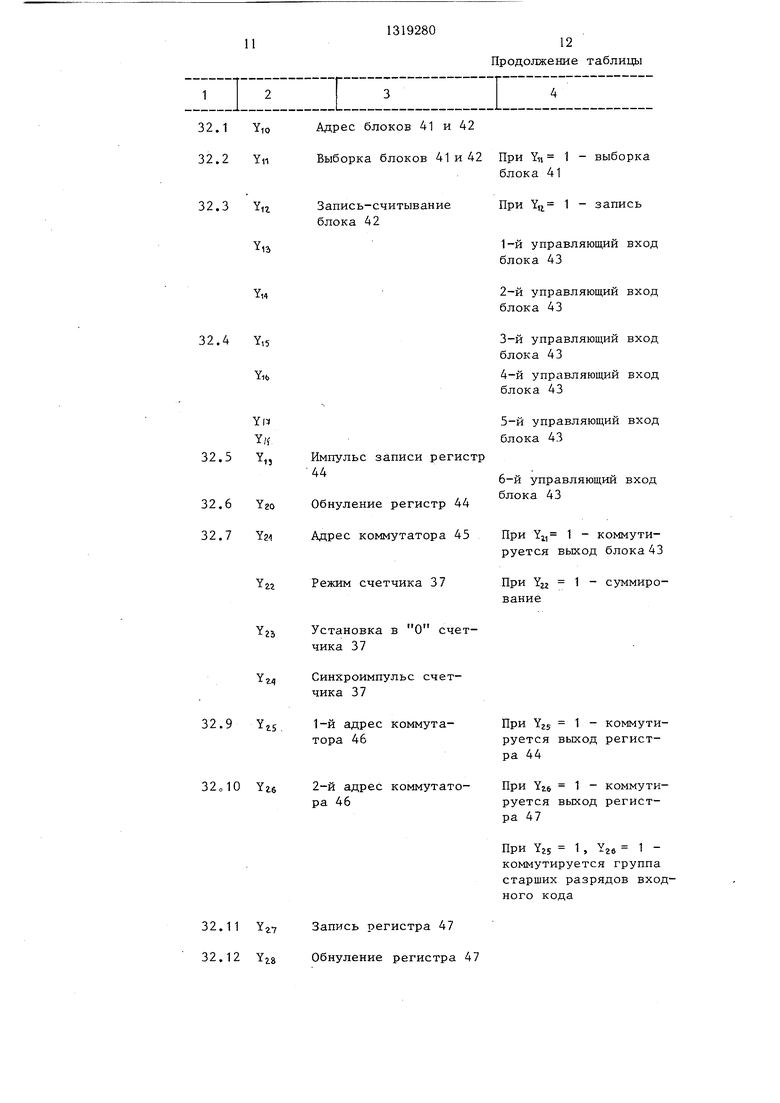

Необходимые для управления функционированием ЦАП управляющие и условные сигналы приведены в таблице при , т 3.

Алгоритм работы устройства (фиг. 4 и 5) состоит из вершин В (1-3) - начальная установка регистра 4 блока 43, запись в регистр 8; В (4-26) - первое кодирование А4 с запретом; В (27-64) - второе кодиро30

ряда КРП, хранимый в блоке 42, и они сравни- 25 вание А4 без запрета; В (65-68) - запись

Кр4 в блок 42, сдвиг регистра 8, обнуление блока 43; В (69-100) - первое кодирование А5 с запретом; В (101 -145) - второе кодирование А5 без запрета; В (146-149) - запись Кр5 в блок 42, сдвиг регистра 8, обнуление блока 43; В (150-186) первое кодирование А6 с запретом; В (187-241) - второе кодирование А6 без запрета; В (242)- запись Крб в блок 42; В (243-244) - обнуление блоков 43, 44, 47, установка в «О счетчика 37; В (245-368) - определение цифровых эквивалентов слов старших разрядов входного кода и цифровых эквивалентов слов старших разрядов входного кода, представляющих код разности весов единичных разрядов старших групп входного и рабочего кодов; В (369-376) - непосредственное цифроаналоговое преобразование.

35

ваются. При сравнении анализируется выходной сигнал 21 блока 43. Причем, если выходной сигнал 21 равен О, то содержимое регистра 44 не изменяется и в регистр 47 записывается, ноль при помощи блока 9. Если выходной сигнал 21 равен 1, то в регистр 44 записывается остаток (дальнейшее сравнение производится с ним), а в регистр 47 - единица.

Далее сравнивается содержимое регистра 44 с кодом реального веса следующего старшего разряда Крп-ь Сравнение происходит аналогично и это выполняется для всех кодов реальных значений весов старших разрядов, определенных на первом этапе поверки. В результате в регистре 47 сформируется код М /, являющийся цифро- 40 вым эквивалентом слов старших разрядов входного кода, который по сигналу блока 9 перепишется в блок 11. Содержимое регистра 44 перепишется в блок 10. Адрес блоков 10 и 11 задается фибоначчиевым реверсивным счетчиком 38.

Посл е этого счетчик 37 меняет свое состояние и весь процесс происходит аналогично описанному.

В режиме непосредственного преобразования входной п- разрядный код К поступает на входную шину 1. Старшие с п-го по (п-т+ 1)-й разряды кода К с помощью блока 11 преобразуются в старшие с (п)-го по ()-й разряды рабочего кода Краб.. Старшие с (п)-го по (п-т+1)-й разряды кода с помощью блока 10 преобразуются гс также в код разности весов единичных разрядов старших групп входного кода и рабочего Крав кодов. Код с выхода блока

50

Формула изобретения

1. Цифроаналоговый преобразователь, содержащий основной цифроаналоговый преобразователь, первый блок оперативной памяти, управляющий вход которого подключен к первому выходу блока управления, выходы подключены. к соответствующим первым информацонным входам фибоначчиевого сумматора-вычитателя, первый и второй выходы которого подключены соответственно к первому и второму входам блока управления, управляющие входы фибоначчиевого сумматора-вычитателя подключены к соответствующим вторым выходам блока управления, третий выход которого подключен к управляющему входу цифрового коммутатора, четвертый и пятый выходы блока

10 с помощью блока 3 суммируется с группой младших (п-т) разрядов, поступающих на второй информационный вход блока 3, и поступает на вход блока 2. С помощью блока 2 формируются младщих (п-т-(-1) разряды кода Крав (п-т + 1)-й разряд кода Краб определяется при помощи элемента ИЛИ 12 в результате логического сложения младшего 11 и старшего 2 разрядов блоков. Код с выходов блоков 11, 12 и 2 поступает на вход коммутатора 14. После коммутации код Краб поступает на вход ЦАП 5, в результате чего на выходной шине 15 уст- ройства появится аналоговая величина, соответствующая входному коду К.

Блок 9 управления выполнен на базе по- следовательностной схемы с использованием постоянного запоминающего устройства.

Необходимые для управления функционированием ЦАП управляющие и условные сигналы приведены в таблице при , т 3.

Алгоритм работы устройства (фиг. 4 и 5) состоит из вершин В (1-3) - начальная установка регистра 4 блока 43, запись в регистр 8; В (4-26) - первое кодирование А4 с запретом; В (27-64) - второе кодирование А4 без запрета; В (65-68) - запись

Формула изобретения

1. Цифроаналоговый преобразователь, содержащий основной цифроаналоговый преобразователь, первый блок оперативной памяти, управляющий вход которого подключен к первому выходу блока управления, выходы подключены. к соответствующим первым информацонным входам фибоначчиевого сумматора-вычитателя, первый и второй выходы которого подключены соответственно к первому и второму входам блока управления, управляющие входы фибоначчиевого сумматора-вычитателя подключены к соответствующим вторым выходам блока управления, третий выход которого подключен к управляющему входу цифрового коммутатора, четвертый и пятый выходы блока

управления подключены соответственно к тактовому и информационному входам регистра последовательного приближения, шестой и седьмой выходы блока управления подключены соответственно к входам записи и сдвига регистра сдвиги, выходы которого подключены к входам дополнительного цифроапалогового преобразователя, выход которого подключен к первому входу блока сравнения, второй вход которого под2. Преобразователь по п. 1, отличающийся тем, что вычислительный блок выполнен на блоке постоянной памяти, блоке оперативной памяти, первом и втором регистрах, первом и втором цифровых коммутаторах, фибоиаччиевом сумматоре-вычи- тателе, первый и второй выходы которого являются соответственно первым и вторым выходами вычислительного блока, третьи выходы подключены к соответствующим инключен к выходу основного цифроаналого- 10 формационным входам блока оперативной вого преобразователя и является выходнойпамяти и к соответствующим первым инфиной, выход блока сравнения подключенформационным входам первого цифрового

коммутатора, первые информационные входы фибоначчиевого сумматора вычитателя г подключены к соответствующим выходам блоков постоянной и оперативной памяти, соответствующие адресные входы которых и входы разрещения считывания попарно объединены, вторые информационные входы фибоначчиевого сумматора-вычитателя объ- щииами m старщих разрядов преобразуе- 20 единены с соответствующими первыми ин- мого кода, управляющие входы вычислитель-формациониыми входами второго цифровоного блока подключены к соответствующимго коммутатора и подключены к соответвосьмым выходам блока управления, пер-ствующим выходам первого цифрового комвый и второй выходы вычислительногомутатора, вторые информационные входы

блока подключены соответственно к пя-второго цифрового коммутатора подключены

тому и щестому входам блока управления,к соответствующим выходам второго регистк третьему входу блока управления, четвертый вход которого является шиной «запуск, отличающийся тем, что, с целью повышения быстродействия, в него введены блок постоянной памяти, второй блок оперативной памяти, элемент ИЛИ, вычислительный блок, информационные входы которого являются соответствующими входными

девятый выход которого подключен к управляющему входу второго блока оперативной памяти, информационные входы которого объединены с соответствующими информара, третьи, информационные входы второго цифрового коммутатора являются соответствующими информационными входами вычислительного блока, а выходы являются

соответствующим десятым выходам блока управления, седьмой и восьмой вход которого являются соответственно первой и второй управляющими щинами, девятый вход подключен к выходу окончания преобразоционными входами первого блока опера- or,соответствующими третьими выходами вычи- тивной памяти и подключены к соответ-слительного блока, при этом адресные вхо- ствуюцХим третьим выходам вычисли-ды, вход разрешения считывания и вход за- тельного блока, адресные входы второго бло-писи-считывания блока оперативной памяти, ка оперативной памяти объединены с соответ-управляющие входы фибоначчиевого сум- ствующими адресными входами первогоматора-вычитателя, входы записи и обнуле- блока оперативной памяти и подключены к ния первого регистра, адресный вход и вто- pyg информационные входы первого цифрового коммутатора, первый и второй адресные входы второго цифрового коммутатора, входы записи и обнуления второго регистра являются соответствующими управляющими

вания регистра последовательного прибли- 40входами вычислительного блока, жения, информационные выходы которого3. Преобразователь по п. , отличающий- подключены к соответствующим первым ин-ся тем, что блок управления выполнен на формационным входам цифрового коммута-блоке постоянной памяти, регистре, гене- тора, выходы которого подключены к вхо-раторе тактовых импульсов, первом и вто- дам основного цифроаналогового преоб-ром фибоначчиевых реверсивных счетчиках, разователя, вторые п информационных вхо- мультиплексоре, выход которого подклю- дов, где п - число разрядов преобразуе-чен к первому адресному входу блока но- мого кода, подключены соответственно к вы-стоянной памяти, выходы которого подклю- ходам блока постоянной памяти с первогочены к соответствующим информационным по (п m)-fi, выходу элемента ИЛИ, выхо-входам регистра, тактовый вход которого дам второго блока оперативной памяти с вто- Qподключен к выходу генератора тактовых рого по т-й, первый выход которого под-импульсов, вход обнуления является четвер- ключен к первому входу элемента ИЛИ,тым входом блока управления, выходы ре- второй вход которого подключен к (л )гистра с первого по четвертый являются выходу блока постоянной памяти, входы ко-соответственно выходами с четвертого по торого подключены к соответствующимседьмой блока управления, выходы регист- третьим выходам фибоначчиевого сумма- 55рз с пятого по девятый являются соответ- тора-вычитателя, вторые информационныествующими вторыми выходами блока управ- входы которого являются соответствующимиления, выходы регистра с десятого по двад- входными щинами п-m младших разрядовцать третий, выходы первого фибоначчие- преобразуемого кода.вого реверсивного счетчика, входы которого

2. Преобразователь по п. 1, отличающийся тем, что вычислительный блок выполнен на блоке постоянной памяти, блоке оперативной памяти, первом и втором регистрах, первом и втором цифровых коммутаторах, фибоиаччиевом сумматоре-вычи- тателе, первый и второй выходы которого являются соответственно первым и вторым выходами вычислительного блока, третьи выходы подключены к соответствующим инра, третьи, информационные входы второго цифрового коммутатора являются соответствующими информационными входами вычислительного блока, а выходы являются

подключены к выходам регистра с двадцать четвертого по двадцать шестой, и выходы регистра с двадцать седьмого по тридцатый являются соответствующими восьмыми выходами блока управления, выходы регистра с тридцать первого по тридцать третий подключены к соответствующим входам второго фибоначчиевого реверсивного счетчика, выходы которого являются соответствующими десятыми выходами блока управления, выходы регистра с тридцать четвертого по тридцать щестой являются соответ

X, X, Xs

Хб Х

Xg Y,

г

Y, Y4 YS Y6

зевания

1-и выход блока 3

2-й выход блока 3

1-й выход блока 43

2-й выход блока 43

Режим 1

Режим 2

Синхроимпульс регистра 4

Информационный вход регистра 4

Запись регистра 8 Сдвиг регистра 8

26

ственно девятым, первым и третьим выходами блока управления, выходы регистра с тридцать седьмого по тридцать девятый подключены к соответствующим управляющим входам мультиплексора, выходы регистра с сорокового по сорок седьмой подключены к адресным входам блока постоянной памяти с второго по девятый, информационные входы мультиплексора с первого по восьмой являются соответственно третьим, девятым, первым, вторым, пятым, щестым, седьмым и восьмым входами блока управления.

При - поверка

При Xg 1 - разрешение преобразования

1-й управляющий блока 3

2-й управляющий блока 3

3-й управляющий блока 3

4-й управляющий блока 3

5-и управляющий блока 3

11

Y,5 Yi6

Yl3 Y;f

Y,,

Ygo

Yai

Yz2

YZJ Yг,

Y

г5

Импульс записи регистр 44

Обнуление регистр 44 Адрес коммутатора 45

Режим счетчика 37

Установка в О счетчика 37

Синхроимпульс счетчика 37

1-й адрес коммутатора 46

32„10 Yг6

2-й адрес коммутатора 46

32.11Y27

32.12Yi8

Запись регистра 47 Обнуление регистра 47

1319280

12 Продолжение таблицы

блока 43

2-й управляющий блока 43

3-й управляющий блока 43

4-й управляющий блока 43

5-й управляющий блока 43

6-й управляющий вход блока 43

При Ту 1 - коммутируется выход блока 43

При YIZ 1 - суммирование

При Yjs 1 - коммутируется выход регистра 44

При 1 - коммутируется выход регистра 47

При 1 , Угв 1 - коммутируется группа старших разрядов входного кода

13

ИГ

Yi3

Режим счетчика 38

io

Установка в О счетчика 38

33

25

27

ьг

л

YM

Синхроимпульс счетчика 38

Запись-считывание бло- При Yjj 1 - запись ка 11

Запись-считывание бло- При Yjj 1 - запись ка 10.

Адрес коммутатора 14 При Yj О - коммутируется выход регистра 4

1319280

14 Продолжение таблицы

При Угч 1 - суммирование

ФигЛ

Нет

Г

I У,зУ,7

Т:

У18

У К-7

70 7

21(7

г 5М5-1 I J33

27Z-L

2бУ:

Jr

Г

7J. 5/55

W )а

нет

р275-.. I

( У21 гцj-369гч

нет

да

ю У

11

/т К

Ю 17

г25Ч 2

г&

W

r25J-r i- - -,

I 7

Г Jg

I

.

г Конец

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197078A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

Изобретение относится к области вычислительной и измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые. Цель изобретения - повышение быстродействия цифроаналогового преобразователя, построенного на основе избыточных измерительных кодов и обладающего возможностью осуществления самопроверки. Цифроаналого- вый преобразователь (ЦАП) содержит входные шины преобразуемого кода, блок 2 постоянной памяти, фибоначчиевый сумматор- вычитатель 3, регистр 4 последовательного приближения, основной ЦАП 5, блок 6 сравнения, дополнительный ЦАП 7, регистр 8 сдвига, блок 9 управления, первый и второй блоки 10, 11 оперативной памяти, элемент 12 ИЛИ, вычислительный блок 13, цифровой коммутатор 14, выходную шину 15. Увеличение быстродействия достигается за счет параллельной обработки разрядов при коррекции входного кода в рабочий код основного ЦАП 5, 2 з.п. ф-лы, 5 ил. 1СЛ 00 со ю 00

| Цифро-аналоговый преобразователь | 1981 |

|

SU953721A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1985-07-08—Подача