к прямому и инверсному вьйсодам триггера соответственно, а выходами - к второму и третьему выходам блока синхронизации.

3. Устройство по п.1, о т л и чающееся тем, что блок срав нения содержит компараторы, элементы И и НЕ и регулируемЕлй рёзистивнь делитель напряжения, подклюк1енн1 .: первым выводом к первому входу блока сравнения и первому входу первого компаратора, вторми выводом к. тине нулевого потенциала блока срав нения, а выводом подвижного контакта - к первому входу второго компаратора, соединенного вторым входом с вторьм входом блока сравнения и вторым входом первого компаратора, а выходом - с входом элемента НЕ и с первым входом первого элемента И, подключенного выходом к первому выходу блока сравнения, а вторым входом к выходу первого компаратора и к первому входу второго элемента И, второй вход и выход которого соединены соответственно с выходом элемента НЕ и вторым выходом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения отношения двух напряжений | 1989 |

|

SU1702397A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для управления технологическим объектом | 1985 |

|

SU1275377A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1229780A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

.1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОТНОШЕНИЯ ДВУХ НАПРЯЖЕНИЙ, содержащее кодоуправляемый резистор, блок сравнения, цифрааналоговый преобразователь и коммутатор, подключенный управляющим входом к первому выходу блока синхронизации, отличающееся тем, что, с целью повышения быстродействия и точности определения отношения, в него дополнительно введены два реверсивных счетчика, элементы И и НЕ, два буферных регистра и генератор счетньк импульсов, соединенный выходом с первыми входами первого и второго элементов И, подключенных выходами к счетным входам первого и второго реверсивных -счетчиков соответственно, причём второй вход первого элемента И соединен с вторым выходом блока синхронизации и входом начальной установки первого буферного регистра, подключенного входом разрешения записи к третьему выходу блока синхронизации, второму входу второго элемента И и первому входу третьего элемента И, информационными входами к выходам разрядов второго реверсивного счетчика, а выходами - к входам цифроаналогового преобразователя, Соединенного выходом с первым входом блока сравнения, подключенного вторым входом к выходу кодоупра.вляемого резистора, первым выходом - к входу управления реверсом первого реверсивного счетчика и входу элемента НЕ, а вторым выходом - к. входам запрета счета первого и второго реверсивных счетчиков и к второму входу третьего элемента И, соединенного выходом с входом разрешения (Л записи второго буферного регистра, выходы разрядов которого являются выходами устройства, а информационные входы подключены к выходам разрядов второго реверсивного счетчика, соединенного входом управления реверсом с выходом элемента НЕ, причем СП выходы разрядов нервбго реверсивного счетчика подключены к управлякнвдм со со входам кодоупра ляемого резистора, соединенного сигнальным входом с вы ходом коммутатора, первый и второй сигнальные входы которого являются входами ус тройства. 2. Устройство по п.1, о т л и чающееся тем, что блок синхронизации содержит триггер, элемент И и генератор импульсов, выход которого является первым выходом блока синхронизации и соединен со счетным входом триггера и с первыми входами первого и второго элементов И, подключенных вторыми входами

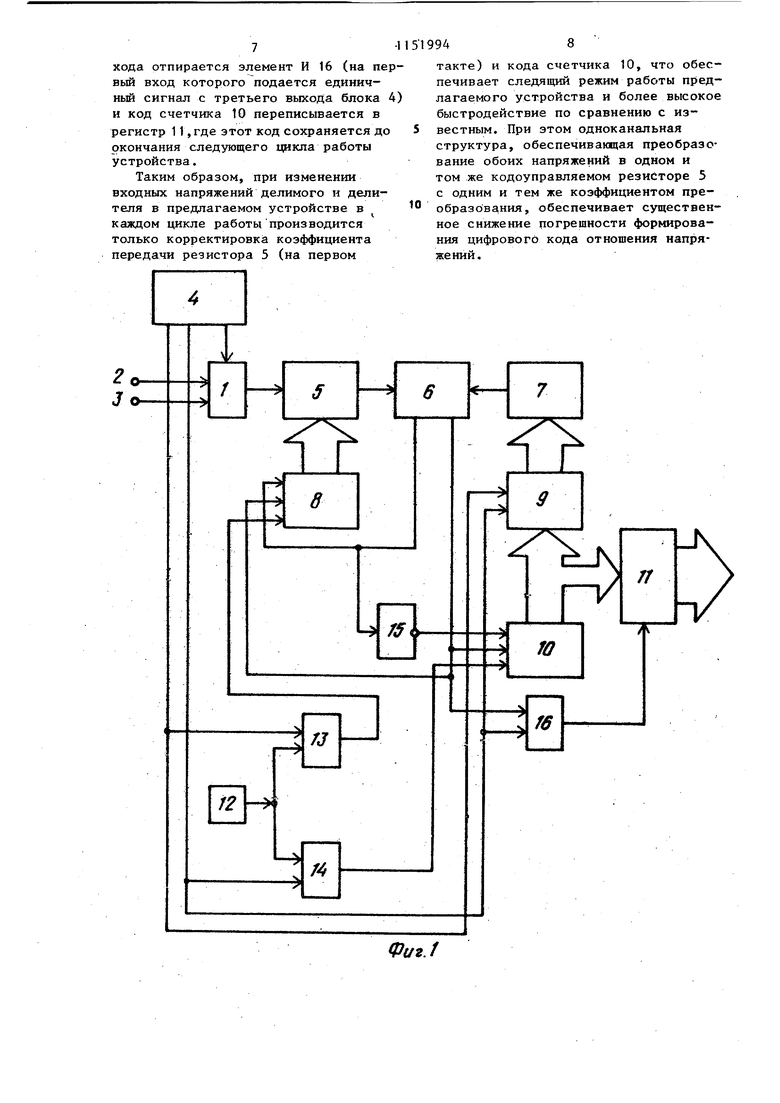

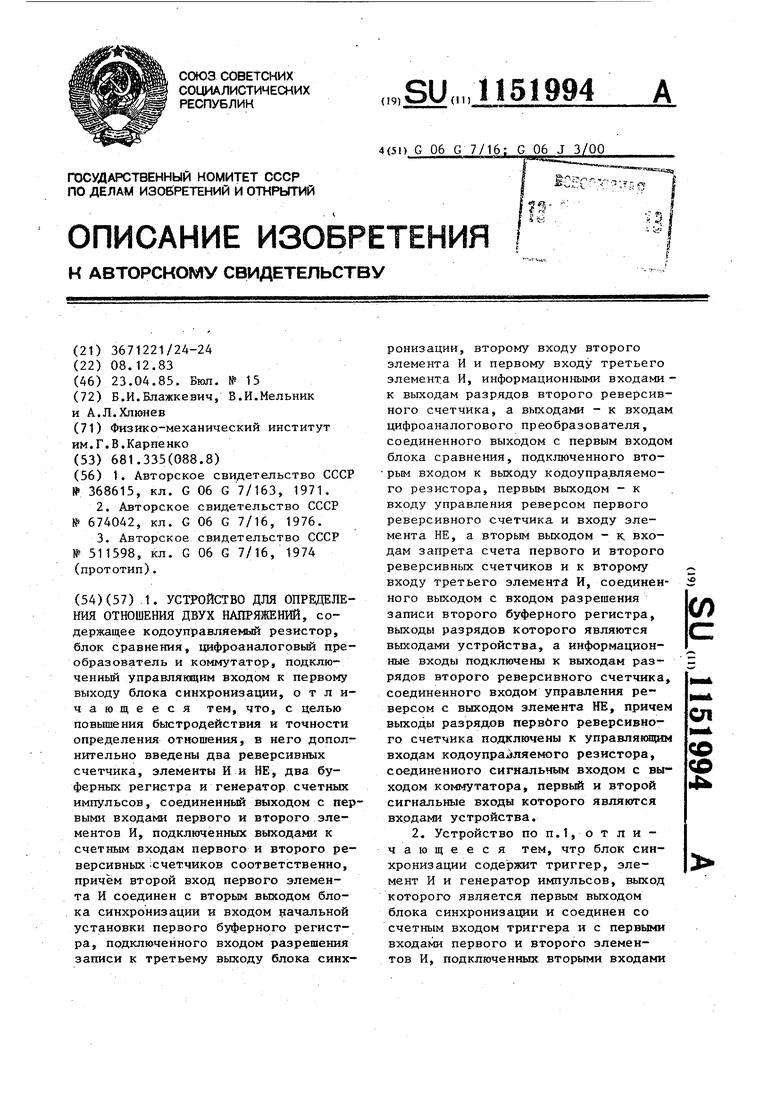

Изобретение относится к области автоматики и вычислительной техники и может найти применение в гибридных вьтчислительных устройствах и системах, в частности, при выполнении пре образования отношения двух напряжений в цифровой код. Известно аналого-цифровое делительное устройство содержащее преобразователь код-напряжение, счетчик блок сравнения, элемент И и генерато тактовых импульсов ТJ. Известно также делительное устройство, содержащее блок синхрониза ции, ключи, генератор тактовых импульсов, элемент И, реверсивньй сче чик и цифроаналоговьй преобразователь t2 1. Недостатками данньЕХ устройств являются пониженные быстродействие и точность. Наиболее близким к изобретению является устройство для определения отношения двух напряжений, содержащее два кодоуцравляеыых резистора, блок сравнения, цйфроаналоговый пре образователь, источник эталонного напряжения, програ шный блок, групп триггеров и два комкутагора, первый из которых подключен сигнальными входами к выходам первого кодоуправ ляемого резистора и цифроаналоговог преобразователя, управляющим входом к первому выходу блока сиихронизации, а выходом - к первому входу блока сравнения, соединенного вторым входом с выходом второго коммутатора, подключенного сигнальнь1ьш входами к выходам второго кодоуправляемого резистора и источника эталонного напряжения , причем первый и второй кодоуправляемые резисторы соединены сигнальными входами с входами устройства, а управляйщими входами г с выходами.триггеров группы, подключенных установочными входами к входам цифроаналогового преобразователя, и выходами программного- блока, соединенного сигнальньш входом с выходом блока сравнения Сз 3. Недостатками известного устройства являются пониженные быстродействие и точность из-за повышенных включенных затрат на обработку первого и второго циклов преобразования м наличие ошибок, обусловленных неидентичностью вы)толнения кодоуправляемых резисторов. Целью изобретения является повышение быстродействия и точности определения отношения двух напряжений. Поставленная цель достигается тем, что в устройство для определеиия отношения двух напряжений, содер жап(ее кодоуправляемый резистор, блок сравнения, цифроаналоговый преобразователь и коммутатор, подключение управляющим входом к первому выходу блока синхронизахщй, дополнительно введены два реверсивных счетчика, элёме{Ггы И и НЕ, двд буферных регистра и генератор счетных импульсов, соединенный выходом с первыми входами первого и второго элементов И, подключенных выходами к счетным входам первого и второго реверсивных счетчиков соответствен но, причем второй вход первого эле мента И соединен с вторым выходом блока синхрониэайии и входом началь ной установки первого буферного регистра, подключенного входом разрешения записи к третьему выходу блока синхронизации, второму входу вто рого элемента И -и первому входу тре тьегЬ элемента И, инфppмaциoнны Q входами - к вькодам разрядов второго реверсивного счетчика, а выходами - к входам цйфроаналогового преобразователя, соединенного выходом с первым входом блока сравнения, по ключенного вторым входом к выходу кодоуправляемого резистора, первь м выходом - к входу управления реверсом первого реверсивного счетчика и входу элемента НЕ, а вторым выходом к входам запрета счета первого и второго реверсивных счетчиков второму входу третьего элемента И, соединенного выходом с входом разре шения записи второго буферного регистра, выходы разрядов которого являются вьтходами устройства, а информационные входы подключены к выходам разрядов второго реверсивного счетчика, соединенного входом управ ления реверсом с выходом элемента Н причем выходы разрядов первого реверсивного счетчика подключены к . управляющим входам кодоуправляемого резистора, соединенного сигнальным входом с выходом коммутатора, первы и второй сигнальные входы которого являются входаю устройства. Кроме того, блок синхронизации содержит триггер, элемент И и генер тор импульсоВ, выход которого являе ся первым выходом блока синхронизации и соединен со счетным входом : триггера и с первыми входами первого и второго элементов И, подключен ных вторыми входами к прямому и инверсному выходам триггера соответст венно, а выходам - к второму и третьему выходам блока синхронизаци Блок сравнения содержит компараторы, элементы И и НЕ и регулируемый резйстивный делитель напряжения подключенный первым выводом к перво му входу блока сравнения и первому входу первого компаратора, вторым вьшодом - к шине нулевого потенциала блока сравнения, а выводом подвижного контакта - к первому входу второго компаратора, соединенного вторым входом с вторым входом блока сравнения и вторым входом первого компаратора, а выходом - с входом элемента НЕ и с первым входом первого элемента И, подключенного выходом к первому выходу блока сравнения, а вторьм входом - к выходу первого .компаратора и к первому входу второго элемента И, второй вход и выход которого соединены соответственно с вькодом элемента НЕ и вторым выходом блока сравнения. На фиг.1 изображена блок-схема устройства для определения отношения двух напряжений; на фиг.2 - схема блока синхронизации; на фиг.3 - то же, блока сравнения. Устройство дпя определения отношения двух напряжений (фиг.1) содержит коммутатор 1, первый 2 и второй 3 входы устройства, блок 4 синхронизации, кодоуправляеьяый резистор 5, блок 6 сравнения, цифроаналоговьй преобразователь 7, первый реверсивньш счетчик 8, первый буферный регистр 9, второй реверсивный счетчик 10, второй буферный регистр 11, генератор 12 счетных импульсов, первый и второй элементы И 13 и 14, элемент НЕ 15 и третий элемент И 16. Блок 4 синхронизации (фиг.2) содержит генератор 17 импульсов, триггер 18, первый и второй элементы И 19 и 20 и с первого по третий выходы 2123. Блок 6 сравнения (фиг.З) содержит первый 24 и второй 25 компараторы, регулируемый резистившяй делитель 26 напряжения, элемент НЕ 27, первый и второй элементы И 28 и 29, первый и второй входы 30 и 31 блока сравнения и первый и второй выходы 32 и 33 блока сравнения. Устройство работает следующим образом. Блок 4 синхронизации осуществляет фор шрованив на первом выходе последовательности импульсов типа 14еандр с периодом Т, осуществляющих последовательное переключение коммутатора 1, и формирование на втором и третьем выходах двух последовательностей импульсов с периодом 2Т каждая смещенных одна относительно другой на время Т. Преобразование входных напряжений и и 7/0; V 70), поступающих на входы 2 и 3 устройства, в цифровой эквивалент их отношения осуществляются в два такта, В первом такте на время действия импульса с первого выхода блока 4 коммутатор 1 подключает напряжение делителя } к входу кодоуправляемого резистора 5. Одновременно с этим сигналом с второго выхода блока 4 отпирается элемент И 13 и в регистре 9 устанавливается начальное значение кода , эквивалентное единице. За счет изменения состояния реверсивного счетчика 8 устанавливается значение коэффициента преобразования К резистора 5, удовлетворяющее соотношению U,Kj-K,Nv,,,t , C1) где Д - разность напряжений, поступающих на входы блока сравнения;К-, - постоянньй коэффициент преобразования цифроаналоговог преобразователя 7; - порог срабатьгоания блока 6 сравнения (может регулироваться изменением положения подвижного контакта делителя 26). Логика работы блока 6 сравнения такова, Б случае Д7 сигналы на пер вом и втором выходах 32 и 33 блока 6 принимают значения логического нуля. В случае сигнал на первом выходе 33 блока сравнения принимает значение логической единицы , а на втором вькоде 33 - логического нуля Если же , то напряжение на втором выходе блока сравнения принимает значение логической единицы независимо от значения сигнала на первом выходе., В первом такте работы импульсы генератора 12 через элемент И 13 поступают на счетньй вход счетчика 8, увеличивая его выходной код при &.или уменьшая выходной код счетчика при Д7 , что соответственно приводи к увеличению или к уменьшению текуще го значения коэффициента передачи ре зистора 5. Изменение этого коэффициента продолжается до момента появления логической единицы на втором вы-, ходе 33 блока, т.е. до выполнения неравенства (1). Сигнал с второго выхода блока 6 сравнения поступает на вход запрета счета счетчика 8, фиксируя его содержимое..После окончания действия импульса на втором выходе блока 4 синхронизации элемент И 13 запирается, обеспечивая сохранение полученного коэффициента передачи на время второго такта работы. Во втором такте работы коммутатор 1 подключает к входу резистора 5 напряжение делимого и . Импульсом с третьего выхода блока 4 синхронизации отпирается элемент И 14, в регистр 9 подается разрешение на перенос в этот регистр выходного кода счетчика 10. В этом такте формируемьш в реверсивном счетчике 10 текзпций код непрерывно переносится в регистр 9 и в цифроаналоговом преобразовате- . ле 7 преобразуется в напряжение U- К , поступающее, на первый вход блока 6 сравнения, на втором входе которого в это время действует напряжение с выхода резистора 5, равное и,„ Так как вход управления реверсом счетчика 10 подключен к первому выходу блока 6 сравнения че.рез элемент НЕ 15, то при UJ-UT.- происходит уменьшение выходного кода счетчика 10, а при - увеличение этого кода до момента времени удовлетворения соотношения lUj-U ( , фиксируемого появлением единичного сигнала на втором выходе блока 4 . сравнения. При этом выходной код счетчика 10 удовлетворяет условию UT Kjg и EiN.N 10 10,1 Uj, К, U Из выражения (3) следует, что при сформированньш в счетчике 10 во втором такте рабо.ты код N выражает искомое значение отношения входных напряжений с мультипликативной погрешностью, не превышающей Л1±1 U. I и аддитивной погрешностью,. ч г е превышающей . По окончании формирования кода у етчика 10 сигналом с второго вы7хода отпирается элемент И 16 (на пе вый вход которого подается единичный сигнал с третьего выхода блока и код счетчика 10 переписывается в регистр 11, где этот код сохраняется д окончания следующего цикла работы устройства. Таким образом, при изменении входных напряжений делимого н делителя в предлагаемом устройстве в каждом цикле работы производится только корректировка коэффициента передачи резистора 5 (на первом такте) и кода счетчика 10, что обеспечивает следящий режим работы предлагаемого устройства и более высокое быстродействие по сравнению с известным. При этом одноканальная структура, обеспечивающая преобразование обоих напряжений в одном и том же кодоуправляемом резисторе 5 с одним и тем же коэффициентом преобразования, обеспечивает существенное снижение погрешности формирования цифрового кода отношения напряжений.

Фиг.1

тф{/г. 2

21

22

30

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АНАЛОГО-ЦИФРОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 0 |

|

SU368615A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-08—Подача