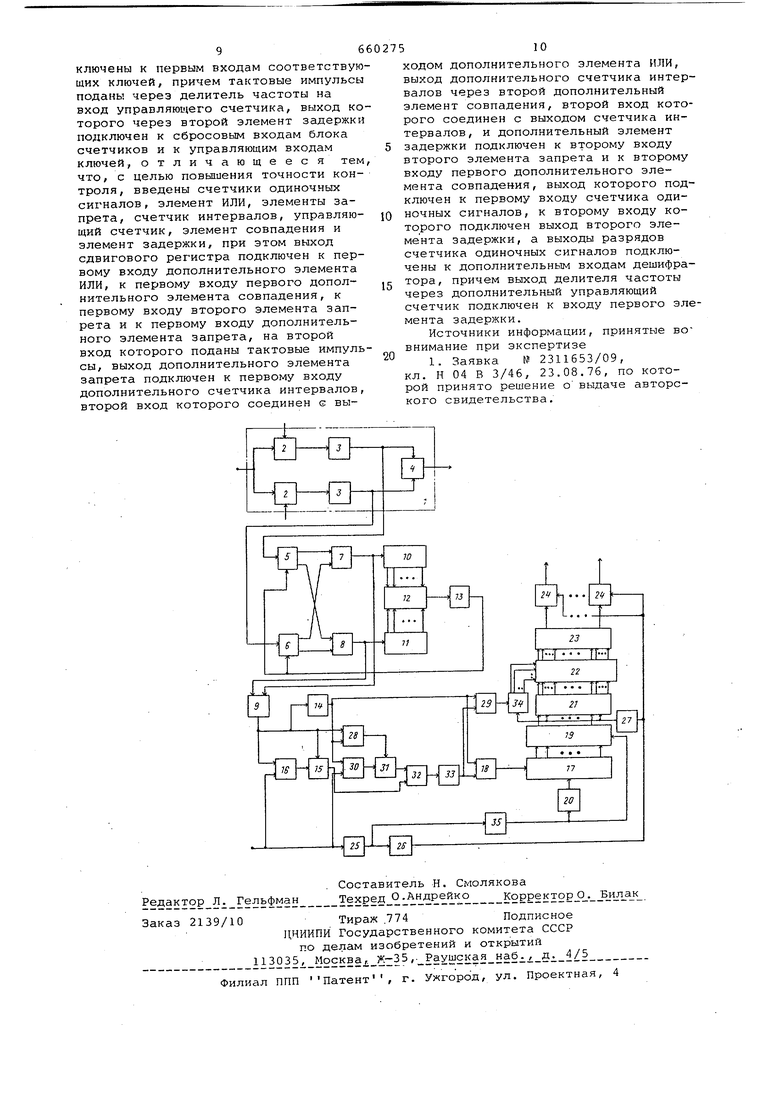

измерения которых можно оценинать вероятность г - кратной ошибки в п. - разрядной послелователъности принимаемых единичнЕ-лх элементов. Цель изобретения - повымение точности контроля. Для этого в устройство для контро ля состояния каналов связи, содержащее корреляционный приемник, управляющие выходы которого подключены к первым входам двух идентичных спусков-ых схем, единичные выходы которых подключены к входам первой схемы совпадения, а нулевые - к входам вто рой схемы совпадения, выходы последних подключены к входам первого элемента ИЛИ и через соответствующие счетчики к входам элемента сравнени выход которого через интегратор подключен к BTOpEiiM входам спусковых схе при этом выход первого элемента ИЛИ соединен с входом сдвигового регистра, с первым входом счетчика интерва лов и через первый элемент запрета, на второй вход которого поданы такто вые импульсы, с вторым входом счетчика интервалов, разрядный счетчик, к первому входу которого подключен выход второго элемента запрета, выходы разрядного счетчика подключены к информационным входам блока считы вания, управляющий вход которого со динен с входом первого элемента задержки, выход которого подключен к второму входу разрядного счётчика, причем выходы блока считывания подключены к соответствующим входам блока счетчиков, выходы которого по ключены к соответствующим входам де шифратора, соответствующие группы выходов которого через блок элементов ИЛИ подключены к первым входам соответствующих ключей, причем тактовые импульсы поданы через делител частоты на вход управляющего счетчика, выход которого через второй э мент задержки подключен к сбросовым входам блока счетчиков и к управляю щим входам ключей, введены счетчик одиночных сигналов, элемент ИЛИ, элементы запрета, счетчик интервалов, управляющий счетчик, элемент совпадения и элемент задержки, при этом выход сдвигового -регистра подключен к первому входу дополнительного элемента ИЛИ, к первому входу первого дополнительного элемента со падения, к первому входу второго эл мента запрета и к первому входу дополнительного элемента запрета, на второй вход которого поданы тактовы импульсы, выход дополнительного эле мента запрета подключен к первому входу дополнительного счетчика интервалов, второй вход которого соед нен с выходом дополнительного элемента ИЛИ, выход дополнительного счетчика интервалов через второй до нолнителыилй элемент совпадения, второй вход которого соединен с выходом счетч1 ка интервалов, и дополнительный элемент задержки подключен к второму зходу второго элемента запрета и к второму нхопу первого дополнительного элемента совпадения, выход которого подключен к первому входу счетчика одиночных сигналов, к второму входу которого подключен выход второго элемента задержки, а выходы разрядов счетчика одиночных сигналов подключены к дополнительным входам дешифратора, причем выход делителя частоты через дополнительный управляющий счетчик подключен к входу первого элемента задержки. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство для контроля состояния каналов связи содержит корреляционный приемник 1, в состав которого входят умножители 2, интеграторы 3 и элемент сравнения 4. Управляющие выходы корреляционного приемни ка 1 подключены к первым входам двух идентичных спусковых схем 5, б, единичные выходы которых подключены к входам первой схемы совпадения 7, а нулевые - к входам второй схемы совпадения 8. Выходы этих схем совпадения подключены к входам первого элемента ИЛИ 9 и через счетчики 10, 11 к входам элемента сравнения 12, выход которого через интегратор 13 подключен к вторым входам спусковых схем 5, 6. Выход первого элемента ИЛИ 9 соединен с входом сдвигового регистра 14, с первым входом счетчика интервалов 15 и через первый элемент запрета 1 6 с вторым входом счетчика интервалов 15. К первому входу разрядного счетчика 17 подключен выход второго элемента запрета 18, а выходы разрядного счетчика подключены к информационным входам блока считывания 19, управляющий вход которого соединен с входом первого элемента задержки 20, выход которого подключен к второму входу разрядного счетчика 17. Выходы блока считывания 19 подключены к входам блока счетчиков 21, выходы которого подключены к входам дешифратора 22, соответствующие группы выходов которого подключены через блок элементов ИЛИ 23 к первым входам ключей 24. Тактовые импульсы подaнFЛ через делитель частоты 25 на вход управляющего счетчика 26, выход которого через второй элемент задержки 27 подключен к сбросовым входам блока счетчиков 2.. Выход сдвигового регистра 14 подключен к первому входу дополнительного элемента ИЛИ 28, к первому входу первого дополнитель- ного элемента совпадения 29, к первому входу второго элемента запрета 18 и к первому входу дополнительног |Элемента запрета 30, на второй вход которого поданы тактовые импульсы. Выход дополнительного элемента запрта 30 подключен к первому входу дополнительного счетчика интервалов 31, выход которого через второй дополнительный элемент совпадения 32 и дополнительный элемент задержки 3 подключен к второму входу второго элемента запрета 18 и к второму входу первого дополнительного элемента совпадения 29. Выход дополнительного элемента совпадения 29 подключен к первому входу счетчика 34 одиночных сигналов, выходы разрядов которого подключены к дополнительным входам дешифратора 22. Выход делителя частоты 25 через дополнительный управляющий счетчик 35 подключен к входу первого элемента задержки 20.

Устройство работает следующим образом.

На вход устройства поступает полезный сигнал и помеха. В умножителях 2 происходит умножение поступающего зашумленного сигнала на эталонные единичный и нулевой сигналы. Случайные величины с выходов интеграторов 3 поступают на входы спусковых схем 5 и 6. Если поступающие на входы этих схем сигналы больще порога, то на единичных выходах этих блоков появляются сигналы, поступающие на входы первой схемы совпадения 7. С выхода этой схемы на вход первого элемента ИЛИ 9 поступают сигналы ненадежного обнаружения первого рода. Если сигналы на входах спусковых схем 5 и 6 меньше порога, то на нулевых выходах этих схем появляются сигналы, которые поступают на входы второй схемы совпадения 8. С выхода этой схемы на вход элемента ИЛИ 9 поступают СНО второго рода. Пусть на выходе элемента ИЛИ 9 появился СНО. Он поступает на запрещающий вход элемента запрета 16, тем самым запрещая прохолщение тактовых импульсов через элемент запрета 16 на вход счетчика интервалов 15. Кроме того, этот же СНО поступает на вход сдвигового регистра 14 и на сбросовый вход счетчика интервалов 15, который тем самым устанавливается в нулевое состояние. Этим же СНО через дополнительный элемент ИЛИ 28 устанавливается в нулевое состояние дополнительный сч-етчик интервалов 31.

Если поступивший СНО одиночный, то он отделен от смежных с ним СНО интервалами пакетообразования большими величины эе. . На следующем такте счетчики интервалов 15 и 31 начнут подсчет тактовыхимпульсов, поступающих на их входы с выходов элементов запрета 16 и 30 соответственно. (Исходное состояние сдвигового регистра нулевое, щпш начальной установки не показаны). Одновременно одиночный СНО, занесенный в сдвиговый регистр 14, продригается по регистру. В момент, когда CFIO окажется в последнем разряде сдвигового регистра 14, т.е. через (Эг1+1) тактов после его поступления в регистр, счетчики интервалов 15 и 31 сосчитывают по (эе+1) тактовых импульсов, и на их выходах появятся импульсы, которые поступят одновременно на оба входа элемента совпадения 32. Импульс с выхода элемента совпадения 32, задержанный на один такт элементом задержки 33, поступит на вход элемента совпадения 29, на другой вход которого одновременно поступит одиночный импульс из регистра 14. Этот импульс поступит на вход счетчика 34 одиночных сигналов. Одновременно импульс с выхода регистра 14, пройдя через дoпoлнитeльн Jй элемент ИЛИ 28, поступит на сбросовый вход дополнительного счетчика интервалов 31. Счетчик интервалов 15 продолжает счет тактовых импульсов. При отсутствии СНО через элементы запрета 16 и 30 будут проходить тактовые импульсы, которые подсчитываются счетчиками интервалов 15 и 31 соответственно. Но так как счет тактовых импульсов они начали в разное время (счетчик интервалов 31 был сброшен сигналом с выхода регистра, а счетчик интервалов 15 не сбрасывался) то появление .сигналов на их выходах будет сдвинуто во времени. Следовательно, на выходе элемента совпадения 32 сигнал будет отсутствовать.

Пусть с выхода элемента ИЛИ 9 поступает пакет СНО. Первый сигнал пакета, записываясь в регистр 14, одновременно сбросит счетчики интервалов 15 и 31 в нулевое состояние

аналогично тому, как и при поступлении одиночного СНО. Элементы запрета 16 и 30 в те моменты времени, 1согда СНО в пакете отсутствуют, будут пропускать тактовые импульсы на входы счетчиков интервалов 15 и 31 соответс.твенно. Но так как интервалы между СНО в пакете не больше величины критерия пакетообразования Эй , то счетчики интервалов 15 и 31, сосчитав в крайнем случае по э€ импульсов, на следующем такте будут сбрасываться СНО, поступающими с выхо;к. элементов ИЛИ 9 и 28 соответственно. Таким образом, при поступлении пакета СНО импульсы на выходе элемента совпадения 32 отсутствуют. C.in ;i Haтельно, СНО пакета с выхода сдвигового регистра .14 проходят черс: злсмснт запрета 18 на вход разрядного счот-. чика 17.и не проходят через элемент

совпадения 29. Последний г.-и.тупакяцгм.о пакета снова сбросит содержимое счетчиков интервалов 15 и 31. IpoxoKflehfHe этого СИО через ре-гкс;тр 14 аналогично прохождению пре лыдуц их СНО пакета и сопровоххдается отсутствием сигнала на выходе элемента задерлски 33, т.е. отсутствием сигнала на запрещающем входе элемен та 18 и на входе элемента совпадения 29. Таким образом, после,цний СНО пакета также заносится в разрядный счетчик 17 (так как он объед няеггся с предпоследним СНО величиHofi интервала пакетообразования Эй ) . С прохождением последнего пакета СИО схемы запрета 18 работа рассмот ренной части схемы осуществляется аналогично. I Таким образом, одиночные СИО (не принадлежащие пакетам) проходят на вход счетчика 34 одиночных сигналов а пакеты СНО проходят на вход разряддного счетчика 17. Разрядньлй счет чик подсчитывает количество СНО в пакетах, принс длежащих принимаемой п - разрядной последовательности элементов. По сигналу управления с вьзхода дополнительного управляющего счетчика- 35, поступаютдего на управляющий вход блока считывания, (этот сигнал соответствует приему п разрядов информации), содержимое разрядного счетчика 17 поступает в блок считывания 19, а счетчик этим же сигналом, поступающим через первый элемент за/держки 20, сбрасывает ся в нулевое состояние. Таким образом, число тактовых им пульсов, зафиксированное в разрядном счетчике 17, соответствует числу единиц в пакетах СНО при приеме п - разрядной последовательности элементов. В зависимости от величины этого числа на одном из выходов блока считывания 19 (по импульсу считывания с выхода дополнительного управляющего счетчика 35) появится импульс, который занесется в соответствующий счетчик блока счетчиков 21. Сигнал на j-м выходе блока считы вания 19 указывает на то, что при приеме п - разрядной последовательности элементов, число СНО, принадлежащих пакетам, равно j, а число импульсов с j-ro выхода блока считывания за интервал измерения пропо ционально частоте появления последо вательности элементов, в которых количество СНО, принадлежащих пакетам, равно JV В коцце контрольного интервала, величина которого определяется коэф фициентом деления делителя частоты 25, и емкостью управляющего счетчика 26f по импульсу с выхода счетчика 26 производится считывание содержимого блока .счетчиков 21 и счетчика одкночнБЖ сигналов, Выходы разрядов 58 этих счетчиков подключены на входы дешифратора 22. Поэтому в зависимости от содержимого этих счетчиков на одном из выходов дешифратора 22 будет сигнал, который через соответствующий элемент ИЛИ блока элементов ИЛИ 23 поступает на вход ключа 29. Выходы дешифратора 22 объединены в К групп с помощью соответствующих элементов ИЛИ, входящих в блок элементов ИЛИ 23 таким образом, что сигнал на К-м выходе блока элементов ИЛИ 23 сигнализирует об определенных диапазонах числовых наборов в счетчиках блока счетчиков 21 и в счетчике 34 одиночных сигналов. Следовательно, в конце каждого контрольного интервала по сигналу управления с выхода управляющего счетчика 26,подаваемому на управляющие, входы ключей 24, на выходе К-го ключа 24 появляется сигнал (подаваемьтй с соответствующего выхода блока элементов ИЛИ 23), указывающийо К-м состоянии канала связи. Тем же сигналом с выхода счетчика 26 через второй элемент задержки 27 блок счетчиков 21 и счетчик 34 одиночных сигналов устанавливаются в нулевое состояние. Формула изобретения Устройство для контроля состояния каналов связи, содержащее корреляционный приемник, управляющие выходы которого подключены к первым входам двух идентичных спусковых схем, единичные выходы которых подключены к входам первой схемы совпадения, а нулевые - к входам второй схемы совпадения, выходы последних подключены к входам первого элемента ИЛИ и через соответствующие счетчики к входам элемента сравнения, выход которого через интегратор подключен к вторым входам спусковых схем, при этом выход первого элемента ИЛИ соединен с входом c двигoвoгo регистра, с, первым входом счетчика интервалов и через первый элемент запрета, на второй вход которого поданы тактовые импульсы, с вторым входом счетчика интервалов, разрядный счетчик, к первому входу которого подключен выход второго элемента запрета, выходы разрядного счетчика подключены к информационным входам блока считывания, управляющий вход которого соединен с входом первого элемента задержки,, выход которого подключен к второму входу разрядного счетчика, причем выходы блока считывания подключены к соответствующим входам блока счетчи,ков, выходы которого подключены к соответствующим входам дешифратора, соответствующие группы выходов кото-рого через блок элементов ИЛИ под96ключены к первым входам соответствую щих ключей, причем тактовые импульсы поданы через делитель частоты на вход управляющего счетчика, выход ко торого через второй элемент задержки подключен к сбросовым входам блока счетчиков и к управляющим входам ключей, отличающеес я тем что, с целью повышения точности контроля, введены счетчики одиночных сигналов, элемент ИЛИ, элементы запрета, счетчик интервалов, управляющий счетчик, элемент совпадения и элемент задержки, при этом выход сдвигового регистра подключен к первому входу дополнительного элемента ИЛИ, к первому входу первого дополнительного элемента совпадения, к первому входу второго элемента запрета и к первому входу дополнительного элемента запрета, на второй вход которого поданы тактовые импуль сы, выход дополнительного элемента запрета подключен к первому входу дополнительного счетчика интервалов, второй вход которого соединен с вы5ходом дополнительного элемента ИЛИ, выход дополнительного счетчика интервалов через второй дополнительный элемент совпадения, второй вход которого соединен с выходом счетчика интервалов, и дополнительный элемент задержки подключен к второму входу второго элемента запрета и к второму входу первого дополнительного элемента совпадения, выход которого подключен к первому входу счетчика одиночных сигналов, к второму входу которого подключен выход второго элемента задержки, а выходы разрядов счетчика одиночных сигналов подключены к дополнительным входам дешифратора, причем выход делителя частоты через дополнительный управляющий счетчик подключен к входу первого элемента задержки. Источники информации, принятые во внимание при экспертизе 1. Заявка tJ 2311653/09, кл. Н 04 В 3/46, 23.08.76, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля состояния канала связи | 1976 |

|

SU568170A2 |

| Устройство контроля состоянияКАНАлА СВязи | 1979 |

|

SU809594A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1998 |

|

RU2137312C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| Многоканальное устройство для локации источников акустической эмисии | 1983 |

|

SU1149159A1 |

| Устройство для измерения коэффициента ошибок в цифровых системах передачи | 1984 |

|

SU1177920A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Приемник последовательного кода | 1988 |

|

SU1674378A1 |

Авторы

Даты

1979-04-30—Публикация

1976-11-15—Подача