16.1 1G.2

Ю-п

Ё

9 20 21 22

23

ON VI 4 СО VI 00

Изобретение относится к вычислительной технике и может быть использовано для формирования и передачи информационных слов последовательным двухполярным кодом по информационным каналам связи. Целью изобретения является расширение области применения путем обеспечения режима многоканального приема информации.

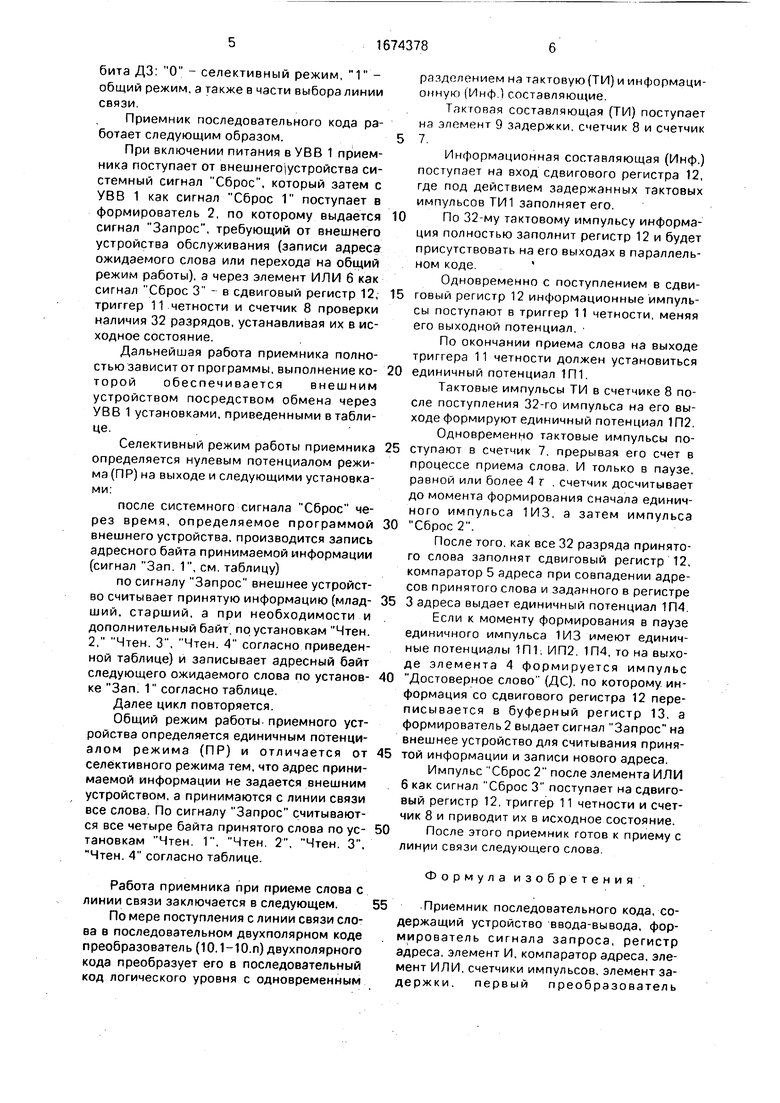

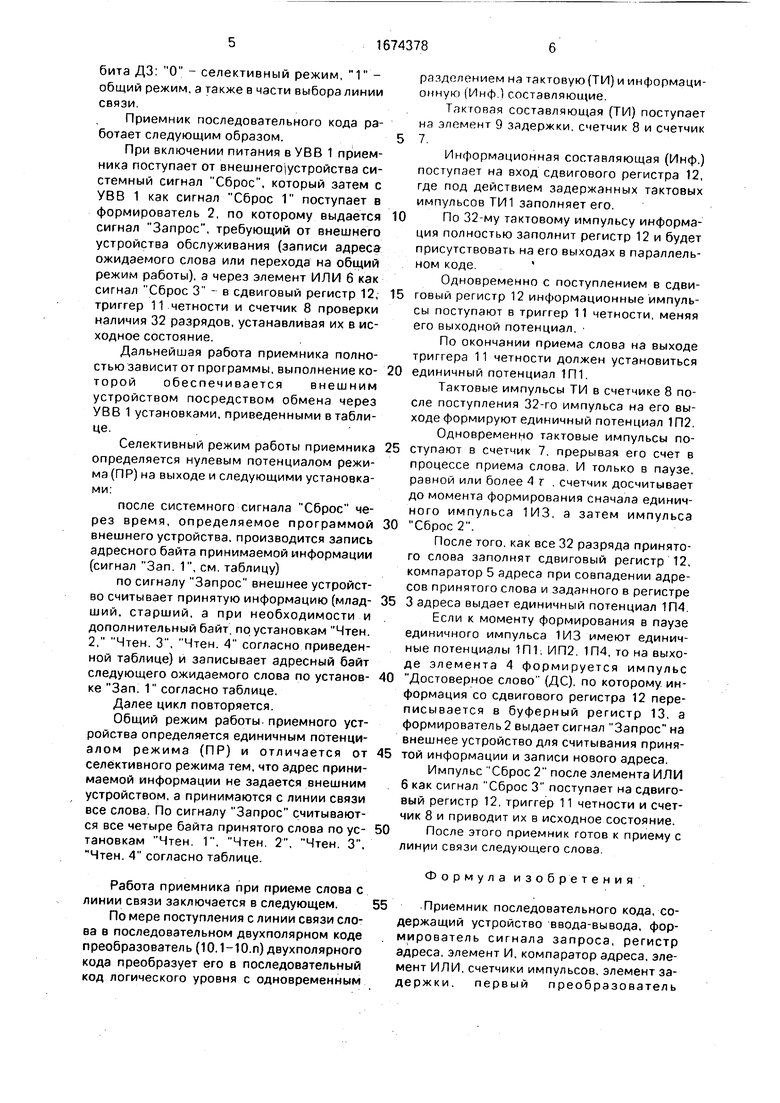

На чертеже представлена функциональная блок-схема приемника.

Приемник содержит устройство 1 ввода-вывода, формирователь 2 сигнала запроса, регистр 3 адреса, элемент И 4, компаратор 5 адреса, элемент ИЛИ 6, первый и второй счетчики 7 и 8 импульсов, элемент 9 задержки, первый - п-й преобразователи 10.1 - 10.п двухполярного кода, триггер 11 четности, сдвиговый регистр 12, буферный регистр 13, дешифратор 14, регистр 15 управления, первый - п-й информационные входы 16.1 - 16.п. входы- выходы 17 данных, адресные входы 18, первый - пятый управляющие входы 19-23 и выход 24 запроса.

Устройство 1 ввода-вывода (УВВ) обеспечивает согласование приемника с внешними устройствами по входу-выходу 17 данных ДО ... Д7, входу 18 адреса АО ... А2 и входам 19-22 управления: выбор модуля (ВМ), Запись, Чтение, Сброс.

Формирователь 2 сигнала запроса предназначен для формирования сигнала запроса на обслуживание внешних устройств по сигналам Сброс 1 (в начальный период работы) и по сигналу ДС (по принятии достоверного слова) и снятия его по сигналам Зап. 1 (запись адресного байта в регистр 3 адреса при селективном приеме), Зап. 2 (запись команды в регистр 15 управления приемом при переходе на общий режим приема), Чт, 1 (при чтении адресного байта с буферного регистра 13 при общем режиме приема).

Регистр 3 адреса обеспечивает запись и хранение 8 разрядов адреса, записываемых через устройство 1 ввода-вывода.

Элемент И 4 при наличии всех единичных потенциалов (четыре признака достоверности принятого слова) выдает сигнал ДС на перезапись параллельного 32-разрядного кода принятого слова из сдвигового регистра 12 в буферный регистр 13 и на формирователь 2 сигнала запроса.

Компаратор 5 адреса служит для сравнения адреса, заданного в регистре 3 адреса, и адреса, принятого в последовательном формате с линии связи. При совпадении адресов выдается единичный потенциал 1П4 на элемент И 4, который является признаком достоверности принятого с линии связи информационного слова.

Первый счетчик 7 импульсов методом подсчета импульсов в промежутках между

тактовыми импульсами принимаемого пакета определяет паузу между словами (промежуток, равный или более 4г ) и по истечении2/3 от 4 г формирует импульс достоверности наличия паузы, а затем импульс сброса (Сб. 2), устанавливающий через элемент ИЛИ 6 приемник в исходное состояние.

Второй счетчик 8 импульсов методом подсчета тактовых импульсов (ТИ) формирует единичный потенциал по наличию в принятом пакете 32 импульсов, характеризующих следующий признак достоверности принятого слова.

Элемент 9 задержки предназначен для

задержки импульсов тактовой составляющей относительно импульсов информационной составляющей, поступающих с преобразователей 10.1-10.п, для обеспечения достоверного приема информации

сдвиговым регистром 12.

Преобразователи 10.1 -10.п предназначены для преобразования двухполярного трехуровневого кода RZ. поступающего с линии связи, в последовательный код уровня ТТЛ с разделением его на тактовую и информационную составляющие, а также для согласования приемника, совместно с которым работает данный преобразователь, с информационной шиной, выполненной в виде витой экранированной пары проводов.

Триггер 11 четности методом подсчета единичных импульсов информационного пакета (Инф.) формирует единичный потенциал четности, характеризующий один из признаков достоверности принятого слова. Сдвиговый регистр 12 (32-разрядный) служит для преобразования последовательного кода информации, принимаемого с линии связи, в параллельный.

Буферный регистр 13 (32-разрядный) служит для хранения 32 разрядов вводимой информации, принятой прием ни ком с линии 0 связи.

Дешифратор 14 обеспечивает формирование одного из восьми, например, потенциалов разрешения приема в зависимости от кода, записанного в регистр 15 управле- 5 ния.

Регистр 15 управления приемом обеспечивает запоминание команды через устройство 1 ввода-вывода в части выбора режима работы приемника по состоянию

бита ДЗ. О селективный режим, 1 - общий режим, а также в части выбора линии связи

Приемник последовательного кода работает следующим образом.

При включении питания в УВВ 1 приемника поступает от внешнегО|устройства системный сигнал Сброс, который затем с УВВ 1 как сигнал Сброс 1 поступает в формирователь 2. по которому выдается сигнал Запрос, требующий от внешнего устройства обслуживания (записи адреса ожидаемого слова или перехода на общий режим работы), а через элемент ИЛИ 6 как сигнал Сброс 3 - в сдвиговый регистр 12, триггер 11 четности и счетчик 8 проверки наличия 32 разрядов, устанавливая их в исходное состояние.

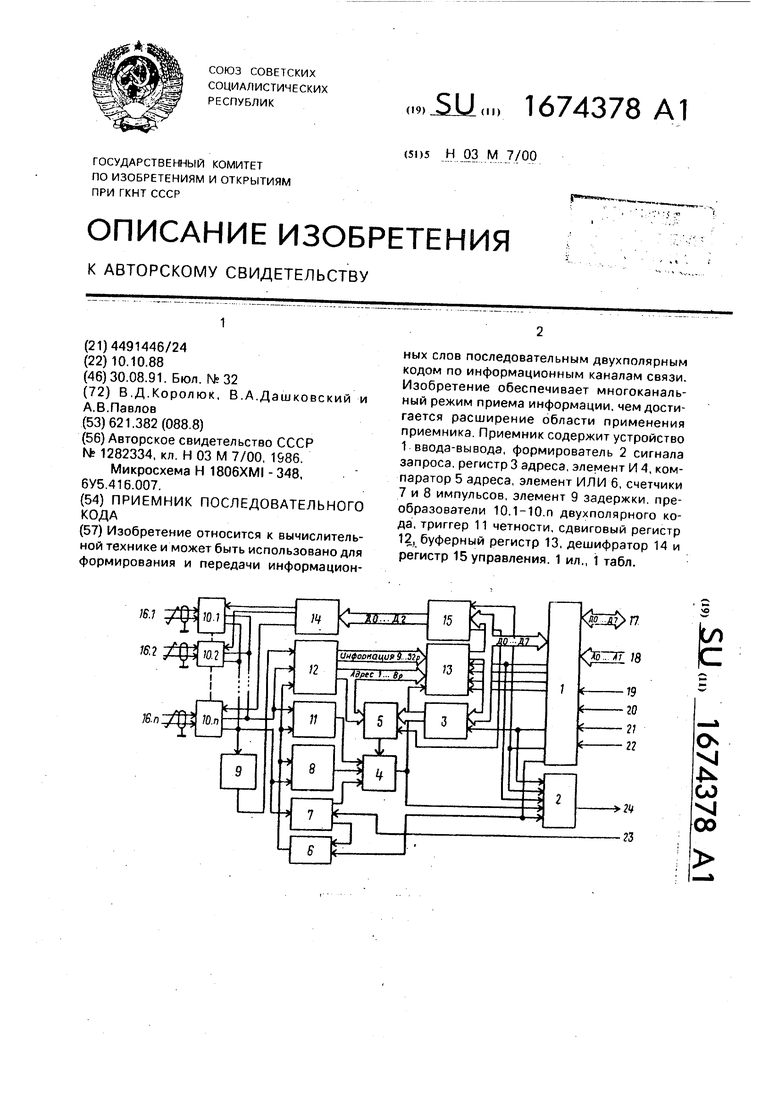

Дальнейшая работа приемника полностью зависит от программы, выполнение ко- торой обеспечивается внешним устройством посредством обмени через УВВ 1 установками, приведенными в таблице.

Селективный режим работы приемника определяется нулевым потенциалом режима (ПР) на выходе и следующими установками

после системного сигнала Сброс через время, определяемое программой внешнего устройства, производится запись адресного байта принимаемой информации (сигнал Зап 1, см. таблицу)

по сигналу Запрос внешнее устройство считывает принятую информацию (младший, старший, а при необходимости и дополнительный байт по установкам Чтен. 2, Чтен 3, Чтен. 4 согласно приведенной таблице) и записывает адресный байт следующего ожидаемого слова по установке Зап. 1 согласно таблице.

Далее цикл повторяется.

Общий режим работы приемного устройства определяется единичным потенциалом режима (ПР) и отличается от селективного режима тем, что адрес принимаемой информации не задается внешним устройством, а принимаются с линии связи все слова По сигналу Запрос считываются все четыре байта принятого слова по установкам Чтен 1, Чтен. 2, Чтен. 3, Чтен. 4 согласно таблице.

Работа приемника при приеме слова с линии связи заключается в следующем.

По мере поступления с линии связи слова в последовательном двухполярном коде преобразователь (10.1-10.л) двухполярного кода преобразует его в последовательный код логического уровня с одновременным

разделением на тактовую (ТИ) и информационную (Инф ) составляющие

Тлкговая составляющая (ТИ) поступает ня элемент 9 задержки, счетчик 8 и счетчик 5 7

Информационная составляющая (Инф.) поступает на вход сдвигового регистра 12, где под действием задержанных тактовых импульсов ТИ1 заполняет его. 10По 32-му тактовому импульсу информация полностью заполнит регистр 12 и будет присутствовать на его выходах в параллельном коде

Одновременно с поступлением в сдви- 15 говый регистр 12 информационные импульсы поступают в триггер 11 четности, меняя его выходной потенциал

По окончании приема слова на выходе триггера 11 четности должен установиться 0 единичный потенциал 1П1

Тактовые импульсы ТИ в счетчике 8 после поступления 32-го импульса на его выходе формируют единичный потенциал 1П2. Одновременно тактовые импульсы по- 5 ступают в счетчик 7. прерывая его счет в процессе приема слова И только в паузе. равной или более 4 г . счетчик досчитывает до момента формирования сначала единичного импульса 1ИЗ а затем импульса 0 Сброс 2.

После того, как все 32 разряда принятого слова заполнят сдвиговый регистр 12. компаратор 5 адреса при совпадении адресов принятого слова и заданного в регистре 5 3 адреса выдает единичный потенциал 1П4 Если к моменту формирования в паузе единичного импульса 1ИЗ имеют единичные потенциалы 1П1 ИП2 1П4. то на выходе элемента 4 формируется импульс 0 Достоверное слово (ДС). по которому информация со сдвигового регистра 12 переписывается в буферный регистр 13. а формирователь 2 выдает сигнал Запрос на внешнее устройство для считывания приня- 5 той информации и записи нового адреса.

Импульс Сброс 2 после элемента ИЛИ 6 как сигнал Сброс 3 поступает на сдвиговый регистр 12. триггер 11 четности и счетчик 8 и приводит их в исходное состояние. 0После этого приемник готов к приему с

линии связи следующего слова

Формула изобретения

5Приемник последовательного кода, содержащий устройство ввода-вывода, формирователь сигнала запроса, регистр адреса, элемент И. компаратор адреса, элемент ИЛИ, счетчики импульсов, элемент задержки, первый преобразователь

двухполярного кода, информационный выход которого соединен с первыми входами триггера четности и сдвигового регистра, информационные выходы которого соединены с соответствующими информационными входами буферного регистра, входы первого преобразователя двухполярного кода являются первым информационна входом приемника, входы выбора модуля, записи, чтения и сброса устройства ввода- вывода являются соответственно первым - четвертым управляющими входами приемника, входы-выходы устройства ввода-вывода являются входами-выходами данных приемника, адресные входы устройства ввода-вывода являются адресными входами приемника, отличающийся тем, что, с целью расширения области применения приемника за счет многоканального приема информации в двух режимах - селективном и общем, в приемник введены второй -- гцй преобразователи двухполярного кода (п 1, N), дешифратор и регистр управления, первые выходы которого соединены с соответствующими входами дешифратора, выходы которого соединены с входами разрешения одноименных преобразователей двухполярного кода, тактовые выходы которых объединены и соединены непосредственно с первыми входами первого и второго счетчиков импульсов и через элемент задержки с вторым входом сдвигового регистра, адресные выходы которого соединены с соответствующими адресными входами буферного регистра и первыми входами компаратора адреса, выход которого соединен с первым входом элемента И, выходы буферного регистра соединены с входом данных устройства ввода- вывода, первыми входами регистра управления и первыми входами регистра

адреса, выходы которого соединены с вто рыми входами компаратор) адреса, первый выход первого счетчика импульсов соединен с первым входом элемента ИЛИ выход

которого соединен с вторыми входами вто рого счетчика импульсов и триггера четности и третьим входом сдвигового регистра, второй выход первого счетчика импульсов и выходы второго счетчика импульсов и триггера четности соединены соответственно с вторым, третьим и четвертым входами элемента И, выход которого соединен с управляющим входом буферного регистра и первым входом формирователя сигнала запроса, выход которого является выходом запроса приемника втором выход регистра управления соединен с третьим входом компаратора адреса, первый - четвертый выходы чтения устройства ввода-вывода

соединены с одноименными входами управления буферного регистра, первый выход записи устройства ввода вывода соединен с вторыми входлми регистра адреса , Формирователя сигналя запроса, второй выход записи устройства ввода-ВЫРПДЯ соединен с вторым входом регистра управления и третьим входом формирователя сигнала за проса, выход сброса устройства ввода-вывода соединен с вторым входом элемента И ПИ

и четвертым входом формирователя сигнала запроса, пятый вход которою подключен к первому выходу чтения устройства ввода-вывода, информационные выходы второго п-то преобразователей двухполярного кода подключены к первым входам сдвигового регистра и триггера четности, входы второго п-го преобразователей двухполярного кода являются вторым - n-м информационными входами приемника второй вход первого счетчика

импульсов является пятым управляющим пхо- дом приемника.

| название | год | авторы | номер документа |

|---|---|---|---|

| Передатчик последовательного кода | 1988 |

|

SU1683177A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

Изобретение относится к вычислительной технике и может быть использовано для формирования и передачи информационных слов последовательным двухполярным кодом по информационным каналам связи. Изобретение обеспечивает многоканальный режим приема информации, чем достигается расширение области применения приемника. Приемник содержит устройство 1 ввода-вывода, формирователь 2 сигнала запроса, регистр 3 адреса, элемент И 4, компаратор 5 адреса, элемент ИЛИ 6, счетчики 7 и 8 импульсов, элемент 9 задержки, преобразователи 10.1 - 10.N двухполярного кода, триггер 11 четности, сдвиговый регистр 12, буферный регистр 13, дешифратор 14 и регистр 15 управления. 1 ил.

Управление

Запись ГЧтение A1

-,--- „-- -1 - 3- .- 4-у

1 оГ

2

Z

О

6 О

Сиг нал

1

Зап. Г

Зап.2

Установка

Запись адресного байта принимаемой информации Установка режима приема и выбор Л ПИ при ДЗ О, общий режим Л1 - 1, Селрктир.- нь1й

Продолжение таблицы

| Декодирующее устройство | 1985 |

|

SU1282334A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Способ подготовки глины для глинобитных, саманных и т.п. построек из необожженной глины | 1924 |

|

SU1806A1 |

Авторы

Даты

1991-08-30—Публикация

1988-10-10—Подача