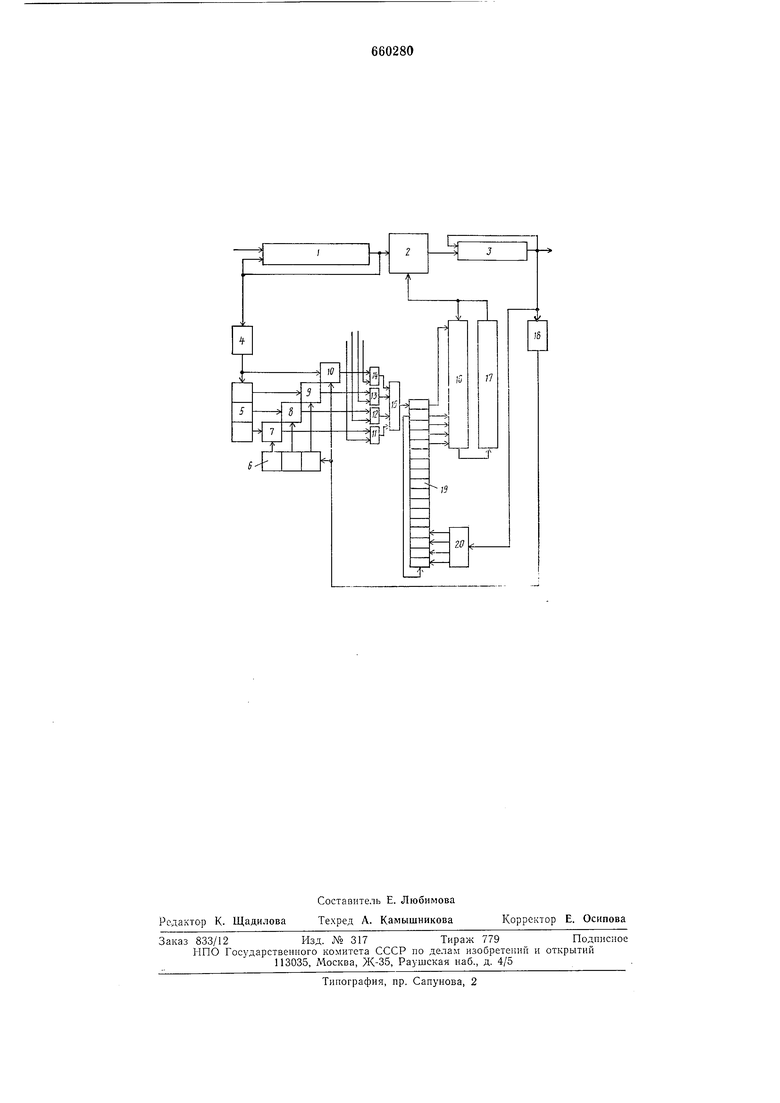

Устройство работает следующим образом.

Очередная выборка сигнала, поступающая с периодом Т из канала связи, содерл ит десять двоичных разрядов. Каждый бит из десятиразрядной выборки сигнала вводится во входной регистр 1, предварительно сдвинув его содержимое на один ряд вправо. При этом содерл имое крайнего правого разряда стирается.

В умножителе 2 производится поочередное умножение всех хранимых во входном регистре 1 выборок сигнала на соответствующие коэффициенты усиления, накапливаемые в регистре 17. Результаты этих умножений суммируются в накопителе 3, с выхода которого по окончании цикла перемножений и суммирований, соответствующего текущему периоду Т, снимается откорректированное значение сигнала для потребителя.

Далее в детекторе 20 анализом откорректированного значения сигнала определяется текущее значение абсолютной величины ошибки, которая заносится в младщие разряды регистра 19. Одновременно с получением абсолютной величины текущей ошибки в блоке 18 определяется ее знак, который поступает на вход регистра 6, содержимое которого предварительно сдвигается на один разряд влево.

В процессе каждого умножения выборки сигнала из входного регистра 1 на соответствующее ему значение коэффициента из регистра 17 в течение цикла, определяемого периодом 7, производится корректирование этого коэффициента, для чего в блоке 4 определяется знак перемнон аемой выборки сигнала, поступающий на вход регистра 5, содерл-симое которого сдвигается на один разряд. Далее следует уточнение коэффициентов зсиления отводов корректора. Для этого текущее значение первого коэффициента из регистра 17 заносится в корректирующий сумматор 16. Затем при появлении управляющего сигнала на входе элемента совпадения И определяется знак приращений коэффициента, записываемый в знаковый разряд регистра 19, старшие разряды которого связаны с входами корректирующего сумматора 16. Взаимное расположение содержимого корректирующего сумматора 16 н суммируемого значения приращения в регистре 19 выбирается таким, чтобы обеспечивалось необходимое взвешивание абсолютного значения ошибки. Полученное таким образом приращение со знаком складывается с содержимым корректирующего сумматора 16.

До появления управляющего сигнала на входе элемента совпадения 12 содержимое

регистра 19 циклически сдвигается так, чтобы против соответствующих входов корректирующего сумматора 16 находилось другое значение абсолютной ошибки, нолученное на последующем цикле работы устройства но отношению к его предыдущему значению. Вычислив очередной знак, полученное приращение складывают с содержимым корректирующего сумматора 16. Таким образом, уточнение коэффициента продолжается до тех пор, пока не закончится полностью щаг коррекции этого коэффициента, значение которого затем списывается в регистр 17.

Уточнение следующего коэффициента усиления отводов начинают с того, что содержимое входного регистра 1 циклически сдвигается на один разряд вправо и в блоке 4 определяется знак очередной текущей

выборки сигнала, а содержимое регистра 5 сдвигается на один разряд. При этом в корректирующий сумматор 16 заносится следующее значение коэффициента из регистра 17. Далее процедура коррекции коэффициента усиления отвода повторяется.

После уточнения последнего коэффициента усиления отвода содержимое регистра 19 дополнительно сдвигается так, чтобы против выходов детектора 20 находилось самое

раннее значение абсолютной ошибки, которое в следующем цикле работы замещается новым текущим значением ошибки с выхода детектора 20.

Формула изобретения

Устройство адаптивной коррекции сигнала по авт. св. № 499681, отличающееся тем, что, с целью сокращения времени коррекции, в него введены регистр приращения коэффициента усиления, детектор сигнала «Ошибка, элемент сборки н четыре элемента совпадения, при этом выход каждого из корреляторов подключен через соответствующий элемент совпадения, на другой вход каждого из которых подан сигнал управления, к входу элемента сборки, выход которого подключен к входу «Знаковый разряд регистра приращения коэффициента усиления, выход «Знаковый разряд которого подключен к входу корректирующего сумматора, выходы старших разрядов регистра приращения коэффициента усиления, один из которых подключен к одному

из входов младших разрядов регистра приращения коэффициента усиления, каждый из которых соединен с соответствующим выходом детектора сигнала «Ошибка, подключены к корректирующему сумматору, а

вход носледнего соединен с выходом накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор цифровых сигналов | 1978 |

|

SU741477A2 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| Адаптивный корректор цифровых сигналов | 1974 |

|

SU519868A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1976 |

|

SU648988A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

Авторы

Даты

1979-04-30—Публикация

1977-11-09—Подача