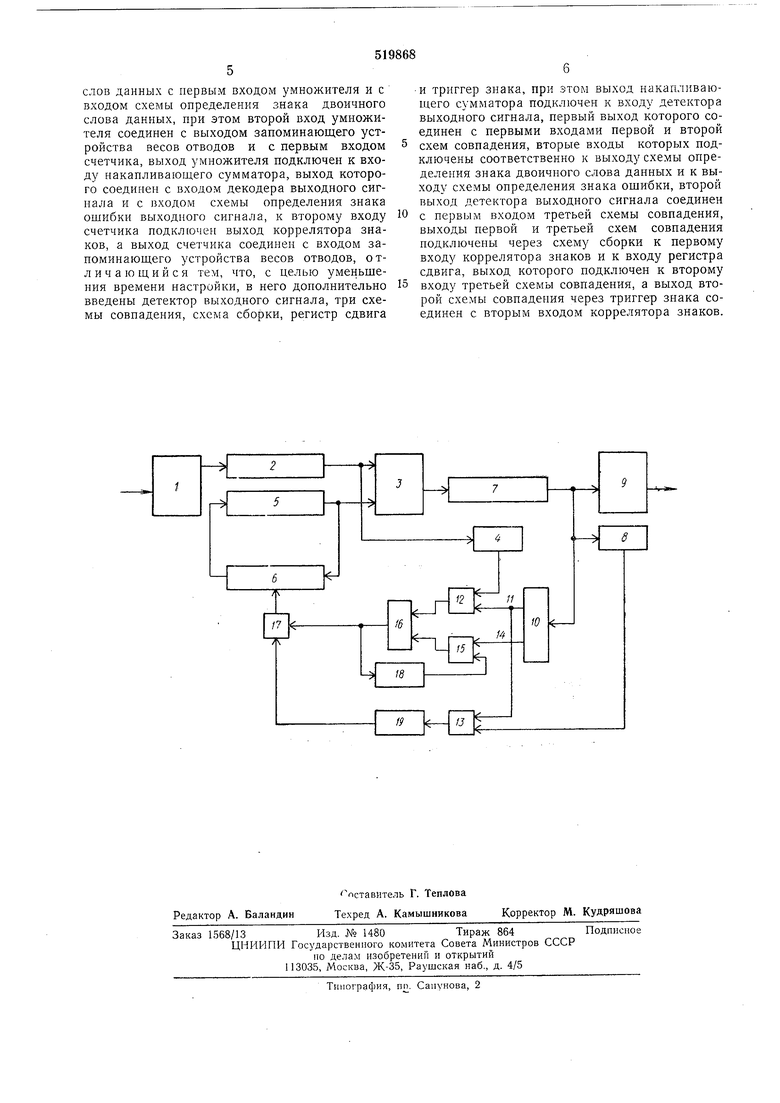

1 ВХОДНОГО сигнала, выход которого соедниен через оапомииающее устройство (ЗУ) 2 двоичных слов данных с нервым входом умножнтеля 3 и с входом схемы 4 определения знака двончного слова данных, при этом второй вход умножителя 3 соединен с выходом ЗУ 5 весов отводов и с первым входом счетчика 6, выход умножителя 3 подключен к входу накапливающего сумматора 7, выход которого соединен с входами схемы 8 определения знака ошибки выходного сигнала, декодера 9 выходного сигнала и детектора 10 выходного сигнала, первый выход 11 которого соединен с-первыми входами первой и второй схем совпадения 12 и 13, вторые входы которых подключены соответственно к выходам схем 4 и 8, второй выход 14 детектора 10 соединен с первым входом третьей схемы совпадения 15, выходы первой и третьей схем совпадения 12 и 15 подключены через схему сборки 16 к первому входу коррелятора 17 знаков и к входу регистра 18 сдвига, выход которого подключен к второму входу третьей схемы совпадения 15, выход второй схемы совпадения 13 через триггер 19 знака соединен с вторым входом коррелятора 17, выход которого подключен к второму входу счетчика 6, выход которого соединен с входом ЗУ 5. Вход аналого-цифрового преобразователя 1 является входом, а выход декодера 9 - выходом корректора. Адаптивный корректор работает следующим образом. Предположим, что в конце предыдущего цикла в результате анализа выходного сигнала накапливающего сумматора 7 выходные сигналы на выходах 11 и 14 детектора 10 соответственно равны 1 и 0. Это означает, что к началу очередного цикла работы адаптивного корректора схемы совпадения 13 и 12 открыты, а схема 15 закрыта. Триггер 19 находится в положении, соответствующем знаку ошибки, который определяется в конце предыдущего цикла в схеме 8. Очередной текущий цикл работы устройства начинается с появления на входе корректора сигнала, который цосле преобразования в аналого-цифровом преобразователе 1 в двоичном коде поступает на вход ЗУ 2 двоичных слов данных. Содержимое ЗУ 2 перед записью очередного слова данных с выхода преобразователя 1 сдвигается па один такт. Далее следует процедура вычисления выравниваемого значения сигнала. Для этого на каждом подцикле, количество которых на один больше числа отводов адаптивного корректора, производится попарное перемножение двоичных слов данных из ЗУ 2 с соответствующими словами весов отводов из ЗУ 5 в умножителе 3. Результаты всех произведений суммируются в накапливающем сумматоре 7, содержимое которого очищается в начале каждого цикла. Цикл состоит из подциклов. На протяжении каждого подцикла в процессе перемножения двоичного слова данных из ЗУ 2 и соответствующего ему слова веса из ЗУ 5 производится настройка адаптивного корректора, заключающаяся в уточнен; и значения этого слова веса с целью минимизации искажений на выходе корректора. Для этого данное слово веса, одновременно с выдачей в умножитель 3, поступает .в счетчик 6, а соответствующее ему двоичное слово данных- в схему 4 для определения знака. Знак двоич«ого слова данных с выхода схемы 4, пройдя открытую схему совпадения 12 и схему сборки 16, поступает на один из входо1В (коррелятора 17, на другой вход которого подается знак ошибки с триггера 19. Одновременно знак двоичного слова данных поступает на хранение в регистр 18. В соответствии с результато м корреляции знака ош1иб1КИ и знака двоичного слова данных производится изменение содержимого счетчика 6 на величииу шага приращения слова веса. Далее после уточнения слово веса из счетчика 6 заносится в ЗУ 5. После того, .как в течение дикла будут -поларно ineремножены все двоичные слова данных с соответствующими весами отводов, на выходе накапливающего сумматора 7 образуется искомая сумма, равная выравненному значению принимаемого сигнала, которое затем декодируется декодером 9. Па выходе корректора получается значение передаваемого сигнала. К этому моменту в регистре 18 находится вся последовательность знаков двоичных слов данных в том порядке, в котором находились слова данных в ЗУ 2 на протяжении текущего цикла работы корректора. Аналогично предыдущему в конце текущего цикла одновременно с декодированием анализируется выходной сигнал накапливающего сумматора 7 детектором 10. При значении выходного сигнала, попадающем в зону нечувствительности, сигналы на выходах 11 и 14 детектора 10 равны О и 1. Это обеспечивает блокировку схем совпадения 13 и 12 на протяжении следующего цикла. При этом схема 15 открыта. Предыдущее значение знака ошибки сохраняется в триггере 19. Теперь в процессе следующего цикла перемножения двоичных слов данных из ЗУ 2 на слова весов из ЗУ 5 при уточнении каждого слова веса будет сделан повторный щаг настройки, соответствующий настройке в прошедшем цикле, и так до тех пор, пока значение выходного сигнала накапливающего сумматора 7 не выйдет из зоны нечувствительности, после чего вновь обновится содержимое регистра 18 и триггера 19. В результате получение ошибочного символа на выходе накапливающего сумматора 7, обусловленное большими искажениями в канале передачи, не вызыает ложного шага настройки адаптивного орректора. Время настройки сокращается. Формула изобретения Адаптивный корректор цифровых сигналов, одержащий аналого-цифровой преобразоваель входного сигнала, выход которого соедиен через запоминающее устройство двоичных

слов данных с первым входом умножителя и с входом схемы определения знака двоичного слова данных, при этом второй вход умножителя соединен с выходом запоминающего устройства весов отводов и с первым входом счетчика, выход умножителя подключен к входу накапливающего сумматора, выход которого соединен с входом декодера выходного сигнала и с входом схемы определения знака ошибки выходного сигнала, к второму входу счетчика подключен выход коррелятора знаков, а выход счетчика соединен с входом запоминающего устройства весов отводов, отличающийся тем, что, с целью уменьшения времени настройки, в него дополнительно введены детектор выходного сигнала, три схемы совпадения, схема сборки, регистр сдвига

6

и триггер знака, при зтом выход накапливающего сумматора подключен к входу детектора выходного сигнала, первый выход которого соединен с первыми входами первой и второй схем совпадения, вторые входы которых подключены соответственно к выходу схемы определения знака двоичного слова данных и к выходу схемы определения знака ошибки, второй выход детектора выходного сигнала соединен с первым входом третьей схемы совпадения, выходы первой и третьей схем совпадения подключены через схему сборки к первому входу коррелятора знаков и к входу регистра сдвига, выход которого подключен к второму входу третьей схемы совпадения, а выход второй схемы совпадения через триггер знака соединен с вторым входом коррелятора знаков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор цифровых сигналов | 1978 |

|

SU741477A2 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство адаптивной коррекции сигнала | 1977 |

|

SU660280A2 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Цифровой коррелятор | 1979 |

|

SU842768A1 |

| Адаптивный корректор фазомодули-рованных сигналов | 1974 |

|

SU508944A1 |

| Цифровой нелинейный корректор сигнала | 1982 |

|

SU1075423A1 |

| Система передачи данных | 1989 |

|

SU1728976A2 |

Авторы

Даты

1976-06-30—Публикация

1974-12-23—Подача