(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ / @ | 1981 |

|

SU1015374A1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления быстрого преобразования Фурье | 1983 |

|

SU1124323A1 |

| Устройство для вычисления коэффициентов-фурье | 1982 |

|

SU1049920A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1999 |

|

RU2190874C2 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

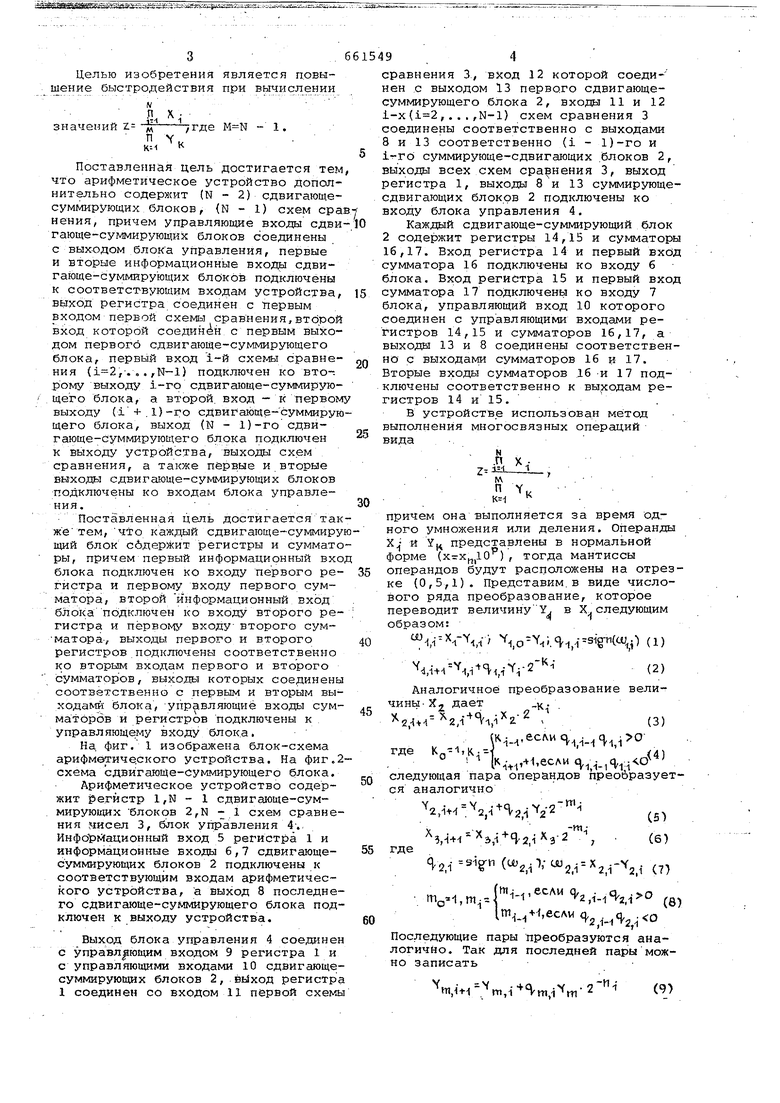

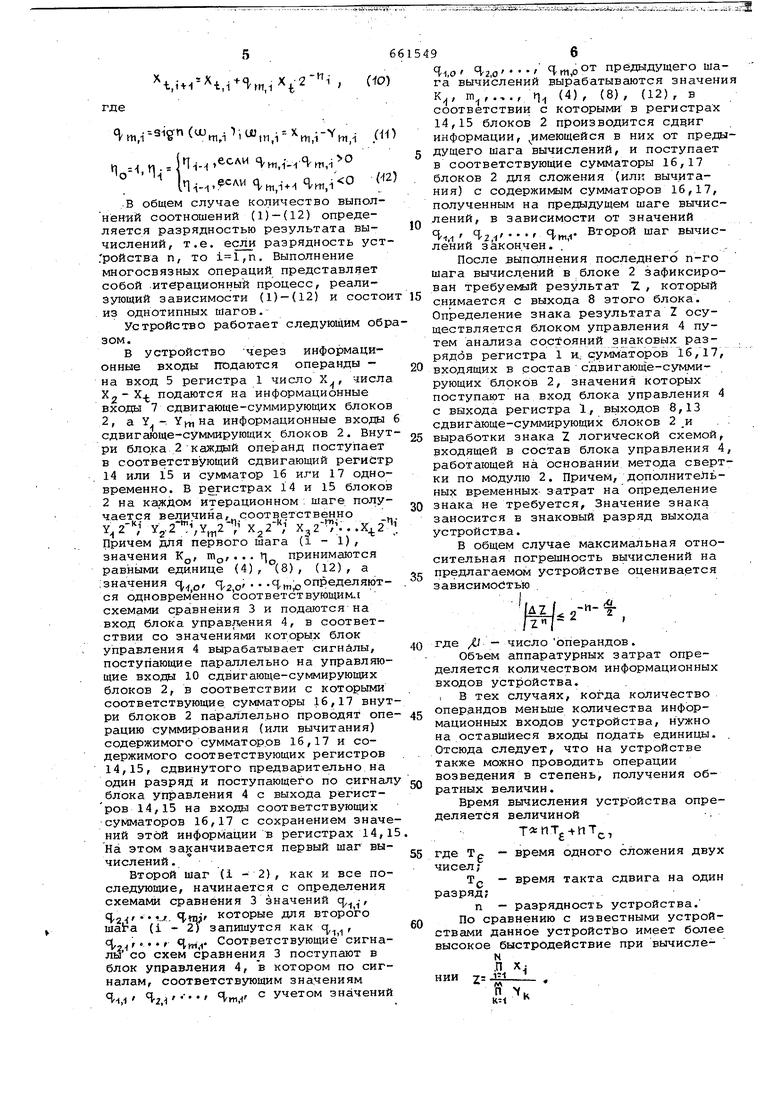

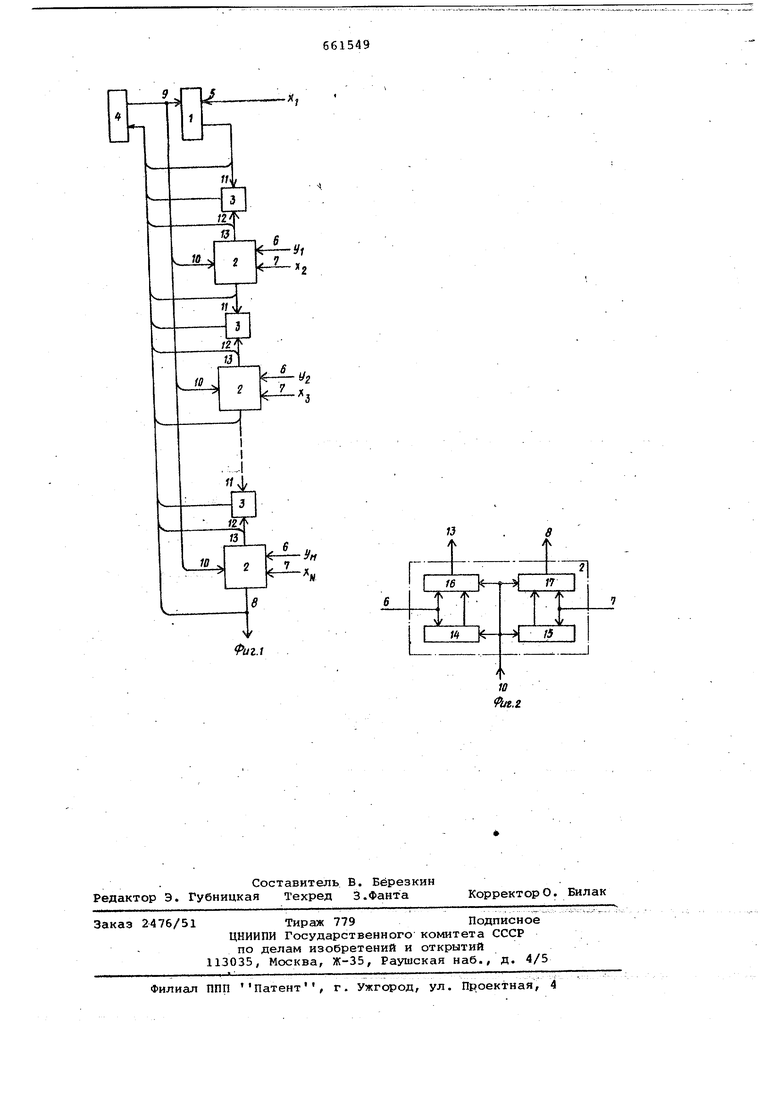

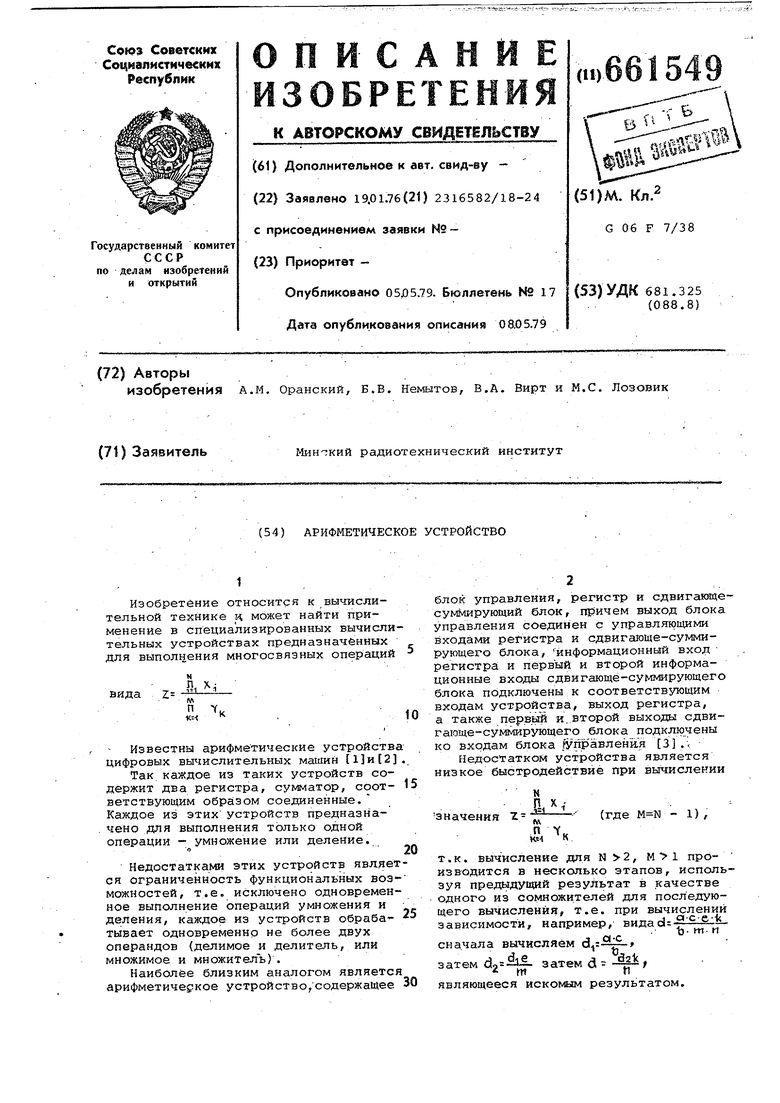

Изобретение относится к вычислительной технике н может найти применение в специализированных вычисли тельных устройствах предназначенных для выполнения многосвяэных операций . JaJiL вида Z Известны арифметические устройств цифровых вычислительных машин Так каждое из таких устройств содержит два регистра, сумматор, соответствующим образом соединенные. Каждое из этих устройств предназначено для выполнения только одной операции - умножение или деление. Недостатками этих устройств являе ся ограниченность функциональных воз можностей, т.е. исключено одновремен ное выполнение операций умножения и деления, каиодое из устройств обрабатывает одновременно не более двух операндов (делимое и делитель, или множимое и множителТь) . Наиболее близким аналогом являетс арифметиче$;кое устройство/содержащее блок управления, регистр и сдвигающесуммирующий блок, причем выход блока управления соединен с управляю1дими входами регистра и сдвигающе-суммирующего блока, информационный вход регистра и первый и второй информационные входы сдвигающе-суммирующего блока подключены к соответствующим входам устройства, выход регистра, а также первый и,.второй выходы сдвигающе-суммирующего блока подключены ко входам блока управленй.я 3. Недостатком устройства является низкое быстродействие при вычислении (где значеният.к. вычисление для N 2, М 1 производится в несколько этапов, используя предыдущий результат в качестве одного из сомножителей для последующего вычисления, т.е. при вычислений зависимости, например, видасЗ-- fa. ж. и сначала вычисляем d:,:--- затем dy- затем d -4й HI П являющееся иског ым результатом. Целью изобретения является повышение быстродействия при вычислении W Ч значений z - где - 1 Поставленная цель достигается тем что арифметическое устройство дополнительно содержит (N - 2) сдвигающесуммирующих блоков, {N - 1) схем сра нения, причем управляющие входы сдви гающе-суммиругок их блоков соединены с выходом блока управления, первые и вторые информационные входы сдвигающе-суммирующих блоков подключены к соответствующим входам устройства, выход регистра соединен с первым входом первой схемы сравнения,второй вход которой соединен с первым выходом первого cдвигaюI e-cyм 1иpyющeгo блока, первый вход 1-й схемы сравнения (,-. ,. ,N-1) подключен ко вто-. рому выходу i-ro сдвига1още-су1Фшрую. щего блока, а второй, вход - к первом выходу (i+.l)-ro сдвнгайще-суммирую щего блока, выход (N 1)-го сдвигающе-суммирующего блока подключен к выходу устройства, выходы схем сравнения, а также первые и вторые выходы сдвигающе-суммирующих блоков подключены ко входам блока управления.. . Поставленная цель достигается так же тем, что каждый сдвигающе-суммиру адий блок сбдержит регистры и суммато ры, причем первый информационный вхо блока подключен ко входу первого регистра и первому входу первого сумматора, второй Информационный вход блока подключен ко входу второго регистра и первому входу второго сумматора-, выходы первого и второго регистров подключены соответственно ко вторым входам первого и второго сумматоров, выходы которых соединены соответственно с первым и вторым выходами блока, -управляющие входы сум маторов и регистров подключены к . управляющему входу блока. На. фиг. 1 изображена блок-схема арифметического устройства. На фиг. схема сдвигающе-суммирующего блока. Арифметическое устройство содержит регистр 1,N - 1 сдвигающе-суммирующих блоков 2,N - 1 схем сравне ния мисел 3, блок управления 4-., Инфop aциoнный вход 5 регистра 1 и информационные входы б,7 сдвигающесуммируювщх блоков 2 подключены к соответствующим входам арифметического устройства, а выход 8 последне го сдвигающе-суммирующего блока под ключен к выходу устройства. Выход блока управления 4 сое,цине с управляющим входом 9 регистра 1 и с управляющими входами 10 сдвигающе суммирующих блоков 2, вЫход регистр 1 соединен со входом 11 первой схем 94 сравнения 3, вход 12 которой соединен с выходом 13 первого сдвигающесуммирующего блока 2, входы 11 и 12 1-х(,...,N-1) схем сравнения 3 соединены соответственно с выходами 8 и 13 соответственно (i - 1)-го и i-гб суммирующе-сдвигающих .блоков 2, выходы всех схем сравнения 3, выход регистра 1, выходы 8 и 13 суммирующесдвигающих блоков 2 подключены ко входу блока управления 4. Каждый сдвигающе-суммирующий блок 2 содержит регистры 14,15 и сумматоры 1б,17. Вход регистра 14 и первый вход сумматора 16 подключ-ены ко входу б блока. Вход регистра 15 и первый вход сумматора 17 подключены ко входу 7 блока, управляющий вход 10 которого соединен с управляющими входами регистров 14,15 и сумматоров 16,17, а выходы 13 и 8 соединены соответственно с выходакш сумматоров 16 и 17. Вторые входы сумматоров 16 -и 17 подключены соответственно к вы.ходам регистров 14 и 15. В устройстве использован метод выполнения многосвязных операций вида . . причем она выполняется за время одного умножения или деления. ОЦеранды X; И Уц представлены в нормальной форме () , тогда мантиссы операндов будут расположены на отрезке (0,5,1). Представим.в виде числового ряда преобразование, которое переводит величину У, в Наследующим образом: .i ,-1- з1€Г И,0 (1) .i.V- inM iАналогичное преобразование величины -Х дает -к . , + ,, (3) (К..,,еслис ;, где Kn-i.K.-f/4) ° l Ч1 ecAиcvv,.,cv,.0 следующая пара операндов преооразуется аналогично . ,2, 2 2,,,1 где (,., (7) moM,, (8) нНесл« 2.д.о Последующие пары преобразуются аналогично. Так для последней пары можно записать m,, t,,,,,-2 Vm,(ni,,,,i W .,.Ц..м Я.т,1-,,1 Я.ж,1 Я.1,1 в общем случае количество выполнёнт1Й соотношений (1) -(12) определяется разрядностью результата вычислений, т.е. если разрядность уст Гройства п, то ,п. Выполнение многосвязных операций представляет собой .итерационный процесс, реализующий зависимости (1)-(12) и состо из однотипных шагов. Устройство работает следующим об зом. В устройство через информационные входы подаются операнды на вход 5 регистра 1 число X,, числ Х - Х подаются на информационные входы 7 сдвигающе-суммирующих блоко 2, а У.-. Y| на информационные входы сдвигающе-суммирующих блоков 2. Вну ри блока 2 каждый операнд поступает в соответствующий сдвигающий регист 14 или 15 и сумматор 16 иги 17 одно временно. В регистрах 14 и 15 блоко 2 на каждом итерационном, шаге полу чается величина,,,соответственно V 7 V V 9 i V 7 I Y у V -j / 2 m 2 Причем для первого шага (i - 1), значения К, га, . .. rj принимаются равными еди.нице (4), (8), (12), а .значения , с,;. . .с{,- О1фер.&пяк тся одновременно соответствующим. схемами сравнения 3 и подаются на вход блока управления 4, в соответствии со значениями которых блок управления 4 вырабатывает сигналы, поступающие параллельно на управляющие входы 10 сдвигающе-суммирующих блоков 2, в соответствии с которыми соответствующие сумматоры 16,17 внут ри блоков 2 параллельно проводят one рацию суммирования (или вычитания) содержимого сумматоров 16,17 и содержимого соответствующих регистров 14,15, сдвинутого предварительно на один разряд и поступающего по сигнал блока управления 4 с выхода регистров 14,15 на входы соответствующих сумматоров 16,17 с сохранением значе ний этой информации в регистрах 14,1 На этом за:канчивается первый шаг вычислений . Второй шаг (i -2), как и все послед5тощие, начинается с определения схемаш сравнения 3 значений t срг( ЯИу которые для второго шаЬа (i - 2) запишутся как q, , с ,. ,., Соответствующие сигналы со схем сравнени я 3 поступают в блок управления 4, в котором по сигналам, соответствующим зна,чениям ,1 2, учетом значений

661549 42,0 Чт.оот предыдущего шага вычислений вырабатываются значения К, т,.,., fi (4) , (8) , (12) , в соответствии с которыми в регистрах 14,15 блоков 2 производится сдвиг информации, имеющейся в них от предыдущего шага вычислений, и поступает в соответствующие сумматоры 16,17 блоков 2 для сложения (или вычитания) с содержимым сумматоров 16,17, полученным на предыдущем шаге вычислений, в зависимости от значений ti,- Ч-2 -( Ят,1 Второй шаг вычислений закончен. После выполнения последнего п-го шага вычисл.ений в блоке 2 зафиксирован требуег.ий результат t , который снимается с выхода 8 этого блока. Оп1ределение знака результата Z осуществляется блоком управления 4 путем анализа состояний знаковых разрядов регистра 1 к сумматоров 16,17, входящих в составсдвигающе-суммирующих блоков 2, значения которых поступают на вход блока управления 4 с выхода регистра 1, выходов 8,13 сдвигающе-суммирующих блоков 2 и . выработки знака Z логической схемой, входящей в состав блока управления 4, работающей на основании метрда свертки по модулю 2. Причем, дополнительных временных- затрат на определение знака не требуется. Значение знака заносится в знаковый разряд выхода устройства. В общем случае максимальная относительная погрешность вычислений на предлагаемом устройстве оценивается зависимостью ,-f где Х - числооперандов. Объем аппаратурных затрат определяется количеством информационных входов устройства. В тех случаях, когда количество операндов меньше количества информационных входов устройства, нужно на оставшиеся входы подать единицы. . Отсюда следует, что на устройстве также можно проводить операции возведения в степень, получения обратных величин. Время вычисления устройства определяется величиной , где Tg - время одного сложения двух чисел; TC время такта сдвига на один разряд; п - разрядность устройства. По сравнению с известными устройствами данное устройство имеет более высокое быстродействие при вычислеФормула изобретения 1. Арифметическое устройство, содержащее блок управления, регистр и сдвигающе-суммирующий блок, гфичем выход блока управления соединен с управляющими входами регистра и сдвигающе-суммиругащего блока, информационный вход регистра и первый и второй информа1дионные входы сдвигающе-суммирующего блока подключены/к соответствующим входам устройства, выход регистра, а также первый и второй выходы сдвигающе-суммирующего блока подключены ко входам управления, о т л и ч а ю щ е е с я , тем, что, с целбю повьзшения быстродействия при вычислении значений {где устройство дополнительно содержит (N - 2) сдвигающе-суммирующих блоков, (N - 1) схемасравнений, причем упрабляющие входы сдвигающе-суммирующих блоков соединены с выходом блок управления, первые и вторые информа ционные входы сдвигающе-суммирующих блоков подключены к соответствующим входам устройства,.выход регистра соединен с первым входом первой схе мы сравнения, второй вход которой соединен с первым выходом первого сдвигающе-суммирующего блока, первый вход i-й схемы сравнения (,N - Iподключен ко второму выходу сдвигающе-суммирующего блока, а вто- . рой вход - к первому выходу (1 + 1)-го сдвигающе-суммирующего блока, выход (N - 1)-го сдвигающе-суммирующего блока подключен к выходу устройства, выходы схем сравнения, а также первые и вторые выхода сдвигающе-суммирующих блоков подключены ко входам блока управления. 2. Арифметическое устройство по п. 1, отличающееся тем, что сдвигающе-суммирующий блок, содержит регистрыи сумматоры, причем первый информационный вход блока подключен ко входу первого регистра и первому входу первого cyMJ iaTopa, второй информационный вход блока подключен ,ко входу второго регистра и первому входу второго сумматора, выхо,цы первого и второго регистров подключены соответственно ко вторым входам первого и второго сумматоров, выходы которых соединены соответственно с первым и вторым выходами блока, управляющие входы сумг- аторов и регистров подключены к управля.ющему входу блока. . Источники информации, принятые во внимание при экспертизе ,1. Каган Б.М, и др, Цифровые вычислительные машины и системы, М., Энергия, 1973, с, 329-348. 2,Хетагуров Я,А. и др. Основы . инженерного проектирования УЦВМ, М., Сов.рад ио , 1972, с. 142. 3.Авторское свидетельство СССР № 553614, кл. G 06 F 7/38, 1974.

:.J (1

/2ф

13

Ун

10

13

Авторы

Даты

1979-05-05—Публикация

1976-01-19—Подача