1

Изобретение может быть использовано, например, в, микропрограммных устройствах управления.

Известны запоминающие устройства (ЗУ) III 2}.

Одно из известных ЗУ содержит ряд постоянных микропрограмм, адресация к которым может производиться по множеству адресов 1. Недостатком этого устройства являютс большие аппаратурные затраты.

Наиболее близким техническим решением к изобретению является ЗУ, содержащее последовательно соединенные коммутатор адреса операций, регистр адреса операций и дешифратор адреса операций, выходы которого подключены к одним адресным входам накопителя, информационные выходы которого соединены с регистром микрокоманд, и блок управления 2.

БОЛЬШОЙ объем накбпителя такого ЗУ определяется произведением разрядности поля управляющих сигналов на среднее число микрокоманд для каждой из операций и число операций.

Целью изобретения является упрощение устройства за счет сокращения количества оборудования.

Поставленная цель достигается тем, что прёдложеШоё ЗУ содержит последовательно соединенные коммутатор адреса микрокоманд адреса микрокоманд и дешифратор адреса микрокоманд, выходы которого подключены к другим адресным входам накопителя. Входы коммутатора адреса микрокоманд соединены соответственно с

0 одними из выходов регистра микрокоманд и входом ЗУ. Управляющие входы ко|и мутатора адреса микрокоманд и счетчика адреса микрокоманд подключены к выходам блока управления.

5

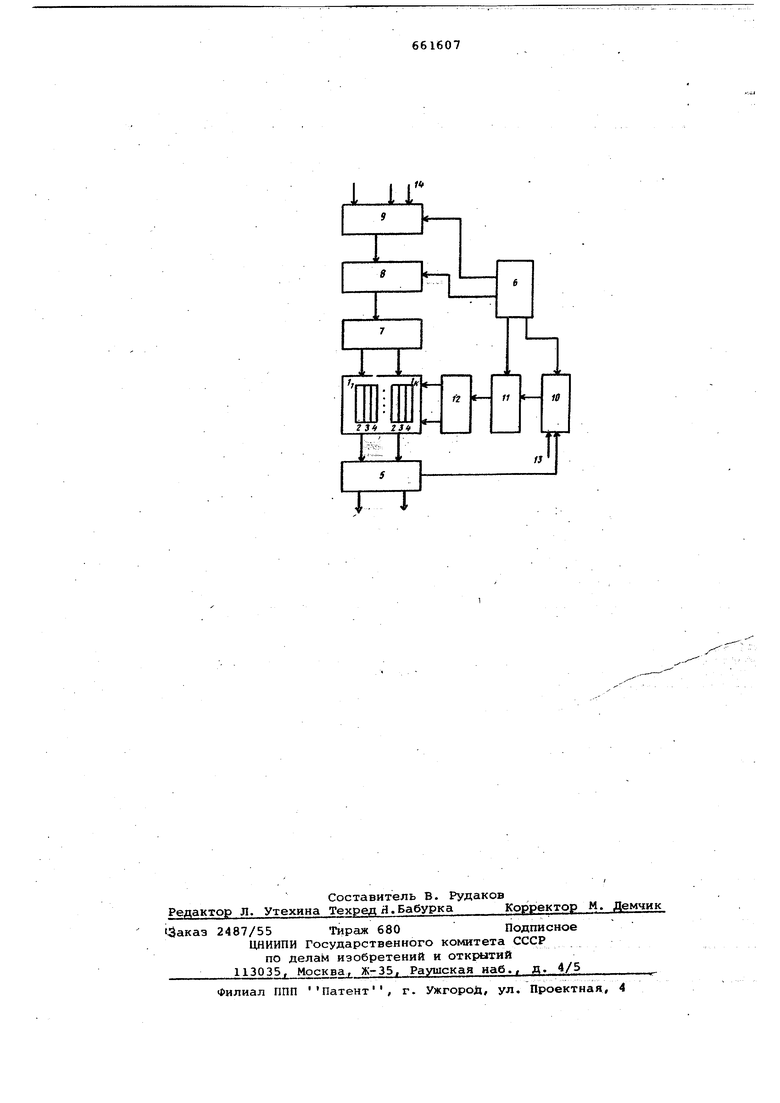

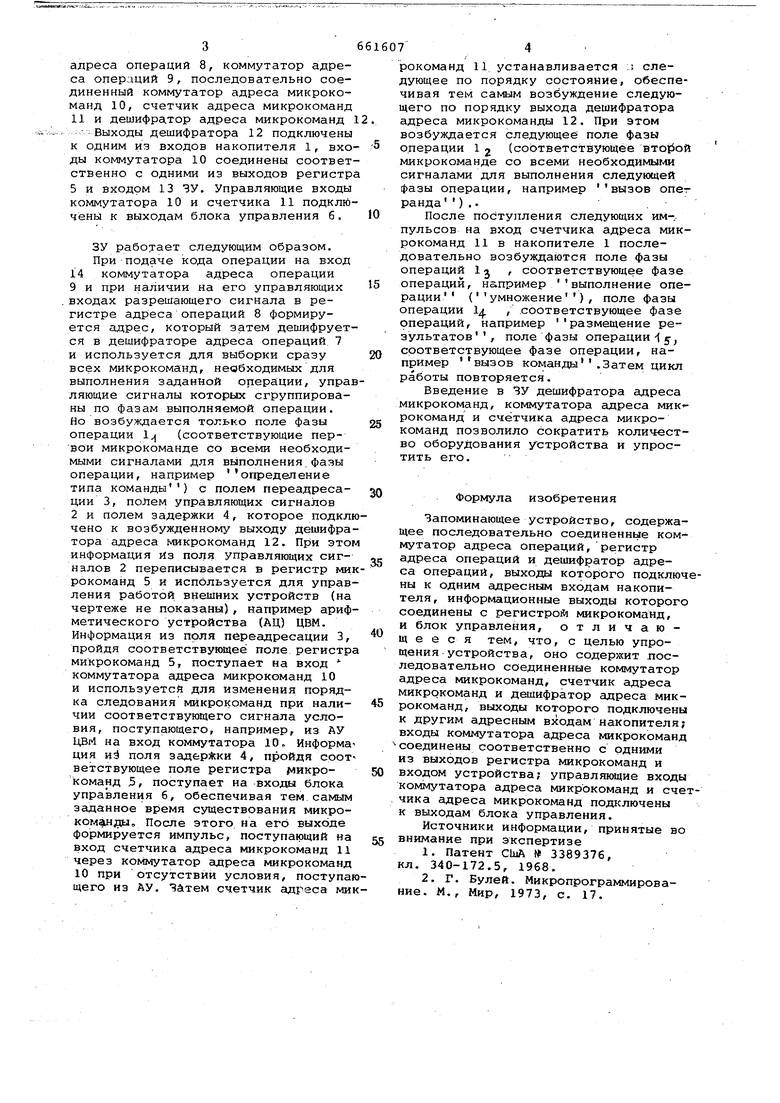

На чертеже изображена структурная схема предложенного ЗУ.

ЗУ содержит накопитель 1, разде- , ленный на К полей фазы операций 1 1ц (где К- число фаз, необходимых

0 для вьлполнения операции типа выборка команды выборка операнда , выполнение операций , формирование команды ).

В состав каждого поля фазы опера5ций входит псэле управляющих сигналов 2, поле переадресации 3 и поле задержки 4.

ЗУ содержит также регистр микрокоманд 5, блок управления 6, де0оифратор адреса операций 7, регистр

адреса операций 8, коммутатор адреса операций 9, последовательно соединенный коммутатор адреса микрокоманд 10, счетчик адреса микрокоманд 11 и дешифра.тор адреса микрокоманд 1

:Выходы дешифратора 12 подключены к одним из входов накопителя 1, входы коммутатора 10 соединены соответственно с одними из выходов регистра 5 и входом 13 ЗУ. Управляющие входы коммутатора 10 и счетчика 11 подключены к выходам блока управления 6,

ЗУ работает следующим образом. При подаче кода операции на вход 14 коммутатора адреса операции 9 и при наличии на его управляющих входах разрешающего сигнала в регистре адреса операций 8 формируется адрес, который затем дешифруется в дешифраторе адреса операций 7 и используется для выборки сразу всех микрокоманд, необходимых для выполнения заданной опера;ции, управляющие сигналы которых сгруппированы по фазам выполняемой операции. Но возбуждается только поле фазы операции 1 (соответствующие первой микрокоманде со всеми необходимыми сигналами для выполнения.фазы операции, например определение типа команды ) с полем переадресации 3, поЛем управляющих сигналов 2 и полем задержки 4, которое подключено к возбужденному выходу дешифратора адреса микрокоманд 12. При этом информация Из поля управляющих сигналов 2 переписывается в регистр микрокоманд 5 и используется для управления работой внешних устройств (на чертеже не показаны), например арифметического устройства (АЦ) ЦВМ. Информация из поля переадресации 3, пройдя соответствуняцее поле регистра микрокоманд 5, поступает на вход коммутатора адреса микрокоманд 10 и используетсй для изменения порядка следования микрокоманд при наличии соответствующего сигнала условия, поступающего, например, из АУ ЦВМ на вход коммутатора 10 Информа ция и поля задержки 4, пройдя соот ветствующее поле регистра иикрокоманд 5, поступает на входы блока упраЗвления 6, обеспечивая тем самым заданное время существования микроком ды. После этого на его выходе формируется импульс, поступающий на вход счетчика адреса микрокоманд 11 через коммутатор адреса микрокоманд 10 при отсутствии условия, поступающего из АУ. ЧАтем счетчик адреса микрокоманд 11 устанавливается .: следующее по порядку состояние, обеспечивая тем самым возбуждение следующего по порядку выхода дешифратора адреса микрокоманды 12. При этом возбуждается следующее поле фазы операции 1 2 (соответствующее микрокоманде со всеми необходимыми сигналами для выполнения следующей фазы операции, например вызов операнда ) ,..

После поступления следующих им-,пульсов на вход счетчика адреса микрокоманд 11 в накопителе 1 последовательно возбуждаются поле фазы операций 1j , соответствующее фазе операций, например выполнение операции (умножение), поле фазы операции 1 , .соответствующее фазе операций, например размещение результатов , поле фазы операции I у; соответствующее фазе операции, например вызов команды .Затем цикл работы повторяется.

Введение в ЗУ дешифратора адреса микрокоманд, коммутатора адреса микрокоманд и счётчика адреса микрокоманд позволило сократить количество оборудования устройства и упростить его.

Формула изобретения

Запоминающее устройство, содержащее последовательно соединенные коммутатор адреса операций, регистр адреса операций и деишфратор адреса операций, выходы которого подключны к одним адресНЕЛМ входам накопителя, информационные выходы которого соединены с регистров микрокоманд, и блок управления, отличающееся тем, что, с целью упрощения-устройства, оно содержит последовательно соединенные коммутатор адреса микрокоманд, счетчик адреса микрокоманд и дешифратор адреса микрокоманд, выходы которого подключены к другим адресным входам накопителя; входы коммутатора адреса микрокоманд соединены соответственно с одними из выходов регистра микрокоманд и входом устройства; управляющие входы коммутатора адреса микрокоманд и счечика адреса микрокоманд подключены к выходам блока управления.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3389376, кл. 340-172.5, 1968.

2.Г. Булей. Микропрограммирование. М., Мир, 1973, с. 17.

I 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1978 |

|

SU742937A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Авторы

Даты

1979-05-05—Публикация

1976-06-14—Подача