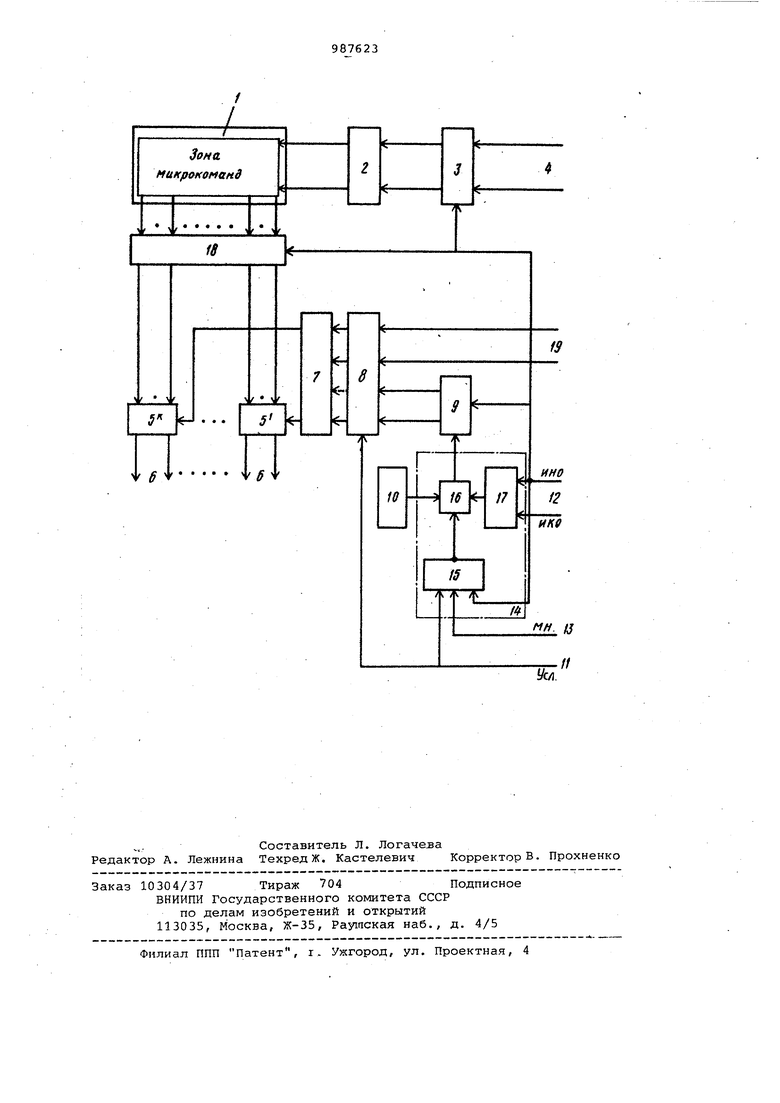

Изобретение относится к вычисли.тельной технике и может быть использо вано в цифровых вычислительных машинах устройствах обработки и отображения информации. Известно микропрограммное устройст во управления, содержащее блок памяти дешифратор адреса операций, блок формирования адреса, дешифратор адреса фаз, коммутатор адресов фаз, регистры адреса фаз, блок управления коммутацией адреса фаз, дешифратор адреса микрокоманд, узел пуска-останова, ком мутатор адресов микрокоманд, регистры адресов микрокоманд, блок управления коммутатором адресов микрокоманд, группы элементов И, регистр микрокоманд 1 . Недостатки этого устройства - боль шой объем оборудования и низкое быстродействие. Наиболее близким к предлагаемому по технической сущности является микропрограммное устройство управления, содержащее запоминающее устройство, адресные шины которого подключены через дешифратор адреса операций и формирователь адреса операций к первым входам микропрограммного устройства управления, К групп элементов И (к - максимальное количество фаз и условных переходов для одной операции), подключенных к первым выходам микропрограммного устройства управления и связанных по цепям управления с выходами дешифратора адреса микрокоманд, коммутатор, счетчик фаз, генератор, узел пуска-останова, связанный со счетным входом счетчика и подключенный к генератору и к вторым входам микропрограммного устройства управления. При этом вторые выходы, групп элементов И связаны через, дешифратор переходов с управляющими шинами коммутатора, информационные входа которого подключены через К регистров адреса переходов к вторым выходам запоминающего устройства C2J. К недостаткам известного устройства относятся низкое быстродействие из-за того, что при формировании каждой микрокоманды для выполняемой операции необходимо осуществлять обращение к медленно действующему (по сравнению с другими элементами, входящими в состав устройства) запоминаюсцему устройству, большое количество оборудования для формирования адреса микрокоманд и большой объем памяти. Цель изобретения - повьпаение быстродействия устррйству при одновременном упрощении устройства за счет сокращения оборудования формирователя адреса микрокоманд и запоминающего устройства. Поставленная цель достигается тем что в микропрограмгиное устройство уп равления, содержащее блок памяти мик рокоманд, дешифратор адреса операций формирователь адреса операций, К групп элементов И К - количество фаз и условных переходов в операции ) дешифратор адреса микрокоманд, комму татор, счетчик фаз, генератор тактовых импульсов и узел пуска-останова, причем адресн.1й вход блока микрокоманд соединен через дешифратор адреса операций с выходом формир вателя адреса операций, информационный вход которого подключен к адресн му входу устройства, выходы элементо Н к групп подключены к информационному выходу устройств -, первгде входы элементов И К групп подключены соответственно к выходам дешифратора адреса микрокоманд, выход генератора тактовых импульсов соединен с первым входом узла пуска-останова, второй вход которого соединен с первым управляющим входом устройства, а выход со счетным входом счетчика фаз, дополнительно содержит регргстр микрокоманд операций, информационный вход которого соединен с выходом блока па мяти микрокоманд, управляющий вход с управляющим входом формирователя адреса операций, с входом сброса счетчика фаз и с первым управляющим входом устройства, а выходы регистра микрокомандд операций - с втopы щ входами элементов И К групп соответственно, управля101щ-1й вход коммутатора соединен с третьим входом узла пуска-останова и с входом условий, второй управляющий вход устройства соединен с четвертым входом узла пуска-останова, вход кода переадреса ции устройства соединен с первым информационным входом коммутатора, вто рой информационный вход которого соединен с вьлходом счетчика фаз, а выход коммутатора соединен с входом дешифратора адреса микрокоманд. На чертеже представлена функциональная схема предлагаемого устройУстройство включает блок 1 памяти микрокоманд, дешифратор 2 адреса опе раций, формирователь 3 адреса операций , адресные входы 4 устройства , К групп элементов И 5, информационны входы 6 устройства, де11гафратор 7 адреса микрокоманд, коммутатор 8, счет чик Э фаз, генератор 10 тактовых импульсов, вход 11 условий устройства, первый управляющий вход 12 устройств второй управляю1ций вход 13 устройства, узел 14 пуска-ocTaF-ioBa, содержащий элемент ИЛИ-НЕ 15, элемент И 16, триггер 17, регистр 18 микрокоманд операций, вход 19 кода переадрес.ации. Микропрограммное устройство управления работает следующим образом. По сигналу Начало операции, подаваемому из внешнего устройства управления (или из арифметического устройства на один из входов 12, счетчик 9 фаз устанавливается в нулевое исходное состояние, в формирователе. 3 формируется адрес операции путем прибавления единицы к содержимому счетчика или за счет записи адреса со входов 4, связанных с внешним устройством управления. По адресу операции из блока 1 выбирается слово со всеми микрокомандаг-ад, необходимыми для выполнения данной установленной операции, которое переписывается в регистр 18 микрокоманд операций, причем длина слова со всеми микрокомандами, выбираемого из запоминающего устройства, равна длине слова каждой из микрокоманд, необходимой для вь полнения данной операции. Это обеспечивается.тем, что для выполнения каждой из фаз операции ( формирование команды, формирование адреса операнда, выполнение операции, размещение результатов необходимы вполне определенные управляющие сигналы, а управляющие сигналы других фаз при этом не используются, и поэтому в предлагаемом устройстве управления сигналы сгруппированы по фазам, подключение которых осуществляется соответствующими группами элементов И5. При этом управляющие сигналы, необходимые для выполнения только первой фазы операции, поступают через группу элементов И 5 на выходы 6 микропрограммного устройства управления, а через остальные группы элементов И5 управляющие сигналы не прохо- дят, так как они при этом отключаются дешифратором 7 адреса микрокоманд. При снятии сигнала Начало операции со входа 12 срабатывает триггер 17, который подключает элемент П 16. При этом импульсы с выхода генератора 10 поступают на счетный вход счетчика 9 фаз, формируя в нем код 1,2..., который через когф утатор В подается на входы дешифратора 7. Последний обеспечивает прохождение управляющих сигналов с выхода регистра 18 микрокоманд операций (т.е. обращения к блоку 1J, необходимых для выполнения второй (третьей) фазы операции, через соответствующие группы элементов И 5 (5) на выходы б микропрограммного устройства управления. При наличии многократного повторения управляющих сигналов для той или иной фазы из внешнего устройства (например арифметического устройства) поступает

сигнал Многократный на вход 13, при этом на времч его сутествования отключается элементн 16.При необходимости изменения порядка выбора фаз из внешнего устройства управления поступает сигнал Условие на входИ, который отключает на время его существования элемент И 16 и подключает входы коммутатора 8 к входам 19 микропрограм-,, много устройства управления, на которые поступает код переадресации, например, из внешнего устройства управления. После снятия сигналов Многократный или Условие цикл работы повторяется и счетчик 9 фаз обеспечивает переключение групп элементов И 5. После выполнения последней фазы операции на вход 12 приходит сигнал Конец операции, воздействующий на триггер 17, который отключает элемент И 16. С приходом следующего сигнала Начало операции цикл работы повторяется.

Технический эффект от использования предлагаемого устройства заключается в повышении быстродействия работы микропрограммного устройства управления за счет исключения необходимости обращения к медленно действующему зaпoминaю ae 1y устройству при формировании микрокоманд для всех (кроме первой ) фаз операций, что достигнуто за счет введения регистра микрокоманд операций, в котором хранятся все микрокоманда (точнее сигналы для всех фаз) выполняемой операции, время считывания из которого значительно меньше временк считывания из запоминающего устройства, а также в упрощении устройства за счет исключения из запоминающего устройства зоны адресов переходов, а из формирователя адреса микрокоманд К регистров адреса перехода с дешифратором переходов, что достигнуто благодаря введению регистра микрокоманд операций и наличию связей коммутатора со входами счетчика фаз и с внешним устройством формирования переходов, позволяющее изменять порядок ,выбора фаз.

Формула изобретения Микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор адреса операций, формирователь адреса операций, К групп элементов И ( К - количество фаз и условных переходов в операции, дешифратор адреса микрокоманд, коммутатор, счетчик фаз, генератор тактовых импульсов и узел пуска-останова, причем адресный вход блока памяти микрокоманд соединен через дешифратор адреса операций с выходом формирователя адреса операций, информационный. вход которого подк почен к адреснрму входу устройства, выходы элементов И К групп подключены к информационному выходу устройства, первые входы

элементов И К групп подключены соответственно к выходам дешифратора адреса микрокоманд, выход генератора тактовых импульсов соединен с первым входом узла пуска-останова, второй

вход которого соединен с первым управляющим входом устройства, а выходсо счетным входом счетчика фаз-, отличающееся тем, что, с целью повышения быстродействия и

упрощения устройства, оно содержит регистр микрокоманд операций, информационный вход которого соединен с выходом блока памяти микрокоманд, управляющий вход - с управляющим входом формирователя адреса операций, с входом сброса счетчика фаз и с первым управляющим входом устройства, а выходы регистра микрокоманд операций с вторыми входами элементов И К групп соответственно, управляющий вход коммутатора соединен с трет-ьим входом узла пуска-останова и с входом условий устройства, второй управляющий вход устройства соединен с четвертым входом узла пуска-остлнова, вход кода переадресации устройства соединен с первым информационныг.1 входом коммутатора, второй информационный вход которого соединен с выходом счетчика фаз, а выход коммутатора соединен с

входом дешифратора адреса т шкрокоманд.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 742937, кл. G 06 F 9/22, 1978,

2. Авторское свидетельство СССР № 760100, кл. G 06 F 9/22, 1978 (прототип).

/

Зона, микрокоманд

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

| Микропрограммное устройство управления | 1978 |

|

SU742937A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1976 |

|

SU638962A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для отладки программ | 1988 |

|

SU1661771A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Микропрограммное устройство управления | 1981 |

|

SU995091A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

Авторы

Даты

1983-01-07—Публикация

1981-06-11—Подача