54 МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1976 |

|

SU638962A1 |

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1978 |

|

SU742937A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964641A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

Изобретение относится к области вычислйтельно.й техники. , Известно микропрограммное устройство управления, содержащее блок памяти, счетчики и дешифраторы Ij. Недостатком известного устройства является его сложность. Наиболее близким по текнической сущ ности к изобретению является микропрог раммное устройство управления, содержашее микропрограммный запоминающий блок, входы зоны адреса переходов которЬго соединены через дешифратор операци регистр команд и запоминающий блок команд с выкодами счетчика команд, вход которого является входом устройства, адресные входы зоны микрокоманд микропрограммного запоминающего блока че рез дешифратор адреса микрокоманд, формирователь адреса микрокоманд и татор соединены с выходами регистра адреса переходов, информационные , цы. микропрограммного запоминающего блока соединены с соответствующими jaxo- йами ре гистра микрокоманд, узла пуска- . останова и регистра адреса перекодов и входу сброс формирователя адреса микрокоманд, управляющие входы коммутатора через дешифратор переходов соединены с выходами счетчика переходов, содержащее также группу элементов И, дополнительный элемент И и элемент НЕ, причем выходы регистра микрокоманд соединены с соответствующими входами узла пуска-останова, регистра команд, счетчика команд, первыми входами элементов И группы, первым входом дополнительного элемента И, второй вход которого через элемент НЕ соединен с входом признаков устройства и со вторыми входами элементов И группы, выходы которых, а также выход дополнительного элемента И и выходы микропрограммного запоминающего блока соединены с соответствующими входами счетчика переходов, второй выход узла пуска-останова соединен с соответствующими входами регистра микрокоманд 2.

374651

В известном устройстве при неисправной работе отдельных устройств, входящих в микропрограммное устройство управления, на выходе его формируются микрокоманды с неправильной информацией, это нарушает работу как микропрограммного устройства управления, так и устройства,. в состав которого оно входит, что снижает надежность его работы.

Целью Изобретения является повыше- 10 ние надежности работы.

Поставленная цель достигается тем, что предложенное устройство содержит перЕьую, вторую,, третью, и четвертую группы элементоё И, первый, второй и третий V 15 элементы ИЛИ, элемент И-НЕ, регистр защиты программы, регистр защиты фазы,ре гистр защиты операций.Информадионные входы регистра зашиты программы являются входами защиты устройстЕ а, а выходы сое- 20 динены с первыми входами элементов И первой группы, вторые входы которйк соэцинены с выходами формирователя адреса операций. Выходы элементов И первой группы соединены с адресными25

входами зоны адреса микропрограмм микропрограммного за-поминающего блока и со входами первого элемента ИЛИ. Входы регистра защиты фазы соединены с выходами коммутатора формирователя, 30 адреса фазы операции, а выходы - с первыми входами элементов И второй групПЬ1, вторые входы которых: сбедйнёны с выходами формирователя адреса микрокоманд. Выходы элементов И второй35 группы соединены с первыми адресными входами аоны мйк:рокоманд микропрограймного запоминающего блока и со входами второго элемента ИЛИ. Вход регистра защиты операции соединен с соответст- 40 вующим выходом зоны адресов микропрограммного запоминающего блока, а выходы - с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами Дещифратора фаз формирова- 45 теля адреса фазы операции. Выходы элементов И третьей группы соединены со вторыми адресными входами зоны микрокоманд микропрограммного запоминающего бло.ка и со входами третьего элемента . 50 ИЛИ. Выходы первого, второго и третьего элементов ИЛИ соединень со входами элемента И-НЕ, выход которого является выходом прерывания устройства. Первые входы элементов И четвертой груп- 55 пы соединены с выходом .первого эле.мента ИЛИ, вторые - с выходом второго элемента ИЛИ, третьи - с выкрцами

.. --

siJSwj,-..;.,v,...,.

64

соответствующих элементов И третьей группы, четвертые -со вторым управляющим выходом узла пуска.ч)станова, Выходы элементов И четвертой группы соединены с управляющик и входами соответствующих разрядов регистра микрокоманд

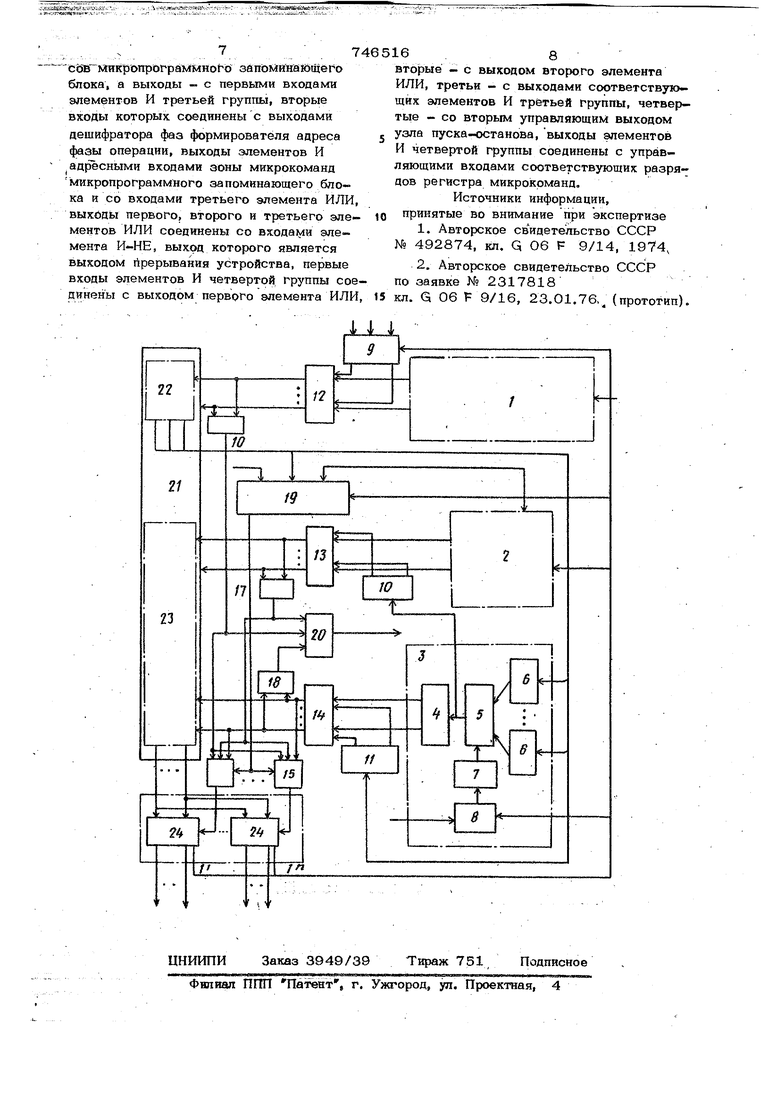

На чертеже представлена структурная схема устройства.

Оно содержит формирователь адреса операций 1, формирователь адреса микрокоманд 2, формирователь адреса фазы операции 3, дещифратор фаз 4, коммутатор 5, регистры адреса фазы , дешифратор переходов 7., счетчик фаз 8, регистра защиты программы 9, регистр защиты фазы 10, регистр защиты операции 11, первую 12, вторую 13, третью 14 и четвертую 15 группы элементов И, первый 16, второй 17 и третий 18 элементы ИЛИ, узел пуска-останова 19, элемент И-НЕ 20, Микропрограммный запоминающий блок 21 с зоной адресов микрокоманд 22 и зоной микрокоманд 23 и регистр микрокоманд 24,

МикропроГ|эаммное устройство управления работает следующим образом.

Перед началом работы в регистр защиты программы 9 из внешнего ЗУ записывается информация о разрешенных операциях в выполняемой программе. Затем в формирователе адреса операции 1 формируется адрес операции, и если он разрешен, то по нему из зоны адреса микрокоманд 22 выбирается соответствующее слово, содержащее все начальные адреса микропрограмм, используемых в данной операции, ряд признаков, и содержащее информацию о разрешенных микропрограммах и микрокомандах в данной выполняемой операции. Информация с начальными адресами микропрограмм и с разрешенными микрокомандами, для каждой из фаз выполняемой операции переписывается с первых выходов зоны адреса микрокоманд 22 в соответствующие регистры адреса фазы 6. -6р. Информация с разрешенными адресами микропрограмм для выполняемой операции со вторых выходов зоны адресов микрокоманд 22 переписывается в регистр 11. Признаки, поступающие с третьих выходов зоны микрокоманд 22, обеспечивают установку в исходное состояние счетчиков и регистров, используемых в микропрограммном устройстве управления. Затем подключается узел пуска-останова 19. При этом из разре- шенной микропрограммы зоны микрокоманд 23, выбранной формирователем ядре . . 57 са фазы операции 3 с помощью формиров теля адреса микрокоманд 2, последовательно выбираются все разрешенные микрокоманды, используемые в данной фазе, которые переписйваются в соответствующий разряд регистра микрокоманд 24. Е последней микрокоманде выполняемой фазы операции формируются сигналы на выходах 1-1 одного из регистров 24 обеспечивающие установку формирователя адреса микрокоманд 2 в исходное состояние, а в счетчике 8 формируется код, обеспечивающий подключение следующего по порядку регистра 6 к выходу коммутатора 5. При этом в регистр защиты фазы 10 записывается информация с разрешенными микрокомандами для следующей фазы, а на выходе группы элементов И 1.4 формируется начальный адрес следующей, второй микропрограммы для выполняемой операции. После поступления следующего импульса с выхода узла пуска-останова 19 цикл работы повторяется. В последней микрокоманде последней фазы выполняемой операции формируютс я сигналы на выходах регистра 2.4 , обес. печивающие формирование адреса следующей по порядку операции в блоке 1, после чего цикл работы в заданной программе повторяется. Таким образом, введение в устройство дополнительных блоков и связей повышает надежность работы устройства за счет уменьшения объема памяти зоны микрокоманд ЗУ путем сокращения длины слов, записанных в эту зону, за счет разделения регистра микрокоманд на п -регистров фаз; Искажения информации на выходе устройства исключены за счет ложных сигналов; сформированных в нерабочих регист- pax фазы, путем отключения (п-1) регист ров фаз; Искажения информации на выходе уст- ройства, возникающие из-за неправильно сформированных адресов на выходах формирователей адреса операции, фазы операции и микрокоманды исключены за счет исключения неразрешенных адресов, осуществляемого с помощью регистров защиты программ, операции, фазы операции и групп элементов И. Формула изобретения, 1, Микропрограммное устройство управления, содержащее формирователь адjaeca операции, микропрограммный запо166минающий блок с зонами микрокоманд, и адресов микропорограмм, формирователь адре са фазы операции, включающий дешифратор фаз, подключенный через коммутатор к выходам регистров адреса фазы, при этом управляющие 6ХОДЫ коммутатора связаны через дешифратор переходов с выходами счетчика фаз, формирователь адреса микрокоманд, узел пуска-останова и регистр микрокоме нд, соответствующие информационные выкоды зоны адресов микропрограмм микропрограммного запоминающего блока подключены к управляющему входу формирователя адреса микрокоманд, к информационным входам регистров адреса фазы формирователя адреса фазы операции, первый управляющий выход узла пускаостанова соединен со вторым уп эавляю- щим входом формирователя адреса микрокоманд, информационные входы регистра микрокоманд соединены с выходами зоны микрокоманд микропрограммного запоминающего блока, а выходы - с информационными входами счетчика фаз формирователя адреса фазы операции, узла пуска-останова, формирователя адреса микрокоманд и являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности, оно содержит первую, вторую, третью и четвертую группы эле;ментов И первый, второй, третий элементы ИЛИ, элемент И-liE, регистр защиты программы, регистр защиты фазы, ре- гистр защиты операции, информационные входы регистра защиты программы $ю- ляются входами защиты устройства, а выходы соединены с первыми входами элементов И первой группы, вторые входы которых соединены с выходами формирователя адреса операций, выходы элементов И первой группы соединены с адресными входами зоны адреса микропрограмм мик- ропрограммного запоминающего блока и со входами первого элемента ИЛИ, входы регистра защиты фазы соединены с выходами коммутатора формирователя адреса фазы операции; а выходы - с первыми входами элементов И второй группы, вторые входы которых соединены с выходами формирователя адреса микрокоманд, выходы элементов И второй группы соединены с первыми адресными входами зоны микрокоманд микропрограммного запоминающего блока и со входами второго элемента ИЛИ, вход регистра защиты операции соединен с соответствующим выходом зоны адре-

СШГМикропрЬграмнногЬ запоминающего блока, а выходы - с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами дешифратора фаз формирователя адреса фазы операции, выходы элементов И .адресными входами зоны микрокоманд микропрограммного запоминающего блока и со входами третьего элемента ИЛИ, выхйды первого, второго и третьего элементов ИЛИ соединены со входами элемента И-НЕ, выход которого является выходом йрерывания устройства, первые входы элементов И четвертой группы соеПйнены с выходом первого элемента ИЛИ,

8

вто1рые - с выходом второго элемента ИЛИ, третьи - с выходами соответствующих элементов И третьей группы, четвертые - со вторым управляющим выходом

узла пуска-останова, выходы элементов И четвертой группы соединены с управляющими входами соответствующих разрядов регистра микрокоманд.

Источники информации,

принятые во внимание при экспертизе

2,Авторское свидетельство СССР по заявке № 2317818

кл. G 06 F 9/16, 23.01.76, (прототип).

Авторы

Даты

1980-07-05—Публикация

1977-08-18—Подача