t

Изобретение относится к импульсно технике.

Известен импульсный преобразователь I содержащий входные триггеры, на информационные входы которых подается сигнал, закодированный с удвоенной плотностью, а на тактируемые входы, - первак и вторая . последовательности синхроимпульсов, взаимно смещенные по фазе; выходы триггеров соединены со входами вентилей И/ выходы которых инвертируются и объединяются вентилем НЕИЛИ для получения одной импульсной последовательности.

Этот преобразователь не позволяет суммировать импульсные последовательности.

Наиболее близким по технической сущности к заявленному является импульсний преобразователь, содержащий два входных триггера, один вход каждого из которых соединён с соотве ствующей входной шиной, вторые входы соединены между собой и подключены к шине синхросигнала, а выход казэдого входного триггера соединен с одним входом соответствующего формирующего триггера и одним из входов фазового различителя, третий и ч твертый входы различителя соединены с выходами формирующих триггеров, вторые входы которых соединены со второй шиной синхросигнала 2.

Преобразователь не обеспечивает достаточной достоверности преобразования.

Цель изобретения - увеличение достоверности преобразования информации.

0

Поставленная цель достигается тем, что в импульсный преобразйватель, содержащий два входных триггера, один вход каждого из которых.соединен с соответствующей входной шиной, вторые

5 вхоЙы соединены между собой и. подключены к шине синхросигнала, а выход каждого входного триггера соединен с одним из входов соответствующего формирующего триггера и одним

0 из входов фазового различителя, третий и четвертый входы которого соединены и выходами формирующих триггеров, вторые входы которых соединены сО второй шиной синхросигнала, введены

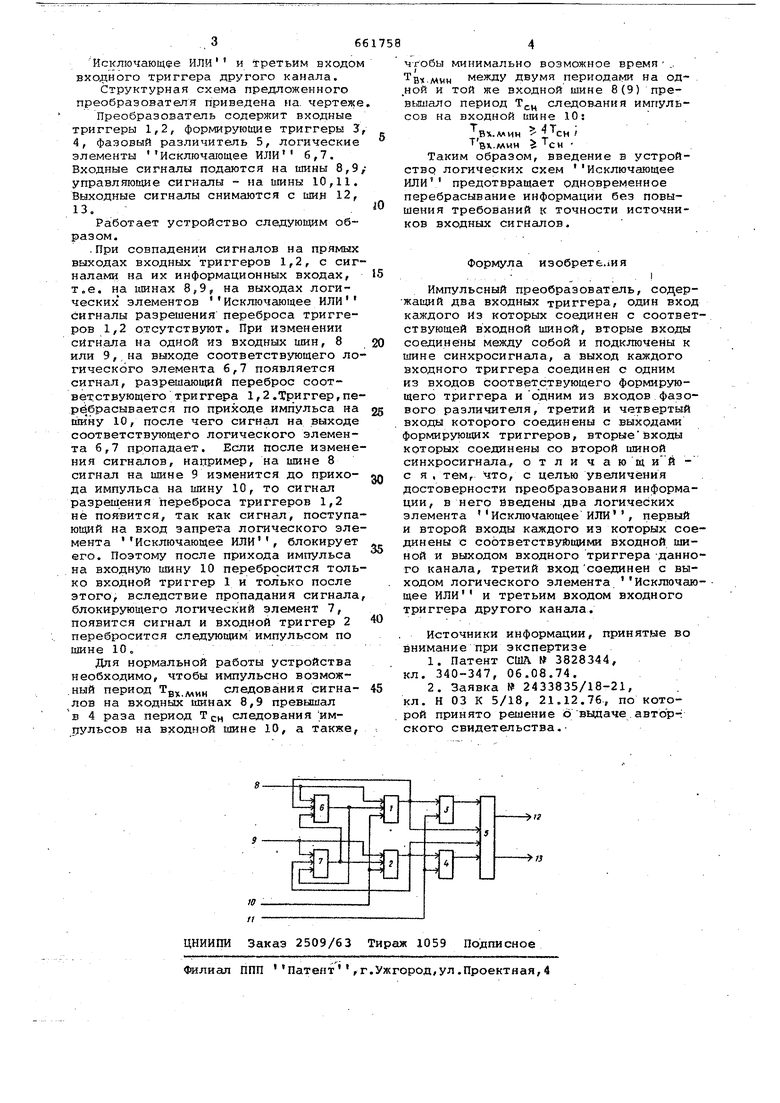

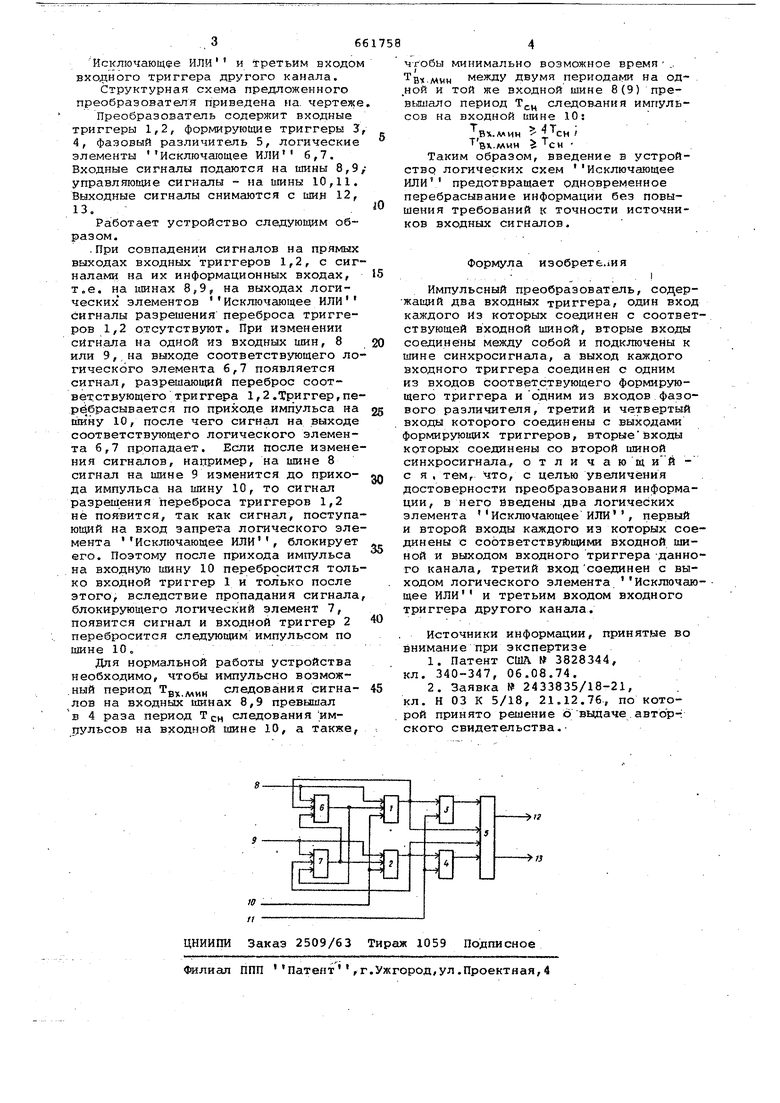

5 дв.а логи еских- элемента Исключающее ИЛИ . Первый и второй входы каж,цого элемента соединены с соответствующими ;входной шиной и выходом входного триггера данного канала, третий вход сое0динен с выходом логического элемента Исключающее ИЛИ и третьим входом вхо дного триггера другого канала. Структурная схема предложенного преобразователя приведена на. чертеже Преобразователь содержит входные триггеры 1,2, формируюйше триггеры 3 4, фазовый различитель 5, логические элементы Исключающее ИЛИ 6,7. Входные сигналы подаются на шины 8,9 управляющие сигналы - на айны 10,11. Выходные сигналы снимаются с шин 12, 13. Работает устройство следующим образом. .При совпадении сигналов на прямых выходах входных триггеров 1,2, с сигналами на их информационных входах, т.е. пинах 8,9, на выходах логических элементов Исключающее ИЛИ сигналы разрешения переброса триггеров 1,2 отсутствуют При изменении сигнала на одной из входных шин, 8 или 9, на выходе соответствующего логического элемента 6,7 появляется сигнал, разрешбиощий переброс соответствующего триггера 1,2.Триггер,перебрасывается по приходе импульса на шину 10, после чего сигнал на выходе соответствующего логического элемента 6,7 пропадает. Если после изменения сигналов, например, на шине 8 сигнал на шине 9 изменится до прихода импульса на шину 10, то сигнал разрешения переброса триггеров 1,2 не появится, так как сигнал, поступающий на вход запрета логического эле мента Исключающее ИЛИ , блокирует его. Поэтому после прихода импульса на входную шину 10 перебросится только входной триггер 1 и только после этого, вследствие пропадания сигнала блокирующего логический элемент 7, появится сигнал и входной триггер 2 перебросится следующим импульсом по шине 10, Для нормальной работы устройства необходимо, чтобы импульсно возмож.ннй период Tg следования сигналов на входных ишнах 8,9 превышал в 4 раза период следования имрульсов на входной шине 10, а также, чтобы минимально возможное время ,. TB.MHH между двумя периодами на и той же входной шине 8(9) превьлиало период следования импульсов на входной шине 10: Т 4 т Bii.MMH Z.сн сн Таким образом, введение в устройство логических схем Исключающее ИЛИ предотвращает одновременное перебрасывание информации без повышения требований к точности источников входных сигналов. Формула изобрете.шя , .1 Импульсный преобразователь, содержащий два входных триггера, один вход каждого из которых соединен с соответствующей входной ишной, вторые входы соединены между собой и подключены к шине синхросигнала, а выход каждого входного триггера соединен с одним из входов соответствующего формирующего триггера исадним из входов фазового различнтеля, третий и четвертый входы которого соединены с выходами форлшрующих триггеров, вторыевходы которых соединены со второй шиной синхросигнала., о т л и ч а ю и иИ с я «тем, что, с целью увеличения достоверности преобразования информации, в него Введены два логических элемента Исключающее ИЛИ , первый и второй входы каждого из которых соединены с соответствующими входной шиной и выходом входного триггера -данного канала, третий входсоединен с выИсключаю- ходом логического элемента щее ИЛИ и третьим входом входного триггера другого канала. Источники информации, принятые во внимание при экспертизе 1.Патент США 3828344, кл. 340-347, 06.08.74. 2.Заявка № 2433835/18-21, кл. Н 03 К 5/18, 21Л2.76, по которой принято решение о вьщаче . автор-: ского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазоимпульсный преобразователь | 1976 |

|

SU684710A1 |

| Устройство для индикации | 1976 |

|

SU624250A1 |

| Устройство для считывания информации с перфожетона | 1980 |

|

SU935984A1 |

| Устройство для контроля работы машин | 1985 |

|

SU1297090A1 |

| Частотно-фазовый детектор | 1980 |

|

SU1040591A1 |

| Частотно-фазовый дискриминатор | 1977 |

|

SU699666A1 |

| Фазовый дискриминатор | 1977 |

|

SU632073A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Весовое устройство для определения количества предметов равной массы | 1978 |

|

SU765663A2 |

| Измерительное устройство для измерителя группового времени запаздывания | 1989 |

|

SU1620986A1 |

Авторы

Даты

1979-05-05—Публикация

1977-04-26—Подача