; 54 ) ЧАСТОТНО-ФАЗОВЫЙ, ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ фазовой автоподстройки частоты управляемого генератора и устройство для его осуществления | 1989 |

|

SU1788576A1 |

| Фазовый дискриминатор | 1977 |

|

SU632073A1 |

| Цифровой частотно-фазовый дискриминатор | 1986 |

|

SU1390774A2 |

| СТАБИЛИЗИРОВАННЫЙ ЭЛЕКТРОПРИВОД | 2016 |

|

RU2621288C1 |

| Цифровой частотно-фазовый дискриминатор | 1991 |

|

SU1826122A1 |

| Частотно-фазовый дискриминатор | 1990 |

|

SU1830180A3 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| Синтезатор частот | 1980 |

|

SU886251A1 |

| ЭЛЕКТРОПРИВОД С ЧАСТОТНО-ФАЗОВЫМ РЕГУЛЯТОРОМ | 1973 |

|

SU379031A1 |

| Частотно-фазовый детектор | 1980 |

|

SU921043A1 |

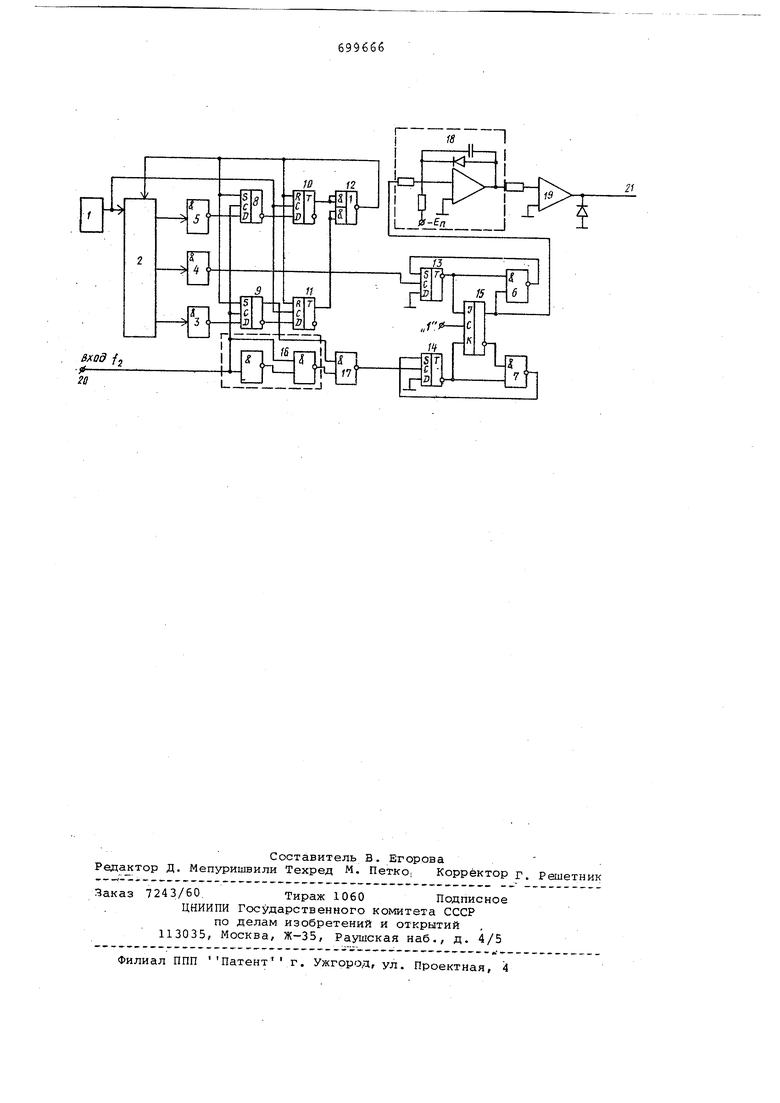

Изобретение относится к импульсно технике. Известен частотно-фазовый дискриминатор, содержащий генератор эталон ной частоты, различающий узел из дву триггеров, на вход одного из которых подключен эталонный генератор, а на вход второго - источник ведомой (измеряемой) частоты (от генератора, электропривода и т.п.), формирующий узел из двух триггеров и cyм /Iaтopa и логические элементы связи между форм рующим и различающим узлами, обеспечи вающие логическое взаимодействие элементов при работе 1. Недостатком дискриминатора является наличие фазовой ошибки при дискри минации. Наиболее близким по технической сущности к заявленному является дискр минатор, содержащий генератор эталонной частоты , выход которого подключен к первому входу делителя частоты второй вход которого,соединен с выходом логического элемента ИЛИ, а выходы делителя частоты соединены со входами трех логических элементов И, выходы первого и третьего из которых соединены с D-входами двух триггеров, S-входы которых соединены между собой и подключены к выходу логического. элемента ИЛИ, а С-входы соединены со входной шиной, и фазовый различитель, состоящий из двух различающих триггеров, выход каждого из которых соединен с первы;- входом одного из двух логических элементов И и одним входом формирующего DK-триггера, выходы которого соединены со вторыми вхсдами упомянутых двух логических элементов И, выходы которых подключены ко вторым входам соответствующих триггеров фазового раз.личителя 2 . Недостатком данного дискриминатора является значительная длительность переходного процесса при изменении режима. Цель изобретения - уменьшение длительности переходных процессов при изменении режима. Поставленная цель достигается тем, что в дискриминатор, содержащий генератор эталонной частоты, выход которого подключен к первому входу делителя частоты, второй вход которого соединен с выходом логического элемента ИЛИ, а выходы делителя частоты сое,инены со входами трех логических элементов И, выходы первого и третьего из которых соединены с D-входами двух триггеров, S-входы которых соединены между собой и подключены к выхсяу логического элемента ИЛИ, а С-входы сое динены со входной шиной, и фазовый раэличитель, состоящий из двух различакяцих триггеров, выход каждого из которых .соединен с первым входом одного из двух логических элементов И и одним входом формирующего .ЗК-тригг гера, выходы которого хзоединены со вторыми входами упомянутых двух ЛОГИческих элементов И, выходы которых подключены ко вторым входам соответствующих триггеров фазового различителя, введены два D-триггера/ элемент задержки, логический элемент ЗАПРЕТ и последовательно соединенные интегра тор и формирующий усилитель, вход корорых соединен с одним из выходов фор мирующего триггера фазового различителя, вход одного из различающих триг геров подключен к вьоходу второго из упомянутых логических элементов И, вход второго различающего триггера со динен с выходом логического элемента ЗАПРЕТ, один вход которого через эле мент задержки соединен со входной ши ной, а второй вход подключен к инверс ному выходу одного из триггеров,, прямые выходы каждого из триггеров подключены к D-входам D-триггеров, R-BX ды которых объединены и соединены с выходом логического элемента ИЛИ, при чем С-входн D- триггеров соединены с выходом.генератора эталонной частоты .а их выходы - со входами логического элемента ИЛИ. Структурная электрическая схема описываемого дискриминатора приведена на чертеже. Дискриминатор содержит генератор эталонной частоты 1, делитель частоты 2, логические элементы И 3,...,7, D-триггеры 8,..., 11, логический эле мент ИЛИ 12, различающие О-триггеры 13, 14, формирующий ик-триггер 15, элемент задержки 16, логический элемент ЗАПРЕТ 17, интегрирующий усилитель 18, формирующий усилитель 19. Входной сигнал подается на входную щину 20. Выходной сигнал снимается с выхода 21. Работу схемы можно прояснить следующим образом. Импульсыэталонной частоты f частотой в Р раз больше за данной частоты синхронизации посту пают на делитель частоты 2, вследстви чего на логических элементах 3,...,5 появляются прямоугольные сигналы час тотой . Сигнал частотой лог ческого элемента И 4 поступает на вх различающего триггера 13 в качестве эталонного сигнала, а сигнал измеряемой частоты поступает второ го различающего триггера 14 черер элемент задержки 16 и логический.эле мент ЗАПРЕТА 17. Рассмотрим работу в режимах сравнения частот и фазовом режиме. Первый частотный режим. Предположим, что период ве;аомой частоты больше эталонной. Вследствие этого сразу после включения или спустя некоторое незначительное время импульсы совпадут на выходе логического элемента И 3. Этот момент (t.) ется триггером 9. Триггер 9, переключаясь, подготавливает переключение D-триггера 11 и одновременно через логический элемент ЗАПРЕТ 17 блокирует поступление импульсов ведомой частоты на вход различающего триггера 14. Вслацствие этого на вход различающего триггера 13 поступают подрдд два импульса эталонной частоты. При этом устройство переводится в первый частотный режим (режим фазной фиксации) и на прямом выходе формирующего триггера 15-появляется сигнал логической . После этого происходит перестройка счет.чика по логической цепи обратной связи. При приходе ближайшего очередного импульса эталонной частоты происходит срабатывание триггера 9. Его выходной сигнал через логический элемент ИЛИ 12 воздействует на установочные входы триггеров 9 и 11 и сбрасывает их в исходное состояние. Одновременно делитель частоты 2 этим сигналом задерживается в состоянии ifi + 1. Это означает его перестройку на такое количество импульсов частоты f, которое необходимо для того, чтобы прошедший блокированный импульс измеряемой частоты как бы совпадал с состоянием m (m 3) делителя частоты 2. После этого и до момента, пока фазорассогласование сравниваемых импульсов не превысит 21Г/р, импульсы поочередно поступают на соответствующие входы ра.зличающих триггеров 13 и 14, выходное состояние которых при этом не меняется. Фазовый режим Переход из первого частотного режима- в фазовый режим происходит при увеличении измеряемой частоты причем для перехода в фазовый ражим необходимо/ чтобы на вход различающего триггера 14 поступили подряд два импульса измеряемойЧастоты fg- Этот момент (tj.) наступает при фазораосогг ласовании сравниваемых импульсов, равном 211 /р. При этом импульс измеряемой частоты f совпадает с импульсом на выходе логического элемента И 5, что фиксируется переключением триггера 8. Триггер 8 подготавливает переключение D-трнггера 10, которое происходит при приходе ближайшего Очередного импульса эталонной частоты, В момент переключения делитель частоты 2 через логический элемент ИЛИ 12 переключается в состояние m 1, минуя состояние т. Вследствие этого на вход различающего триггера 13 поступления очередного импульса эталонной частоты не про изойдет, а на вход различающего триг гера 14 поступят два импульса подряд переведя устройство в режим сравнени фаз. В этом режиме скважность выхсян го напряжения пропорциональна фазорассогласованию сравниваемых импульоных сигналов и не превышает 1/р,Дан ные импульсы поступают на интегратор 18, где преобразуются в треугольные. Импульсы треугольной формы преобразуются формирователем 19 в импульс прямоугольной формы, являющееся выходным сигналом. Второй частотный режим f У . Переход во второй частотный режим происходит при дальнейшем увеличений измеряемой частоты fj. Этот момент (tj) наступает при фазорассогласовании сравниваемых импульсов, равном 2Vp. При этом происходят переключения, аналогичные описанным. При пере ходе из первого частотного режима в фазовый переключаются триггеры 8, 10 происходит перевод делителя частоты 2 в состояние m + 1, минуя состояние т, вследствие этого блокируется поступление очередного эталонного имПул са и на вход различающего триггера 1 поступают подряд два импульса, переводя устройство во второй частотный режим, характеризующийся нулевым напряжением на выходе формирующего триггера 15 и, следовательно, на вы:ходе 21. Переход из второго частотного режима в фазовый происходит при .уменьшении частоты 2. При этом наступает момент, когда фазорассогласование импульсов достигнет 2ft/p и импульс Kf меряемой частоты fg совпадает с вы.ходным напряжением логического элемента И 3. Произойдут переключения, аналогичные описанным при работе в первом частотном режиме; посредством логического элемента 15 блокируется поступление очередного импульса измеряемой частоты и на вхсд различающего триггера 13 поступят подКд два импульса эталонной частоты, и этом дискриминатор переведется f:- фазовый режим. Одновременно произой дет сброс делителя частоты 2 в состояние т+1. Переход из фазового режима впервый частотнвт произойдет при дальнейшем уменьшении частоты f ilpH фазорассогласовании сравниваелих импульсов, равном , произойдет совпадение импульса f j с выходным им пульсом логического элемента И 3 и далее произойдут вышеописанные переключения. Формула изобретения Частотно-фазовый дискриминатор, содержащий генератор эталонной частоты, выход которого подключенК первому входу.делителя частоты, второй вход которого соединен с выходом логического элемента ИЛИ, а выхсды делителя частоты соединены со входами трех логических элементов И, выходы первого и третьего из которых соединены с D-входами двух триггеров, S-входы которых соединены между собой и псдключены к выходу логического элемента ИЛИ, а С-входы соединены с входной шиной, и фазовый различитель, состоящий из двух различающих триггеров, выход каждого из которых соединен с первым входом одного из двух логических элементов И и одним входом формирующего ЗК-триггера, выходы которого соединены со вторыми вxoдaмIi упомянутых двух логических элементов И, выходы которых подключены ко вторыч входам соответствующих триггеров фазового различителя, отличаю Д и и с я тем, что, с целью уменьшения длительности переходных процессов при измерении режима работы, в него введены два D-триггера, элемент задержки, логический элемент ЗАПРЕТ и последов ательно соединенные интегратор и формирующий усилитель, вход которых соединен с одним из выходов формиру1ощего триггера фазового различителя, вход одного из различающих триггеров подключ ён- к выходу второго из упомянутых логических элементов И, вход вторбго различающего триггера соединен с выходом логи,ческого элемента ЗАПРЕТ, один вход которого через элемент задержки соединен со входной шинсй, а второй вхси подключен к инверсному, выходу одного из триггеров, прямые выходы каждого из триггеров подключены к D-входам D-триггеров, R-ЕХОДЫ которых объединены и соединены с выходом логического элемента ИЛИ, причем С-входы D-триггеров соединены с в.кходом генератора эталонной частоты, а их выходы - со входами логического элемента ИЛИ . Источники информации, принятые во внимание при экспеотизе 1.Авторское свидетельство СССР 379049, кл. н 03 К9/06, 30.10.7о. 2.Патент США № 3857103, .кл. 328-133, 24.12.72,

20

21

Авторы

Даты

1979-11-25—Публикация

1977-01-27—Подача