(54) ИНВЕРТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| Инвертор | 1976 |

|

SU615604A1 |

| Умножитель частоты следования импульсов | 1984 |

|

SU1210215A1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

| Адресный формирователь | 1990 |

|

SU1734122A1 |

| Логическое устройство | 1977 |

|

SU738171A1 |

| Устройство для аспирации биологической жидкости | 1990 |

|

SU1725910A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Счетный триггер | 1980 |

|

SU924835A1 |

1

Изобретение относится к импульсной технике, предназначено для использования во входных схемах оперативных запоминающих устройств.

Известен инвертор, содержащий транзисторы прямого и инверсного выходов, токозадающий транзистор и ряд диодов. При этом базы выходных транзисторов объединены через диод и через резисторы соединены, с положительным полюсом источника питания, объединенные эмиттеры подключены к коллектору токозадающего транзистора эмиттер которого через резистор соединен с щиной нулевого потенциала. Катод входного диода подключен ко входу инвертора, а к базе транзистора инверсного выхода 1.

Недостатки этого устройства - высокое значение . минимального выходного -напряжения «нуля и несимметричность прямого и инверсного выходов по минимальному выходному напряжению «нуля.

Наиболее близок к предлагаемому токовый инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, а база подключена через резистор к положительному полюсу источника

питания, транзисторы прямого и инверсного выхода, эмиттеры которых соединены, базы объединены через диод, катод которого через резистор подключен к положительному полюсу источника питания, а анод соединен с коллектором входного транзистора.

При этом к катоду упомянутого диода подсоединен также коллектор дополнительного транзистора; база которого объединена с эмиттерами выходных транзисторов и через резистор соединена с щиной нулевого потенциала, к которой также подключен эмиттер дополнительного транзистора 2.

У этого устройства ограниченные функциональные возможности при построении логических блоков из/за больщих уровней выходных напряжений.

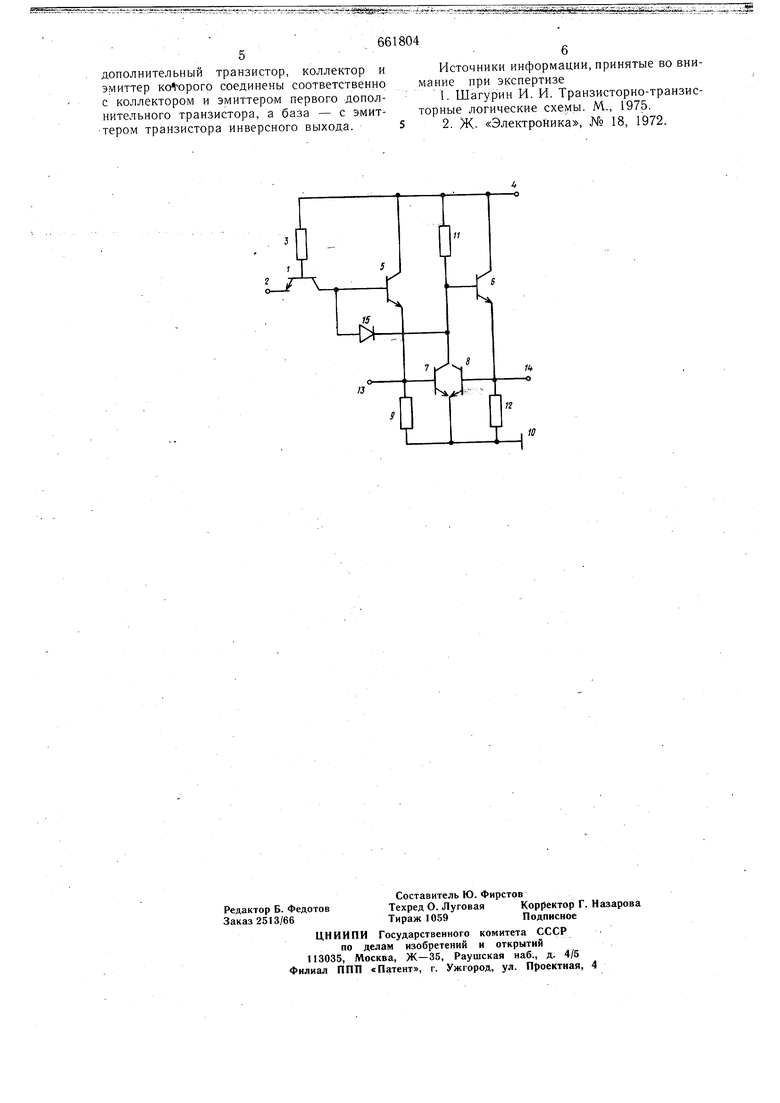

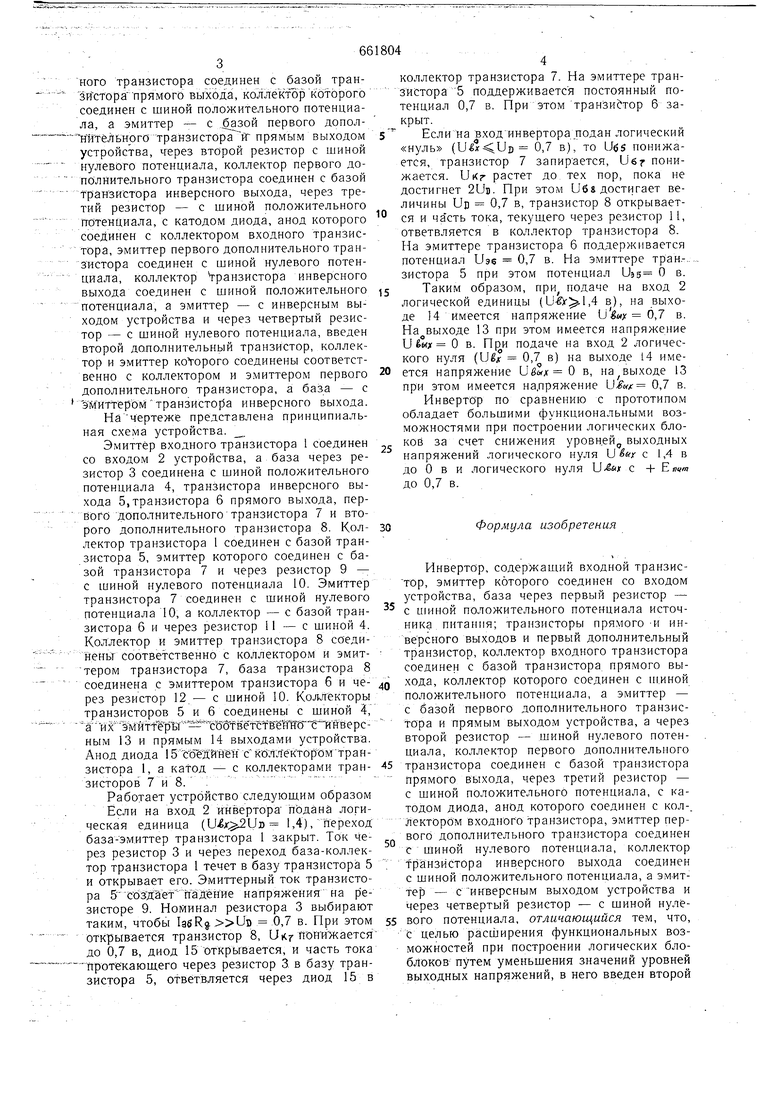

С целью расщирения функциональных возможностей при построении логических блоков путем уменьшения уровней выходных напряжений, в инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, база - через первый резистор с щиной положительного потенциала источника питания, транзисторы и инверсного выхода, первый и второй дополнительные транзисторы, коллектор входного транзистора соединен с базой транзистора прямого выхода, коллекторкоторого соединен с шиной положительного потенциала, а эмиттер - с . первого допол нитеЛьнрго транзистора йг прямым выходом устройства, через второй резистор с шиной нулевого потенциала, коллектор первого дополнительного транзистора соединен с базой транзистора инверсного выхода, через третий резистор - с шиной положительного п;атенциала, с катодом диода, анод которого соединен с коллектором входного транзистора, эмиттер первого дополнительного транзистора соединен с шиной нулевого потенциала, коллектор Уранзистора инверсного выхода соединен с шиной положительного потенциала, а эмиттер - с инверсным выходом устройства и через четвертый резистор - с шиной нулевого потенциала, введен второй до-полнительный транзистор, коллектор и эмиттер которого соединены соответственно с коллектором и эмиттером первого дополнительного транзистора, а база - с эмиттеромтранзистора инверсного выхода. На чертеже представлена принципиальная схема устройства. Эмиттер входного транзистора 1 соединен со входом 2 устройства, а база через резистор 3 соединена с шиной положительного потенциала 4, транзистора инверсного выхода 5, транзистора 6 прямого выхода, первого дополнительного транзистора 7 и второго дополнительного транзистора 8. Коллектор транзистора 1 соединен с базой транзистора 5, эмиттер которого соединен с базой транзистора 7 и через резистор 9 - с шиной нулевого потенциала 10. Эмиттер транзистора 7 соединен с шиной нулевого потенциала 10, а коллектор - с базой транзистора 6 и через резистор 11 - с шиной 4. Коллектор и эмиттер транзистора В соединены соответственно с коллектором и эмиттером транзистора 7, база транзистора 8 соединена с эмиттером транзистора 6 и через резистор 12 - с шиной 10. КолЛекторь транзисторов 5 и 6 соединены с шиной 4, а иГэмиТ1 |рШ 1ЙШ8ётств т Г ным 13 и прямым 14 выходами устройства. Анод диода 1 БсШдЙнён с коллекторбмтранзистора 1, а катод - с коллекторами транзисторов 7 и 8. -,Работает устройство следующим образом Если на вход 2 инвертора подана логическая единица ( 1,4), переход база-эм.иттер транзистора 1 закрыт. Ток Через резистор 3 и через переход база-коллектор транзистора 1 течет в базу транзистора 5 и открывает его. Эмиттерный ток транзистора 5 сЪздаетпадение напряжения на резисторе 9. Номинал резистора 3 выбирают таким, чтобы lasRj UD .0,7 в. При этом открывается транзистор 8, Укг поНИжается до 0,7 в, диод 15 открывается, и часть тока Ттротекающего через резистор 3 в базу транзистора 5, оФветвляется через диод 15 в коллектор транзистора 7. На эмиттере транзистора 5 поддерживается постоянный потенциал 0,7 в. При этом транзистор 6 закрыт. Если на вход инвертора подан логический «нуль (,UD 0,7 в), то понижается, транзистор 7 запирается. Us понижается, и Кг растет до тех пор, пока не достигнет 2UB. При этом U6s достигает величины Uj) 0,7 в, транзистор 8 открывается и часть тока, текущего через резистор 11, ответвляется в коллектор транзистора 8. На эмиттере транзистора 6 поддерживается потенциал Уэе 0,7 в. На эмиттере тран.-,. зистора 5 при этом потенциал Uag О в. Таким образом, при подаче на вход 2 логической единицы (,4 в), на выходе 14 имеется напряжение uW 0,7 в, На выходе 13 при этом имеется напряжение и fewx О в. При подаче на вход 2 логического нуля (U&f 0,7 в) на выходе 14 имеется напряжение в, на выходе 13 при этом имеется напряжение 0,7 в. Инвертор по сравнению с прототипом обладает большими функциональными возможностями при построении логических блоков за счет снижения уровней выходных напряжений логического нуля D с 1,4 в до О в и логического нуля USn/i с + до 0,7 в. Формула изобретения Инвертор, содержащий входной транзистор, эмиттер которого соединен со входом устройства, база через первый резистор - с тиной положительного потенциала источника питания; транзисторы прямого -и инверсного выходов и первый дополнительный транзистор, коллектор входного транзистора соединен с базой транзистора прямого выхода, коллектор которого соединен с ижной положительного потенциала, а эмиттер - с базой первого дополнительного транзистора и прямым выходом устройства, а через второй резистор - шиной нулевого потенциала, коллектор первого дополнительного транзистора соединен с базой транзистора прямого выхода, через третий резистор - с шиной положительного потенциала, с катодом диода, анод которого соединен с кол-. Лектором входного транзистора, эмиттер первого дополнительного транзистора соединен с шиной нулевого потенциала, коллектор транзистора инверсного выхода соединен с шиной положительного потенциала, а эм-иттер - синверсным выходом устройства и через четвертый резистор - с шиной нулевого потенциала, отличающийся тем, что, с целью расширения функциональных возможностей при построении логических блоблоков путем уменьшения значений уровней выходных напряжений, в него введен второй

дополнительный транзистор, коллектор и эмиттер которого соединены соответственно с коллектором и эмиттером первого дополнительного транзистора, а база - с эмиттером транзистора инверсного выхода.

661804

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-05-05—Публикация

1976-07-20—Подача