1

Изобретение относится к импульсной технике и предназначено для -согласования импульсных устройств, работающих с различными по амплитуде логическими уровнями, в частное- 5 ти для согласования по уровню сигналов на входе и выходе ТТЛ и МДП устройств.

Известен преобразователь логических уровней, содержащий входной 10 эмиттерный повторитель, дифференциальный каскад сдвига логических уровней, квазикомплементарный выходной каскад, источник опорного напря;кения, входную и выходную ши- 5

ну 1 .

Недостатком преобразователя является сложность построения и отсутствие защиты от коротких замыканий.20

Известен также преобразватель логических уровней, содержащий управляющий транзистор первого типа проводимости и преобразующий транзистор второго типа проводимости, де- 25 литель напряжения на двух резисторах, входной и нагрузочный резисторы, входную и выходную шину, шину питания и общую шину, первый и второй защитные диоды, при этом база управч ЗО

ляющего, транзистора подключена к катоду первого защитного диода, анод которого соединен с анодом второго защитного диода и через входной резистор - с входной шиной. Эмиттер управляющего транзистора подключен к общей линии, а коллектор соединен с первым выводом второго резистора делителя, второй вывод которого связан с-базой преобразующего транзистора и через первый резистор делителя - с шиной питания и с эмиттером преобразующего транзистора, коллектор преобразующего транзистора подключен к выходной шине,к катоду рторого защитного диода и через нагрузочный резистор - к шине нулевого потенциала 12 .

Недостатками известного устройства является низкое быстродействие и большая потребляемая мощность.

Цель изобретения - повышение быстродействия и снижение потребляемой мощности.

Указанная цель достигается тем, что в преобразователь логических уровней, содержащий преобразующий транзистор р-п-р типа, эмиттер которого соединен с шиной питания, коллектор - с выходом, устройства.

катодом диода и через резистор - с общей шиной, а база через соответствующие резисторы - с шиной питания и коллектором управляющего транзистора п-р-п типа, эмиттер которог подключен к общей шине, введены вхоной, переключающий и разрядный транзисторы п-р-п типа, причем эмитер входного транзистора соединен ч; входом устройства, база - с аНодо диода и через резистор - с шиной питания, а коллектор - с базами управляющего и переключающего транзисторов, коллектор последнего соединен через резистор с выходом устройства и непосредственно с базой разрядного транзистора, коллектор которого подключен к выходу устройства, а эмиттеры переключающего и разрядного транзистора соединены с общей шиной.

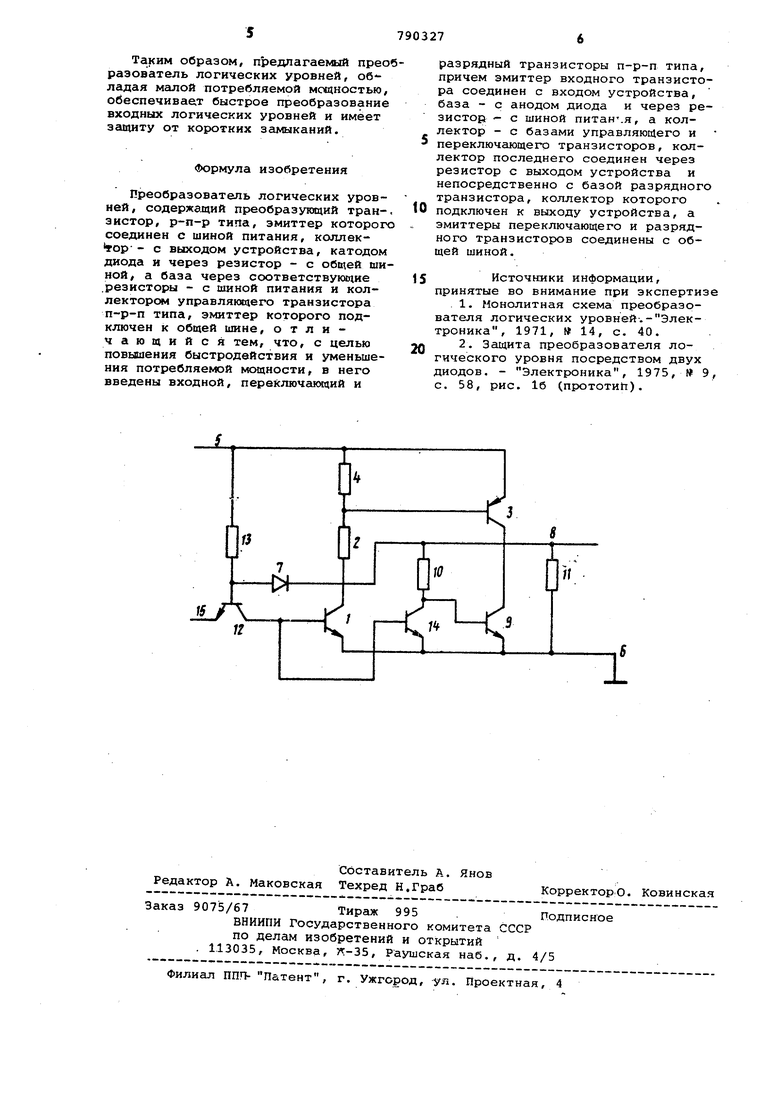

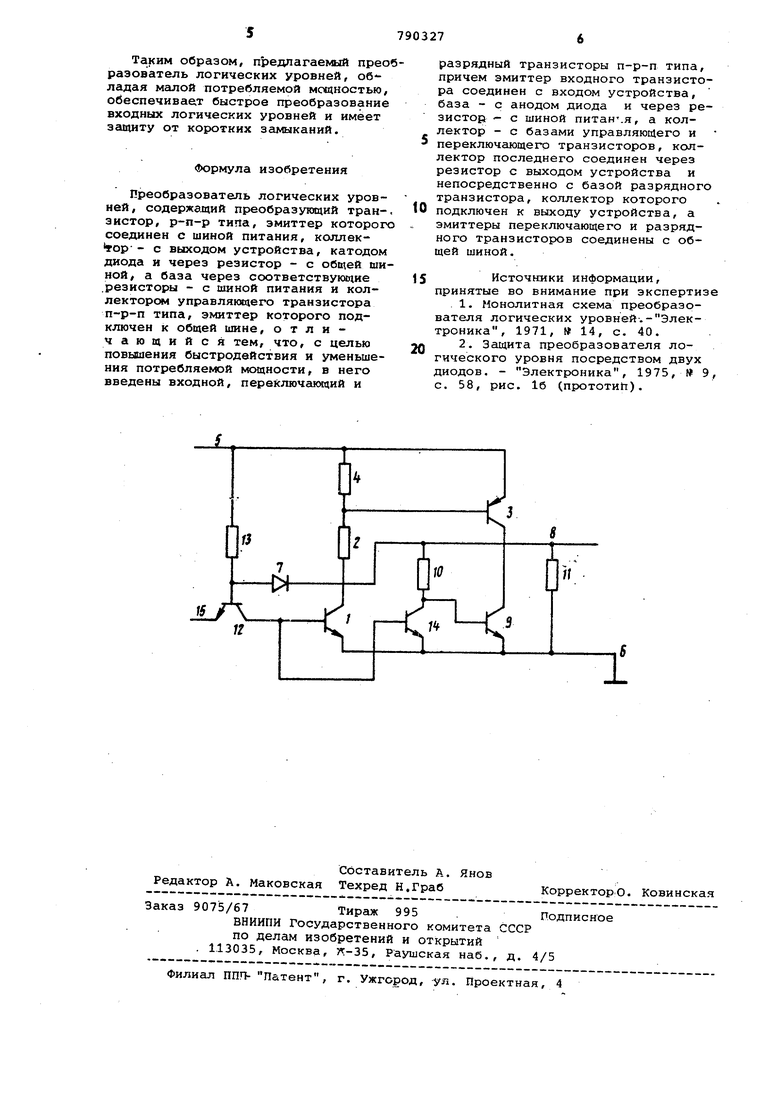

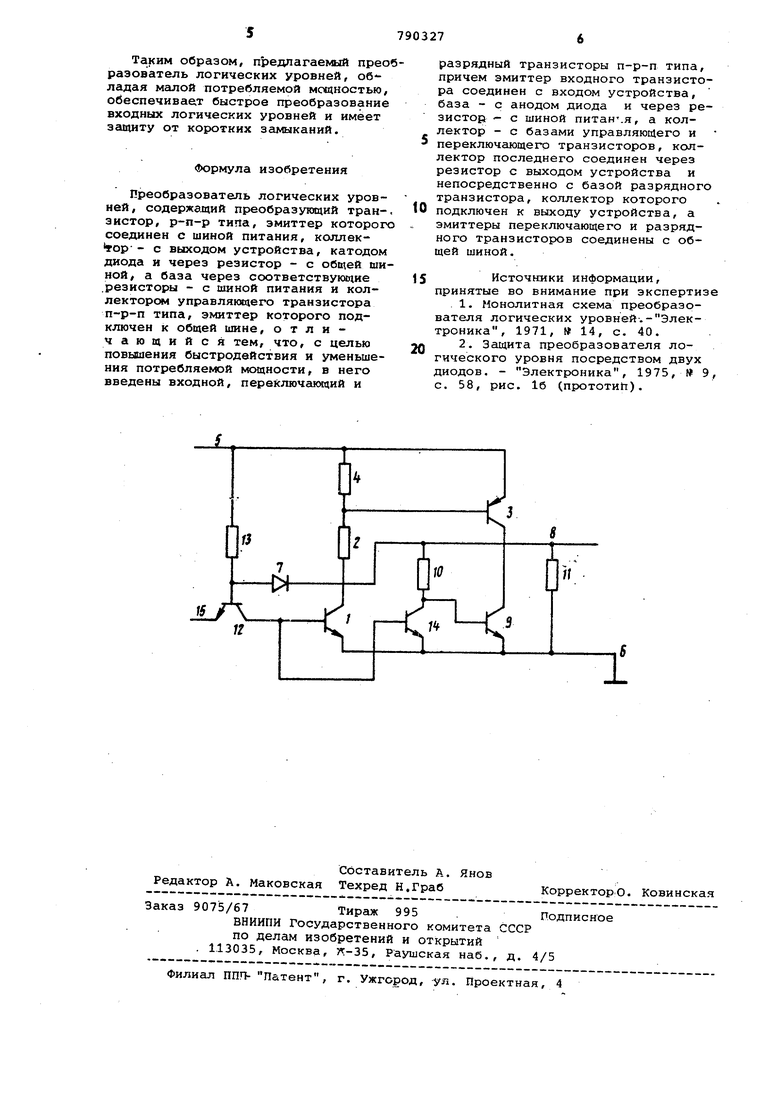

Па чертеже представлена принципиальная схема преобразователя логических уровней.

Коллектор управляющего транзистора 1 п-р-п типа подключен к первому выводу первого резистора 2 делителя, второй вывод которого соединён с базой преобразующего транзистора р-п-р типа 3 и через второй резистор делителя 4 - с эмиттером преобразукнцего транзистора 3 и с шиной 5 питания. Эмиттер управляющего транзистора 1 подключен к шине б нулевого потенциала Коллектор преобразующего транзистора 3 связан с катодом диода 7, с выходной шиной 8, с коллектором разрядного транзистора 9 п-р-п типа, с первым выводом дополнительного резистора 10 и через нагрузочный резистор 11 - с шиной 6 нулевого потенциала.

. База входного транзистора 12 типа подключена к аноду диода 7,и через входной резистор 13 - к шине 5 питания. Коллектор входного транзистора 12 соединен с базой управляющего транзистора 1 и с- базой переключающего транзистора 14 р-п-р типа. Эмиттер входного транзистора 12 подключен к входной шине 15. Второй вывод дополнительного резистора 10 соединен с коллектором переключающего транзистора Д 4 и с базой разрядного транзистора 9. Эмиттеры переключаквдего 14 и азрядного 9 транзисторов подключе ы.. к шине 6 нулевого потенциала.

Преобразователь логических уров-ней работает следующим образом.

Когда на входную шину 15 подается равный 2,3-ЗВ уровень логической 1, подлежащий преобразованию в высокий уровень напряжения. Ток через входной резистор 13 и цепь база-коллектор входного транзистора 12 (инверсное включение входного транзистора 12 ) втекает в базы управляющего транзистора 1 и переключающего транзистора 14. Управляющий 1 и переключающий 14 транзисторы открываются. Открытый переключакячий транзистор 14 шунтирует цепь базае эмиттер разрядного транзистора 9, и транзистор 9 закрывается. По коллекторной цепи открытого управляющего транзистора 1 через первый резистор делителя 2 и параллельно

Q .включенные второй резистор делителя Ц и переход эмиттер-база преобразующего транзистора 3 протекает ток. Преобразующий транзистор 3 открывается, и на входной шине 8 формируется высокий уровень напряжения,

5 .близкий по величине к питающему напряжению, подаваемому на шину 5 питания. Величины нагрузочного резистора 11 и дополнительного резистора 10 выбираются такими, чтобы

0 суммарный ток через них не превышал -0,1-0,2 мА. При сформированном высоком выходном уровне напряжения разрядный транзистор 9 закрыт и не шунтирует выходную шину

5 8.

Если на входную шину 15 поступает уровень логического О, ток через входной резистор 13 протеQ кает по цепи база-эмиттер входного транзистора 12 через открытый входной транзистор 12 проходит рассасывающий ток из базы управляющего транзистора 1 и переключаю- щего транзистора 14, транзисторы 1 и 14 быстро закрываются, в результате закрывается и преобразующий транзистор 3.

Начинается процесс формирования низкого выходного уровня напряже0 НИН. Разрядный транзистор 9 открывается и разряжает выходную шину 8. Как только на выходной линии 8 установится .низкий уровень напряжения, разрядный транзистор 9 закрывается, при этом переключаютлй транзистор 14 также закрыт, и потребление мощности преобразовате. лем от источника питания отсутствует, за исключением цепи: входQ ной резистор 13, база-эмиттер входного транзистора 12.

Преобразователь логических уровней имеет защиту от коротких замыканий выходной шины 8 с обп;ей шиной 6. При коротком замыкании выходной

5 шины 8 с общей шиной 6 включается диод 7. Напряжение на его аноде равно примерно 0,7 В, что недостаточно для открывания управляющего транзистора, и переключающего транзистора 14. Транзисторы 1 и 14 закрываются, что приводит к закрыванию преобразующего транзистора 3. После устранения причины, вызвавшей короткое замыкание, устройство возвращается в прежнее состояние.

Таким образом, предлагаемый преобразователь логических уровней, обладая малой потребляемой мощностью, обеспечивает быстрое преобразование входных логических уровней и имеет зёцциту от коротких замыканий.

Формула изобретения

Преобразователь логических уровней, содержэлций преобразующий тракзистор, р-п-р типа, эмиттер которог соединен с шиной питания, коллекbfop-- с выходом устройства, катодом диода и через резистор - с общей шиной, а база через соответствукндие .резисторы - с шиной питания и коллектором управляющего транзистора п-р-п типа, эмиттер которого подключен к общей шине, отличающийся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, в него введены входной, переключающий и

разрядный транзисторы п-р-п типа, причем эмиттер входного транзистора соединен с входом устройства, база - с анодом диода и через резистор - с шиной питан .я, а коллектор - с базами управляющего и переключающего транзисторов, коллектор последнего соединен через резистор с выходом устройства и непосредственно с базой разрядного транзистора, коллектор которого

0 подключен к выходу устройства, а эмиттеры переключающего и разрядного транзисторов соединены с общей шиной,

Источники информации,

принятые во внимание при экспертизе

. 1, Монолитная схема преобразователя логических уровней.- Электроника, 1971, 14, с. 40.

2. Защита преобразователя логического уровня посредством двух иодов. - Электроника, 1975, 9, с. 58, рис. 1б (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Усилитель считывания | 1983 |

|

SU1132364A1 |

| Формирователь импульсов | 1975 |

|

SU656192A1 |

| Усилитель считывания | 1983 |

|

SU1104581A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

Авторы

Даты

1980-12-23—Публикация

1978-10-09—Подача