;дом шифратора, выходы (п+5) старших разрядов 1-го блока формирования частичного результата подключены ко входам регистра частичного результата {i+i)-ro блока и ко входам шифратора 1-го блока, первый и второй выходы которого соединены соответственно со вХодаМй установки в единичное и нулевое состояние первого триггера (1+1)-го блока и третьего триггера 1-го блока, а третий и четвертый выходы шифратора 1-го блока соединены со входами установки в единичное и нулевое состояние второго триггера (1+1)-го блока и четвертого триггера 1-го блока, соответственно, единичный выход второго управляющего триггера соединен с (п+5)-м входом блока формирования частичного результата, а. единичный выход первого управляющего.. триггёра. соединенс первым входом .. -. второго элемента И, второй и третий BJtosa kOToporo срединенй .соответст.вен с единичным выходом четвёртого триггера (1+1У-го ШйёЙйм .выхоДом чётвертого. триггера 1-г6 блока, -единичныйвыход, первого управЛяющетСО. -трЙггёрабоедИнен со входом третьего элемента .И, второй .и третий йхОды котброгбсоединены соответйтвенно .с : едй Ийчным. выводом третьего триггера .(1+1) -гр -блока и нулевым выхддом т ретьего триггера i-rO блока, выход второго элемента И соединен со вхрДйми установкивединичное и нулевое сос.тояние, .сро вётсттвенно, тре.т ьегр ... триггера (i+l)-го блокаи ч еТвер ого . трЙггера {1+1)-го блока, и с первым. . .входом первого Элемента И, к другому входу кОттЗрОг.о подключен единичный вЫХОД третьеготрнгггера, а .также с пёрвьпу вхЪдой че.тйё15т6г6 элементаИ, второй вход которого подключен к нуяёв6му;выходу трётьёгр триггера/ а ..вйходтретьего элейента И йОёдинен установки в е 1Иййчн-оё;;11 нулевое состояние сббтвётствёНйо чётвертрго тр1иггера (1+1)-го блока и Трётьёготриггера (1+1)-го .блОка и С :первь5м:входом пятогс) элемента И, второй вход которого подключен к единичному вахОду четвертого триггера, а также с: первым Входом шестого элемента И , второй вход которого подключен к нулевому ВьИсодучетвертогр триггера вйходЫ; двухвходовых схем 1Гёрво1 о; Четвертого, пятрго и шестоrjo ..элементов И сОеДиаены соответствен ИОЬо входом установки в нулевое соетОяние первого триггера (1+1)-го блока и третьего триггера 1-го блока с6 входом установкив единичное соетбяние второго триггера (1+1)-го блока и четвертого триггера 1-го блока, сойхрдрм установки в нулевое состоЯННе второго триггера (1+1)-го блока и четвертого триггера 1-го блока и со йХОдом устайовки в единичное состоя нйё первого триггера (1+1)-го блока И третьего триггера i-ro блока, выходы второго управляющего триггера 1-го блока соединены со входами второго управляющего триггера (14-1)-го блока. На чертеже изображена функциональная схема i-ro и (i-fl)-ro блоков предлагаемого устройства. Каждый 1-й блок устройства состоит из первого управляющего триггера li, первого триггера 21, второ.го триггера 31, третьего триггера 41, четвертого триггера 51, регистра частичного результата 61, регистра сомножителя 71, второго управляющего триггера 81, блока формирования частичного результата 91, элементов И 101,111,121, шифратора 131, элементов И 141,151, 161. .... :... Устройство работает следующим . . -. ; . . . . Первый операнд последовательности , представленный дополнительным модифиЦиррванным двоичным кодом, имеющим три знаковые разряда, принимается на регистр. 6 i, нарегистр 71 и триггер .1. с помощью устройст ва управления О V , а на триггер записывается ; код 8, .также с помощью устройства управ ,, ления, записывается код . Во втором такте содержимое регистра 6 передается через блок 91 в регистр б. со .с.двигой на Один разряд влево регистра 7| --в регистр 1, сЬдёржиМое триггеров 11 и 8| соотвётственно - в триггеры 1 и Si + j.Ha регистры и 7,, а также на триггеры 1 и 8{. с помощью устройства управлени.я записывается код О результат.е-;передачи информации с первого блока на второй произойдут следующие преобразований: к содержимому регистра 6J прибавится, или вычтется . из него при помощи блока ( содержийое регистра 7, причем выполненная операция междусодержимым регистров 64 и 7| будет зависеть от управляющих входов блока 9i, связанных с триггерами 4 i и 5; , кроме того, содержимое .триггеров 4J и 5) может быть таким, что содержимое регистра 7 вообще не передастся на схему 9|. Одновременно с ЭТИМ в зависимости от управляющих входов схемы 91, связанных с триггерами 2{ и 2, произойдет аналогичная операция между с одержимым триггера 8,причем код ,записанный в триггере 8;, может вычесть;ся или сложиться с содержимым (п+4)го разряда регистра 6i;схемой 13, в соответствии с табл.1, вьвделится старшая цифра -очередного частичного результата, предст авляющая собой цифру избйТочногОквазиканонического кода с цифрагли {Т,0,1, и запишется, в соответствии с табл.1, в 2 и 3,

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Конвейерное устройство для выполне-Ния АРифМЕТичЕСКиХ ОпЕРАций НАдМНОжЕСТВОМ чиСЕл | 1979 |

|

SU849205A1 |

| Арифметическое устройство | 1976 |

|

SU656059A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения двух N-разрядных чисел | 1981 |

|

SU991418A2 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

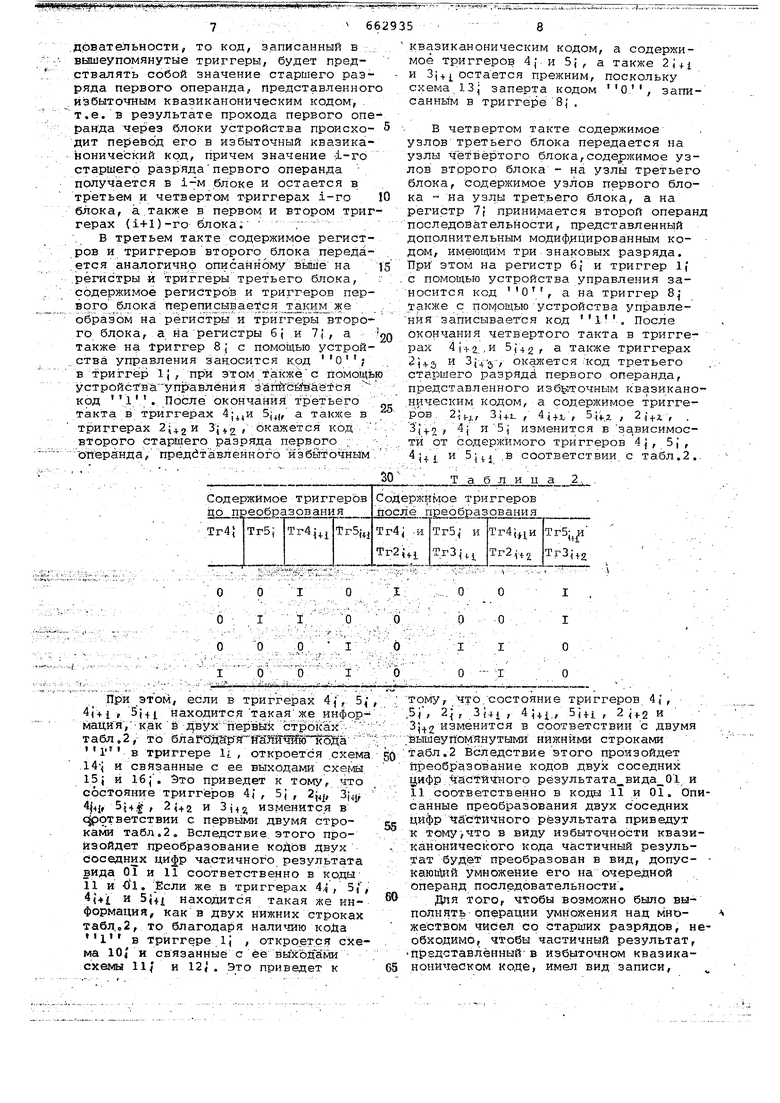

Сложение содержимого регистра 6 с содержимым регистра 7i произойдет, если в триггерах 4j и Sj записан кой I; вычитание - если в триггерах 4; и 5; записан код , содержимое регистра 7; не будет передано на сх-ему , если в триггерах 4, к 5j записан код О. Сложение содержимого триггера 8i с содержикым (п+4)-го разряда регистра 6 произойдет в том случае, если в триггерах 2| и 3| записан коя -Г; вычитание - если в триггерах 2j и 3f зарые возможные комбинации пяти старших разрядов схемы 9/, которые будут свидетельствовать о переполнении разрядной сетки; с целью упрсядения описания заявляемого устройства, эти ситуаций не раЬсматрйваются.

содержимое триггеписан код

ра 8j не будет передано на схему 9f,

55 если в триггерах 2, и 3 записан

О

Таким образом, после оконкод

чания второго такта в третьем и четвертом триггерах первого блока, а также в первом и втором триггерах второго блока окажется код старшей цифры первого частичного результата (код знака первого частичного результата), представленный в избыточном квазиканоническом коде. (Поскольку мы приняли еще только один операнд после.довательности, то код, записанный в ; вышеупомянутые триггеры, будет предствалять собой значение старшего разряда первого операнда, представленног избыточным квазиканоническим кодом, т.е.в результате прохода первого опе ранда через блоки устройства происходит перевод его в избыточный квазикавонический код, причем значение l-ro старшего разрядапервого операнда -. получается в 1-м блоке и остается в третьем и четвертом триггерах 1-го блока, а, также в первом и втором триг герах (i+l)-ro блока; В третьем такте содержимое регистров и триггеров второго блока передается аналоги.чйр описанному вьшё на регистры -и триггеры третьего блока, содержимое регистров и триггеров первого блока переписывается образом на регистры и триггеры второго блока, а нарегистры 6 ,и 7|, а также на триггер 8 j с помощью устройства управления заносится код в триггер 1J , при Этом Такжёс помощь устройства управлёния ЗапйсййаётЬя крд ,.,, .После окончаний третьего Такта в триггерах 4|,и , а также в триггерах 2(2 код второго старшего разряда первого .;. ОПеранда, представленного избыточным При этом, если в триггерах 4j,. 4J4.i, Sifi находитсятакаяже информации,-как S j;Byx riepBUk строка: - табл,2/ то блаШаагй ШлЙчШ кЩа Г в триггере ;. , откроется схема . 14-J и связанные с ее выходами ск&ш. 15; и 16 j. Это приведет к тог, что I 4, , 5; , 2|,|, 3 состояние триггеров 4; , 5J , 2, jj4ij 5{4f , 2 i.2 и JH 3iio изменится в фрответствии с первьами двумй строKaivM табл.2. Вследствие этого произойдет преобразование коДов двух соседних частичного результата вида и 11 соответственно в коды 11 и -О. Если же в триггерах 4 , 5(, 4,+ и 5i4i находится такая же информация, как в двух нижних строках Габл.е2, то благодаря наличию код а в триггере 1J , откроется схема lOj и связанные с ее вьахогГами схемы 11| и 12 . Это приведет к квазиканоническим кодом, а содержимое триггеров 4{. и 5| , а также 2,4i и 3i + j остается прежним, поскольку схема, 13 заперта кодом 0. , записаннь1м в триггере8| , В четвертом такте содержимое узлов третьего блока передается на узлы ч ётвёртого блока,содержимое узлов второго блока - на узлы третьего блока, содержимое узлов первого блока - на узлы третьего блока, а на регистр 7) принимается второй операнд последойательйости, представленный дополнительным модиф цированным кодом, имеющим три.знаковых разряда. При этом на регистр б| и триггер If с помощью устройства управления заносится код О, а на триггер 8{ также с помощью устройства управленйя записываемся код , После окончания четвертого такта в триггерах 4i.v2,,H 5.42f э также триггерах 2j.(.5 и 3(4з / окажется :код третьего старшего разряда первого операнда. представленного изб гточным квазиканоническим кодом, а содержимое триггеров. 2i(.j, 3i+L , .. , .J. , .1, , 4 и5 изменится в за висимостй от содержимого триггеров 4j, 5J, i-ti .в соответствии с табл.2.. Т а б л , что.состояние триггеров 4;, 5j, 2, 3;-4 , ., Sjti , 2 f2 и зменится в соответствии с двумя вышеупомянутыми нижними строками табл.2 Вследствие этого произойдет преобразованне кодов двух соседних цифр, .- астйчиого рёзуль. и 11 соответственно в коды 11 и 01. Описанные преобразования двух сЪседних цифр Чйстичного результата приведут к в виду избыточности квазиканонического кода частичный результат будет преобразован в вид, допус- каюЩий умножение его на очередной . операнд последовательности . Для того, чтобы возможно было выполнять- операции умножения над множеством чисел со старших разрядов, необходимо, чтобы частичный результат, Прздставлёиный в избыточном квазиканоничеаком коде, имел вид записи, - 9 при которой как можно ближе влево расположены , если поло жительно, или , если число оТ рицательно, Описанная последовательность и2 трех тактов повторится для каждого m блоков для t операндов. После под чи i-ro операнда (.1+1)-ый операнд п следовательности можно принимать на вход устройства через два такта, пр чем последовательность из трех такт дня i-ro операнда, где i {2,3,4,, ,.,-1,-, будет отличаться от пос ледовательности из трех тактов для первого операнда тем, что этот операнд будет приниматься регистром 7, а в регистр б с помощью устройства управления будет заноситься код О в отличие от парного операнда послед вательности, который принимается на регистр 6J, а в регистр 7j заноситс код О. . Для формирования результата необходимо в регистр б| и в триггеры 8{ с помсадью устройства управления записать код О, а в регистр 1 подать код 000,0000., ,001, В каж дом следующемтакте содержимое регис ра 7д будет передаваться в регистр 7(4 и, в зависимости от содержимого триггеров 4J и 5J ,складываясь или вычитаясь с содержимьдм регистра б/, через (п+5) тактов достигнет выходов регистра сомножителя из конвейерного устройства. При этом на выходах из конвейерного устройства, связанных со схемйй формирования частичного результата, окажутся знаковый и (п+4) старших разряда кода результата, переведенного в результате описанной операций из квазиканоническо избыточного кода в дополнитёльньзй; двоичный код, -. Старшие (п+4) разряда произведени 2 чисел могут.быть получены при rtoMo щи заявляемого устройства через (ЗЕл-п+б) тактов, при этом в ()-м такте можно принимать новую последбвательнрсть; чисел, С помощью предложенного устройства возможно выполнение умножения и суммирования последовательности.чи сел, а также вычисления полинома .. Р (х) а.,/+: +,, . а,х-5- аа и некоторых других операций, причем выполнение операции суммирования чисел будет отличаться от операции умножения чисел тем, что кйждый i-й операнд, где i € 2,3,4,.-, .t-l, необходимо принимать на регистр б, а в регистр 7 с помощью устройства управления записывается код 001.000 ,. ,00 , При этом частичный результат при выполнении операции сложения можно не преобразовывать, а это значит, что после подачи 1-го операйда в следующем такте можно принимать для суммирования (1+1)-й операнд последовательности и, сле510довательно, (п+4) старшие разряда суммы 1 п-разрядных чисел могут бъпь получены за (Е+п+б) тактов,,Вычисление указанного полинома отличается от операции умножения t чисел, при . условии,что тем, что, начи-™ ная со второй последовательнсюти из трех тактов, на регистр бц будет заноситься не код О, а код а/, при этом на регистр 7j будет заноситься код , В следующем такте, псх;ле подачи такта формирования результата, можно принимать новую последовательность чисел. Следовательно., основное преимущество конвейерного Метода обработки информации, заключающееся в эффективном исдользовани.и аппаратуры многорегистровых устройств, в данном .случае сохраняется. Таким образом, предлагаемое устройство, вычисляя одно и то же арифметическое выражение за гораздо меньшее количество тактов, чем устройство, выбранное в качестве прототипа, обладает значительно большей по сравнению с ним производительностью. При этом оно может состоять из гораздо меньшего количества однотипных блоков. Кроме того, вследствие применения в заявляемом уст- ройстве схемы перемножения чисел в дополнительйых кодах отпадает необходимость В том, чтобы все операнды выражения, подлежащего вычислению, были обязательно п оложительными. дробями, что имеет место при вычислении этого выражения при помощи известного устройства. Формула изобретения КонМейёрнбе устройство для одновременного выполнения арифметических операций над множеством п-разрядных чисел, выполненное из однотипных блоKOB J каждый i-й () блок содержит регистр частичного результата, регистр сомножителя,(п+б) входовой блок фор 4ирОвания частичного-результата, первый управляющий триггер, первый элемент И, первый триггер, шину тактовьсс импу тьсов, причем выходы регистра Частичного результата и регистра сомножителя соединены со входами блока формирования частичного результата, входы регистра сомножителя 1-го блока соединены с выходами регистра сомножителя (i-l)-ro блока, а выходы первого управлшощего триггера i-ro блока подключены к соответствующим ходам первого управляющего триггера (i-H)-ro бпока единичный выход перого триггера подключен к управляющеу входу блока формирования частичноо результата, шина тактовых импульов соединена со входами регистра

11 частичного результата, регистра сомножителя, первого триггера управления и первого триггера, отличающ е е с я тем, что, с целью повьшения быстродействия, в каждый i-й блок введены дополнительно второй, третий и четвертый триггеры, шифратор, второй, третий, четвертый, пятый и шестой элементы И, второй управляющий триггер, причем единичные выходы второго, третьего и четвертого триггеров соединены с управляющими вxoдa вl блока формирования частичного результата нулевой выход второго управляющего триггера соединен с управляющим входом шифратсч а, выходы (п+5) старших разрядов i-ro блока формирования частичного результата подключейы ко входам регистра частичного результата . (i-(-l),-ro блока и ко входам шифратора i-ro блока/первый и второй выхода которого соединены соответствуете со входами установки в единичное и нулевой состояние первого триггера (i-fl)-ro блокаг и третьего триггера i-ro блока, а третий и четвертый выходы шифратора i-ro блока соединены со входами установки в единичное и нулевое состояние второго триггера (i+1)-го блока и четвертого триггера i-ro соответственно, единичный )ыход второго управляющего триггера соединен с (п+5)-м входом блока формирования частичного результата, а единичный выход перв1огь управляющего триггера соединен с первьач входом второго элемента И, второй и третий входы которого соединены соответственно с единичным ввскодом четве|р ого триггера (-i+D-rb блЬка.и нёлувым выходом четвертого триггера i-ro бло ка, единичный выход первого управляющего триггера соединен со входом третЬ1ВГд элемента И, второй и третий входы которого соединены соответстве но (J, единичным, выходом третьего триг гера (i+1)-го блока и нулевым выходо третьего триггера i-ro блока, выход

662935

12 второго элемента И соединен со входами установки в единичное и нулевое состояние, соответственно, третьего триггера (i-H}-ro блока и четвертого , триггера (i-H)-ro блока и с первым входом первого элемента И, к другому входу которого подключен единичный выход третьего триггера, а также с первьиу входом четвертого элемента И, второй вход которого подключен к нулевому выходу третьего триггера, а выход третьего элемента И соединен со входами установки в единичное и нулевое состояние, соответственно четвертого триггера (i+1)-го блока и третьего триггера ti+D-ro блока и с первым входом пятого элемента И, второй вход которого подключен к единичнсм-iy выходу четвертого триггера, а также с первым входом шестого элемента И, второй вход которого подключен к нулевому выходу четвертоготриггера; выходы двухвходовых схем первого, четвертого, пятого и шестого элементов И соединены соответственно со входом установки в нулевое состояние первого триггера (i+1)-го блока и третьего триггера i-ro блока, со вхОдЬм установки в единичное состояние второго триггера (i+1)-го блока и четвертого триггера i-ro блока, со входом установки в нулевое состояние второго .триггера (i+1)-го блока и четвертого триггера i-ro блока и Со входом установки в единичное состояние первого триггера (i+l)-ro блока и третьего Г1Жггера i-ro блока, выходы второго управляющего триггера i-ro блока соединены со входами второго упра вляющего триггера (i+1)-го блока. , Источники информации, принятые во внимание при экспертизе 1.Самофалов К.Г. и др. Структуры ЭЦВМ четвертого поколения, М., Техника, с.89.248. 2.йвторское свидетельство СССР 479111, кл G 06 F 7/52, 1974. ,

Авторы

Даты

1979-05-15—Публикация

1976-11-18—Подача