(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством п-разрядных чисел | 1976 |

|

SU662935A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Конвейерное устройство для выполне-Ния АРифМЕТичЕСКиХ ОпЕРАций НАдМНОжЕСТВОМ чиСЕл | 1979 |

|

SU849205A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

Изобретение относится к области вычислительной техники и предназначено для выполнения арифметически.х операций над массивами двоичных чисел по конвейерному принципу.

Известны устройства для выполнения арифметических операций над массивами чисел, работающие по конвейерному принципу 1. С помощью таких устройств возможно перемножение пар чисел, однако перемножение последовательности из t чисел осуществляется в несколько последовательных этапов. Кроме того, недостатком таких устройств является необходимость одновре.менной выборки из памяти двух операндов и синхронной передачи этих операндов на первый уровень.

Наиболее близким аналогом является арифметическое устройство, состоящее из п блоков, каждьш из которых содержит первый и второй регистры, выходы которых соединены с первым и вторым входами узла формирования частичного произведения, два триггера, выходы которых соединены со входами первого элемента И, тактирующие входы регистров и триггеров соединены с тактовой щиной, выходы первого регистра и уза формирования частнчного произведения, первого э.1емснта И и первого триггера соединены соответственно со входами первого регистра, второго регистра, первым дополнительным входом второго регистра и нулевым входом первого регистра последующего блока, единичный вход второго триггера соединен первым лЮполнительным выходом блока формирования частичного произведения, входы регистров первого блока соединены с шинами ввода операндов, а нулевые входы триггеров первого.блока - с соответствующими управляющими тинами 2.

В этом устройстве в каждом цикле умножения анализируется только один разряд множителя, что ограничивает быстродействие устройства.

Целью изобретения является повыщение быстродействия.

Для достижения поставленной цели каждый блок устройства дополнительно содержит узел формирования управляющих сигпалов, второй элемент И, третий и четвертый триггеры, единичный вход третьего триггера соединен со вторым дополнительным выходом узла формирования частичного произведения, тактирующие входы третьего и

четвертого триггеров подключены к тактовой шине, входы узла формирования управляющих сигналов подключены к выходам первого, второго и третьего триггеров, первый выход узла формирования управляющих сигналов подключен к управляющему входу узла формирования частичного произведения, а второй выход - к единичному, входу четвертого триггера последующего блока, входы второго элемента И подключены к выходам первого и третьего триггеров, а выход второго элемента И подключен ко второму дополнительному входу второго регистра последующего блока, нулевые входы третьего и четвертого триггеров первого блока подключены к соответствующим управляющим щинам устройства.

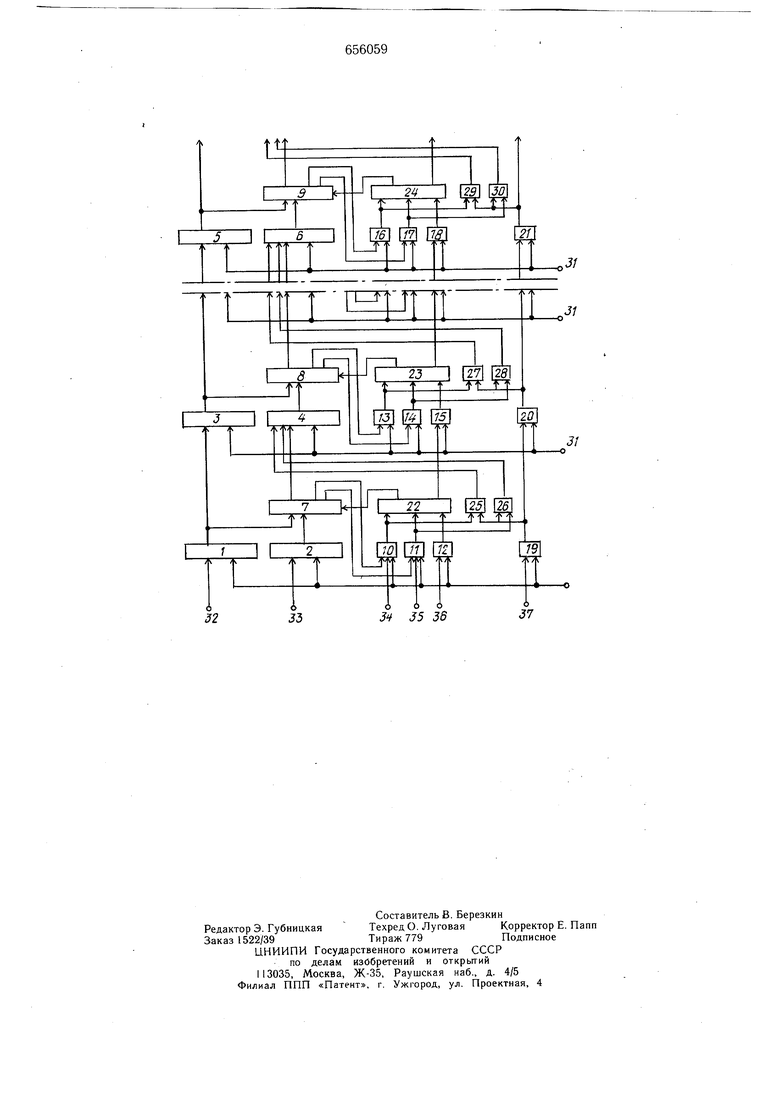

На чертеже изображена функциональная схема арифметического устройства, содержащего п 3 блоков.

Устройство содержит регистры 1-6, узлы формирования частичного произведения 7-9, триггеры 10-21, узлы формирования управляющих сигналов 22-24, элементы И 25-30, тактовые щины 31, шины ввода операндов 32, 33, управляющие шины 34-37. „ .1 - Тто+зк Тн+зк Tia.,.3K ;, + , -Тад-ьзкТм+зкТ ч-зк п T|o+3t T(.|-,.3if-T|2+3 и ак./ Т1о+зк-Т,ц.зи Ти+з и HK+I Т1о+з {Ти.зк V TIO где буквой Т с индексом обозначено состояние соответствующего триггера, а К О, 1, 2. Индекс при наименовании сигнала пока- 35 зывает, в каком блоке генерируется этот сигнал. Узлы формирования частичного произведения 7-9 формируют (п + 2) старших разрядов очередного частичного произведения в зависимости от управляющих сигналов следующим образом. Если управляющий сигнал «+ о, то на выходах узлов формирования частичных произведений 7-9 будут повторяться значения кодов регистров 2, 4, 6. Если управляющий сигнал «+а, то на выходах узлов формирования частичных про 45 изведений 7-9 будет код суммы содержимого регистров 1 и 2, 3 и 4, 5 и 6 соответственно. Если управляющий сигнал «+2а, то на выходах узлов 7-9 будет сумма содержимого регистров 2, 4, 6 и сдвинутого у на один разряд влево, содержимого регистров 1, 3, 5 соответственно. Если же управляющим сигналом является сигнал «- а, то на выходах узлов 7-9 будет разность содержимого регистров 2, 4, 6, и 1, 3, 5 соответственно. Сигнал переноса «П устанавливает триггеры 15, 18 запоминания переносов в следующих блоках в «1, если значение этого сигнала «1, и в «О, если значение его «О.

Регистры 1, 2, узлы 7, 22, триггеры 10, 11, 12, 19, элементы И 25, 26 устройства составляют первый блок. Регистры 3, 4 узлы 8, 23, триггеры 13, 14, 15, 20, элементы И 27, 28 устройства составляют его второй блок. Регистры 5, 6, узлы 3, 24, триггеры 16, 17, 18, 21, элементы И 29, 30 образуют третий блок устройства.

Для случая перемножения чисел регистры 1, 3, 5 являются регистрами сомножителя, регистры 2, 4, 6 - регистрами п старших разрядов частичных произведений, триггеры 12, 15, 18 - триггерами запоминания переносов, триггеры 10, 11, 13, 14, 16, 17 - триггерами хранения двух младших разрядов частичных произведений триггеры 19- 21 - триггерами формирования окончательного результата. Узлы формирования управляющих сигналов 22-24 предназначены для генерирования сигналов + о, -f а, + 2а, - а, управляющих работой узлов формирования частичных произведений 7-9 и триггеров 15, 18 запоминания переноса последую щих блоков. Эти сигналы вырабатываются в зависимости от состояний триггеров 10-18 в соответствии с логическими выражениями: Т +зкТ-и+зк T o- зкTVi-fSttTia+SKVE -i.3KTm.3if%j+at к Т|о+зк-Т,ц.з -Т«+зк SK Tia+ait В первом такте работы устройства первый сомножитель последовательности двоичных чисел принимается с шины ввода операнда 32 на регистр 1, по управляющим шинам 34, 35 приходят сигналы, устанавливающие триггеры 10, 11 в состояние «О и «1 соответственно. Сигнал на управляющей шине 36 устанавливает триггер 12 в состояние «О. Узел формирования управляющих сигналов 22 вырабатывает сигнал «+ а и так как в регистре 2 записан код «О, то на выходах узла формирования частичного произведения 7 появляется код. повторяющий код, записанный в регистр 1. Во втором такте работы устройства с выходов узла формирования частичного произведення 7, определяющих знйчения двух младших разрядов сомножителя, в триггеры 10, 11 запишутся значения этих разрядов, а с выходов старших разрядов информация перепишется в регистр 4 второго блока, и тем самым осуществляется сдвиг сомножителя, на два разряда вправо. В этом же такте код первого сомножителя перепишется в регистр 3 второго блока, а на регистр 1 запишется 1год нового сомножителя. Таким образом, во втором такте на выходах узла формирования частичного произведения 7 появится первое частичное провзведение от умножения двух сомножителей, причем младшие два разряда являются окончательными разрядами полного произведения двух сомножителей и в следуюш,ем такте могут быть сразу же использованы для умножения искомого произведения на следующий сомножитель последовательности. Поэтому в третьем такте работы устройства в регистр 1 принимается третий сомножитель. На выходах узла формирования частичного произведения 7 появится первое частичное произведение от умножения трех сомножителей, причем младшие пара разрядов этого произведения может быть использована в следующем такте для умножения на следующий сомножитель последовательности чисел и т. д. На основе кодов, записанных в триггерах 13 и 14 и кодов записанных в регистрах 3 и 4, на выходах узла формирования частичного произведения 8 появится второе частичное произведение, причем младшие два разряда его являются окончательными и определяют вторую пару цифр произведения двух первых сомножителей, код которой запишется в триггеры 13 и 14 и будет использован ,для умножения на третий сомножитель и т. д. Точность представления определяется состоянием триггеров 19-21, которое устанавливают подачей сигнала на управляющей шине 37. Если, например, в триггеры 19-21 записан код «1, то состояния триггеров 10, 11, 13, 14 и 16, 17 переписываются через элементы И 25-30 в два старших разряда регистров 4, 6 и т. д. Как отмечалось ранее, коды этих регистров сдвигаются в каждом такте на два разряда вправо и, таким образом, к моменту окончания умножения код результата оказывается на требуемой позиции. В (Е+ 1)-м такте можно принимать новую последовательность чисел для пере.множения. Следовательно, сохраняется основное преимущество конвейерного принципа обработки информации, заключающееся в эффективном использовании аппаратуры многорегистровых устройств. Полное произведение последовательности из Е чисел формируется за Е н---- тактов, в отличие от прототипа, который выполняет ту же операцию за Е + Е п тактов, где п - разрядность перемножаемых чисел, т.е. быстродействие устройства выше в (1 -Ь + -0) рэз. Так, для чисел разрядность которых 32 и больше разрядов, быстродействие увеличивается примерно в два раза. С помошью такого устройства наряду с умножением последовательности чисел возможно выполнение суммирования последовательности чисел, сдвига чисел, а также вычисление номинала типа /(X)..a,x.-fa и некоторые другие операции. Формула изобретения Арифметическое устройство, состоящее из п блоков, каждый из которых содержит первый и второй регистры, выходы которых соединены с первым и вторым входами узла формирования частичного произведения, два триггера, выходы которых соединены со входами первого элемента И, тактирующие входы регистров и триггеров соединены с тактовой щиной, выходы первого регистра и узла формирования частичного произведения, первого элемента И и первого триггера соединены соответственно со входами первого регистра, второго регистра первым дополнительным входом второго регистра и нулевым входом первого регистра последующего блока, единичный вход второго триггера соединен с первым дополнительным выходом блока формирования частичного произведения, входы регистров первого блока соединены с шинами ввода операндов, а нулевые входы триггеров первого блока - с соответствующими управляющими шинами, отличающееся тем, что, с целью повышения быстродействия, каждый блок устройства дополнительно содержит узел формирования управляюилих сигналов, второй элемент И, третий и четвертый триггеры, единичный вход третьего триггера соединен со вторым дополнительным выходом узла формирования частичного произведения, тактирующие входы третьего и четвертого триггеров подключены к тактовой щине, входы узла формирования управляющих сигналов подключены к выходам первого, второго и третьего триггеров, первый выход узла формирования управляющих сигналов подключен к управляющему входу узла формирования частичного произведения, а второй выход - к единичному входу четвертого триггера последующего блока, входы второго элемента И подключены к выходам первого и третьего триггеров, а выход второго элемента И подключен ко второму дополнительному входу второго регистра последующего блока, нулевые входы третьего и четвертого триггеров первого блока подключены к соответствующим управляющим щинам устройства. Источники информации, принятые во внимание при экспертизе: 1.Newborn Моцго Propogation logic structures, Ргос. Nat. Electron. Couf. Chicago, 1966, III, V. 22. 2.Авторское свидетельство СССР Xo 479111, кл. G 06 F 7/52, 1973.

Авторы

Даты

1979-04-05—Публикация

1976-09-27—Подача