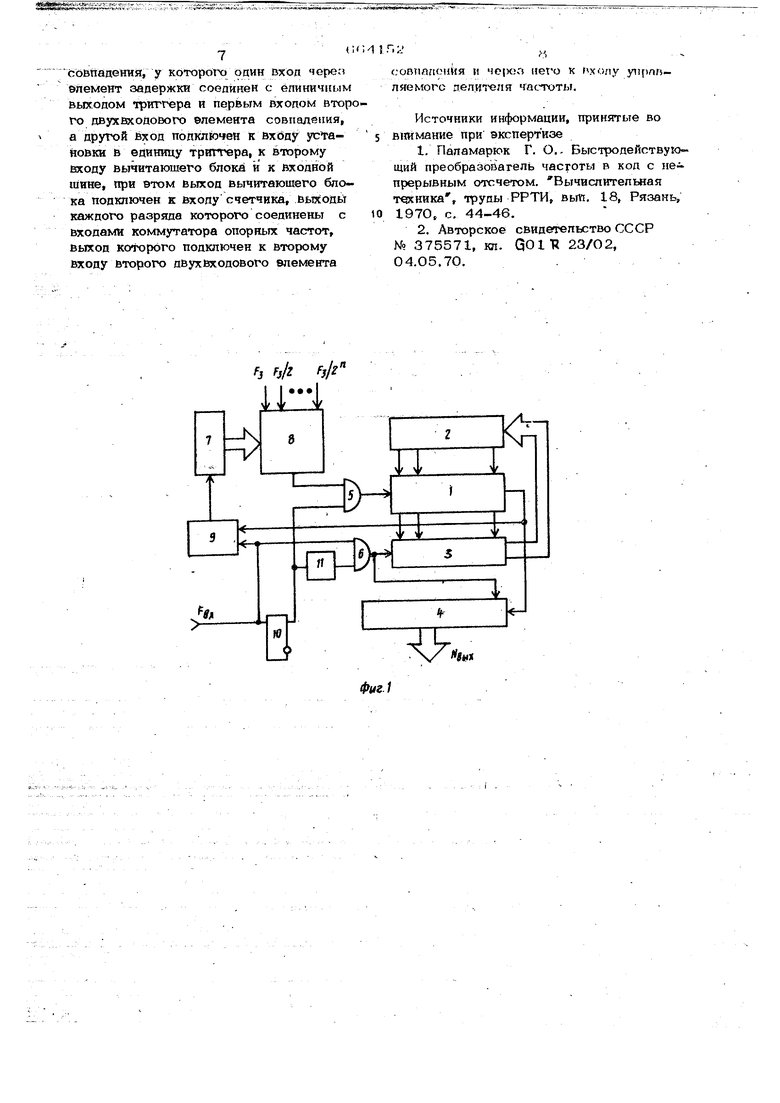

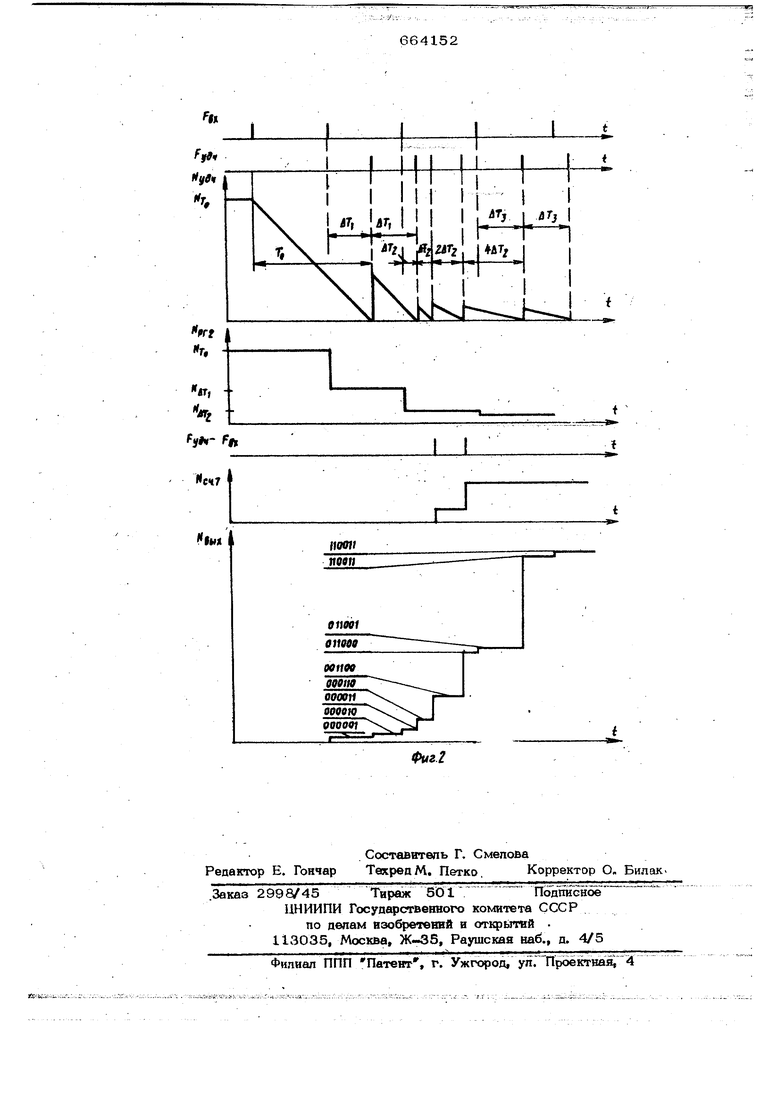

(54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД т&тор бтторных частот, два авухвходовых элемента совпадения, вычитающий бпок и элемент задержки, причем входные ши ны рёгистра памяти соединены через труппу элементов совпадения с единич ным вьвсодом соответствующих разрядов управляемотч) делителя частоты, а выход йереполнения управляемого делителя частоты соединен с первым Входом вычита щего блока и сдвигающей шиной регистр сдвига, у которого йход установки в единицу первого разряда соединен с вто рыми вводами группы элементов совпадения ивыходом первого двухвходового элемента совпадения, у которого один вход через элемент задержки соединен. с единичным выходом триггера и первым входом в.торого двухВходоВого элемента совпадения, а другой вход подключен к входу установки в единицу триггера, к второму входу вычитающего блока и к входной шине, при этом выход вычитающего блока подключен к входу счетчика, выходы каждого разряда которого соединены с входами коммутатора опорных частот, выход которого подключен к второму входу второго двухвходового элемента совпадения и через него к входу управляемого делителя частоты. На фиг. 1 приведена структурная электрическая схема устройства; на фаг. 2 - временные диаграммы, поясняю шие. его работу. Преобразователь частоты в код содержит управляемый делитель 1 частоты (УПЧ), регистр 2 памяти, группу элементов 3 совпадения, регистр 4 сдвига, двухвходбвые элементы 5. и .6 совпаде ния, счетчик 7, коммутатор 8 опорных частот, вычитающий блок 9, триггер 10 эпемент 11 задержки, Моделирующая зависимость Нщ,, пре Питаемого устройства имеет вид причем в устройстве вместо деления входной частоты Fg на опорную Ррп про изводится деление их периодов Т и TO т.е. при атом TQJ, выбирается из условия .N MH-on- Каждый i -и шаг деления состоит йа удвоения остатка, полученного на 6 .2А предыдущем ( 1 -IJ-OM шаге ( дТ. ) и его сравнении с периодом входной частоты T-g , Если ,2 , то i -му разрйпу частотного пр юваивается значение 1 и определяется i й остаток ЛТ - 1-1 5t Если 2 ДТ-j.-t то 1-му разряду частотного .присваивается значение О. В этом случае для следующего i+ 1 шага величина 2 является остатком , Палее процесс повторяется до получения последнетх), п -го, разряда Выходного Кода, Работает устройство следующим образом. В исходном состоянии счетчик 7 и триггер 10 обнулены, в регистр 2 и управляемый делитель 1 частоты записан код TQ , в регистр 4 записана 1 во второй разряд. Процесс преобразования начинается с приходом импульса преобразуемой частоты РВЧ который устанавливает триггер 1О в состояние 1. Приэтом опорная частота F о начинает через коммутатор 8 и открывшийся элемент 5 совпадения поступать на управляемый делитель 1 частоты. Таким образом, с приходом первого импульса Входной частоты начинается формирование интервала времени TQ Синхронность начала периода входной частоты T-g и периода TQ позволяет легко произвести их сравнение. Если , то второй импульс Входной часто«1 ты, пройдя элемент 6 совпадения, запишет 1 в младший разряд регистра 4 и откроет группу элементов 3 совпадения, через которые содержимое управляемого делителя 1 частоты, представляющее собой в этот момент остаток ,. перепишется в регистр 2 Тем. Фиг, 2). Первый импульс на выходе управляемого делителя 1 частоты, соот- ветствующий моменту окончания интервала TOI , произведет сдвиг содержимого регистра 4, .и вычтет из вычитающего блока 9, ранее записанную вторым импульсом входной частоты. Кроме того, в этбт момент (момент об нуления счётчика управляемого делителя 1 частоты), в управляемый делитель Частоты переносится содержимое регистра 2, т.е. код; первого остатка , который сразу же начинает преобразовываться в интервал Кок следует H;I фиг. 2, от момента прихопа второго импульса входной частоты это будет уже второй остаток А- ,т.е второй период входной частоты сравнивается с удвоенным остатком 2 дТ .Если 2дТ Твч f то третий импупьс входной частоты произведет изменения в схе ме, аналогичные действию ее второго им пульса, запишет 1 в младший разряд регистра 4 и перепишет код второго остатка МдТз 2 N о регистр 2 Следующий выходной импульс управляемого делителя 1 частоты (момент времени Tgy + 2дТ ) аналогично его первому импульсу, начнет формирование второго остатка Ф изображен случай, когда ,при этом выходной импульс управляемого де лителя 1 частоты, пройдя вычитающий блок 9, запишет в счетчик 7. Повтому с коммутатора 8 на влемент 5 совпадения вместо частоты FO начнет поступать частота Fo/2. Следовательно, управляемый делитель ,1 частоты начнет формировать интервал времени 2лТ - .NAT 2 2- Если з) -ATg , то импульс с выхода делителя 1 частоты (момент времени .Т,) снова сдвинет . содержимое регистра 4 и, пройдя вы-, читающий блок 9, поступит в счетчик 7, увеличивая его содержимое на I. При этом коммутатор 8 переключит частоту с FO / 2 на FO /4 а управляемый делитель 1 частоты начнет формировать интервал, Итак, предыдущий остаток удваивается до тех пор, пока не. превысит период входной частоты. Выходной код формируется в регистре 4 цифра за цифрой, начиная со старшего разряда, путем записи влево. После П сдвигов записанная до начала работы из Второго разряда регистра 4 переместится в ( h+ 1)-й разряд, что является сигналом окончания преобразования. Время преобразования достигает максимума при gbtx равно ,. Для оцопки выигрыша в быстродейстВИИ считаем, что входная частота и раз0526 рялкость выходного кода у прототипа и данного преобразователя равны между собой и равны максикшльно возКюжным 1 для данных преобразователей величинам, так как БХ БХ.(КС (худший случай для данного преобразователя устройства). Время преобразования для прототипа равно пр- С учетом соотношения .- Bjt.MOIKC Vг пр F, &х. B)i.MaKc Для предлагаемого устройства врет«ш преобразования равно ( ,ЛЛИН Выигрьпи в быстродействии равен 2 и, например, для десятиразряпного кодй составляет 100. Существенно увеличенное быстродействие предлагаемое устройство позволяет использовать jDinfl преобразования быстроизменяющихся входных частот. Формула изобретения Преобразователь частоты в код, содержащий управляемый делитель частоты, входы которого подключены к разрядным выходам регистра памяти, группу . ментов совпадения, счетчик, отличающийся тем, что, с целью уменьще1Ц1Я времени преобразования, в него дополнительно введены два регистра сдвига, триггер, коммутатор опорных частот, два двухвходовых элемента совпадения, вычитающий блок и элемент задержки, причем входные шины регистра пам5гги соединены через группу элементов совпадения с единичным выходом соответствующих разрядов управляемого делителя частоты, а выход переполнения управляемого делителя соединен с первым Входом вычитающего блока и сдвигающей шиной регистра сдвига, у которого Вход установки в единицу первого разряда соединен с вторыми входами группы элементов совпадения и выодбм первого двухвходового элемента

совпадений, У которотх) один вход черен епемент задержки соединен с епиничным выходом триггера и первым входом второtO двухвхоДоВого ©лемента совпадения, а друтх)й Ёход подклЬэчен к входу у гайоьки в единицу триггера, к второму входу вычитающего блоки и к входной шине, при ВТОМ выход вычитающего блока подключен к входу счетчика, выходы каждого разряда которотчэ соединены с входами коммутатора опорных частот, выход которого подключен к второму входу второго двухвходового элемента

(;oBtinrioiiiifl н че|юп него к r xo/iy уцрппляемогс пел.ипчгпя час-тоты.

Источники информации, принятые во внимание при экспертизе

1.Паламарюк Г. О,. Быстродействующий преобразойагель частоты в код с непрерывным отсчетом. Вычислительная те сника, трупы РРТИ, вьт, 18, Рязань, 1970. с. 44-46.

2.Авторское свидетельство СССР Мо 375571, кл. Qom 23/О2, 04.05.70,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частота-код | 1979 |

|

SU839047A1 |

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Преобразователь отношения двух частот в код | 1976 |

|

SU660231A1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| Цифровой кодирующий преобразователь частоты | 1980 |

|

SU938402A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| Цифровой частотомер мгновенных значений | 1990 |

|

SU1783451A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

j fj/г fj/г

U

Авторы

Даты

1979-05-25—Публикация

1976-03-09—Подача