(54) ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА - КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Преобразователь частоты в код | 1976 |

|

SU664152A1 |

| Умножитель частоты | 1987 |

|

SU1499341A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

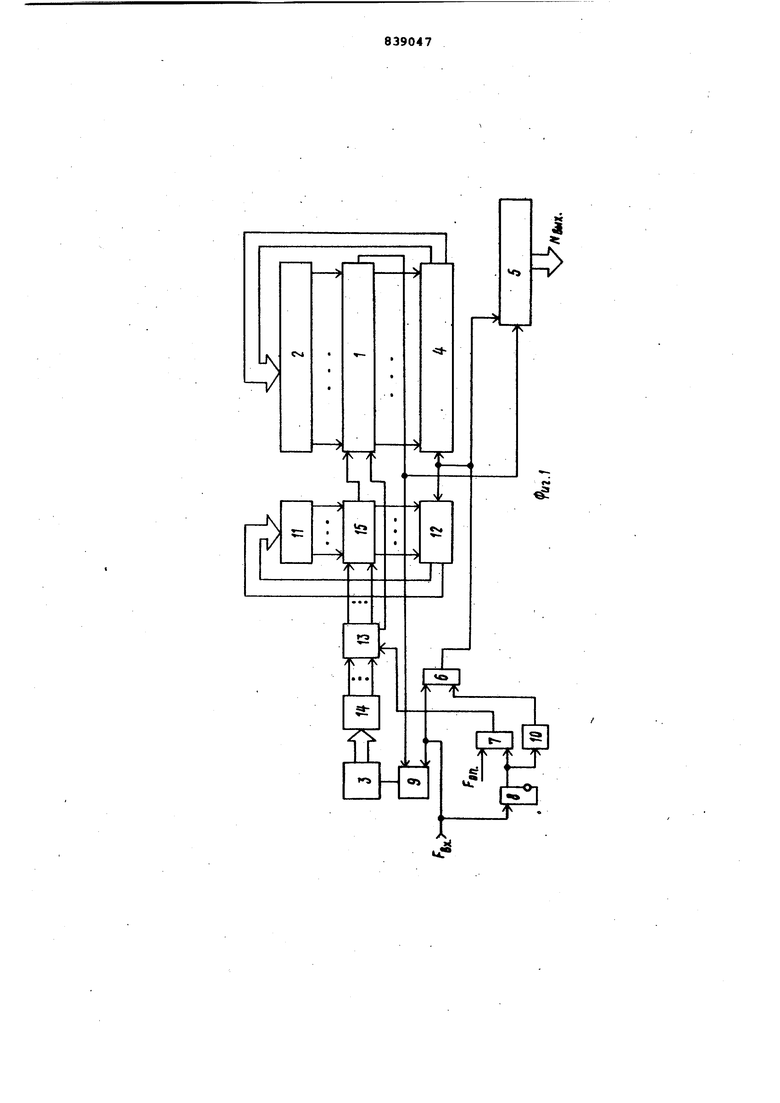

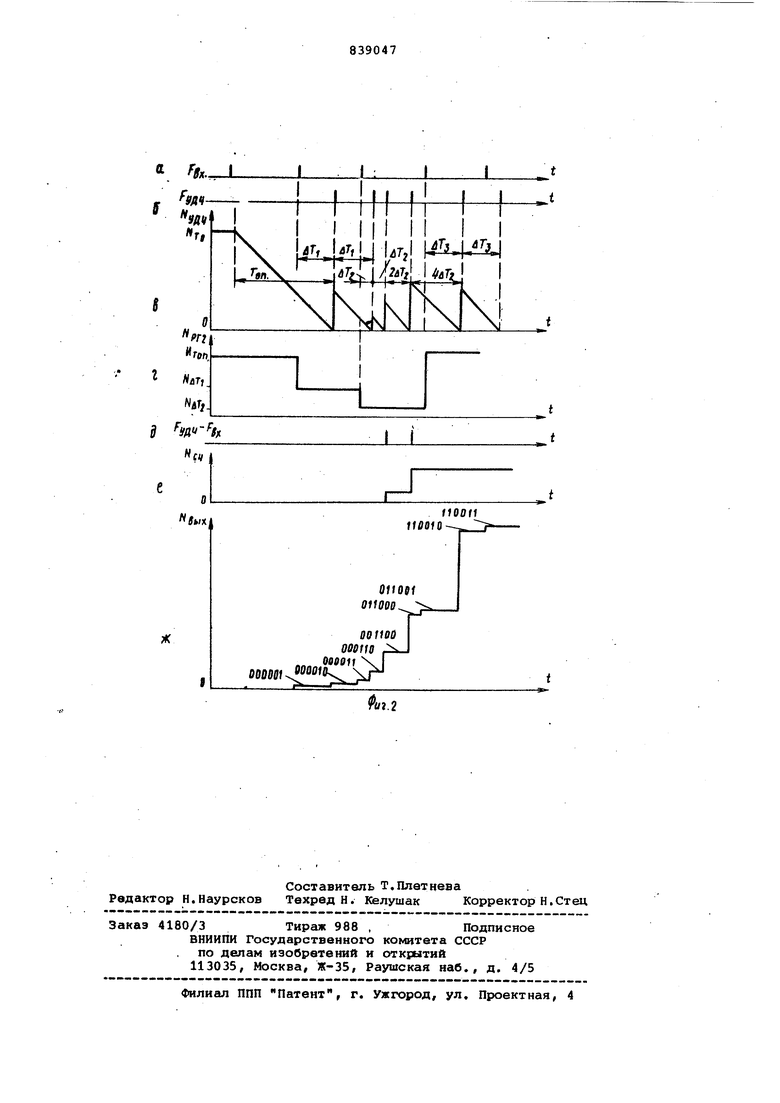

Изобретение относится к вычислительной технике и автоматике и может быть использовано в системах управления движущимися объектами в качестве преобразователя частотной информации в цифровой код. Известен преобразователь частоты в код следящего типа, содержащий реверсивный счетчик, делитель опорной частоты и двоичный умножитель, выход которого соединен с вычитающи входом реверсивного счетчика, а соо ветствующие входы соединены с выходами делителя частоты и реверсивного счетчика ll. Передаточная фу ция такого преобразователя аналогич на передаточной функции инерционног звена - постоянная времени, зависящая от числа разрядов п ревер сивного счетчика и опорной части F 1. ° Однако для обеспечения высокой т ности п должно выбираться достаточно большой величины, что не позволяет получить высокого быстродейств преобразователя. Наиболее близким по технической сущности К--предлагаемому является преобразователь частоты в код, содержащий регистр памяти, управляемый делитель частоты, входы которого подключены к разрядным выходам регистра памяти, группу элементов И, счетчик, регистр сдвига, триггер, коммутатор опорных частот, два двухвходовых элемента И, вычитающий блок и элемент задержки, причем входные шины регистра памяти соединены через группу элементов И с единичным выходом соответствующих разрядов управляемого делителя частоты, а выход переполнения управляемого делителя частоты, соединен с первым входом вычитающего блока и сдвигающей шиной регистра сдвига, у которого вход установки в 1 первого разряда соединен со вторыми вхрдаки группы э хементов И и выходом первого двухвходового элемента И, у которого один вход через элемент задержки соединен с единичным выходом триггера и первым входом второго двухвходовогс элемента И, а другой вход подклкмен ко входу установки в 1 триггера, ко второму входу вычитагацего блока и ко входной шине, при этом выход вычитаищеГО блока соединен со входом счетчика, выходы каждого разряда которого соединены со входами коммутатора опо ных частот, выход которого додключе ко второму входу второго двухвходов го элемента совпадения и через него ко входу управляемого делителя частота 2 . Недостатками такого преобразователя являются погрешности, обусловленные принятым способом прео бразования кода ,-i -ого остатка л в удвоенный временной интервал с помощью набора стабильных частот fj, /2 , соответствии с формулой При этом погрешности операции(1) обусловленные несовпадением момента начала 1„ преобразования ,.; и момента появления ближайшего импульса частоты Fo/2,обратно пропорциональны величине Ро/2 и в максимуме равны . Таким образом, если 1анная погрешность на вто ром шаге работы устройства равна 2/Fc) , то на последнем шаге она увеличивается в раз. Цель изобретения - повышение точности. Указанная цель достигается тем, что в преобразователь частоты в код, содержащий регистр памяти, выходы разрядов которого через основной управляемый делитель частоты подключены ко входам основной групп элементов И, выходы которой соединены с информационными входами регистра памяти, выход переполнения основного управляемого делителя частоты соединен с первым входом вычитающего блока и сигнальным входом регистра сдвига, вхо/i установки 1 первого разряда которого сое динен с управляющим входом основной группы элементов И и выходом первого элемента И, первый вход которого соединен с входйой шиной, входом триггера и вторым входом вычитаквдего блока, которого соединен со входом счетчика, прямой выход тр гера подключен через элемент задерж ки ко второму входу первого элемента И и непосредственно к первому входу второго элемента И, дополнительно введены дешифратор, две груп пы элементов И, управляемьгй делитель частоты и регистр памяти, причем выходы счетчика через дешифрато подключены ко входам первой дополни тельной группы элементов И, сигналь ный вход которой соединен с выходом второго элемента Я, второй вход кот рого подключен к шине опорной часто ты, выходы первой дополнительной гр пы элементов И подключены к первой группе входов дополнительного управляемого делителя частоты, вторая группа входов которогЬ соединена с выходами разрядов регистра памяти, входы которого подключены к выходам второй ополнительной группы элементов И, входы которой соединены с выходами разрядов дополнительного делителя частоты, первый и второй дополнительные входы основного управляемого делиеля частоты подключены к дополнительным выходам соответственно дополнительного управляемого делителя -частоты и первой дополнительной группы элементов И, управлягаций вход второй дополнительной группы элементов И соединен с выходом первого элемента и. . На фиг. 1 приведена блок-схема устройства, на фиг. 2 - временные диаграммл, поясняющие его работу. Преобразователь частота - код содержит управляемый делитель 1 часто-, ты, регистр 2 памяти, счетчик 3, группу 4 элементов И, регистр 5 сдвига, элементы 6 и 7 И, триггер 8, вычитающий блок 9, элемент 10 задержки, регистр 11 памяти, группы 12 и 13 элементов И, дешифратор 14 и дополнительный управляемый делитель 15 частоты. При этом входы управляемого делителя 1 частоты подключены к разрядным выходам регистра 2 памяти, входные шины которого соединены через группу 4 элементов И с разрядными выходами управляемого делителя 1 частоты, выход переполнения которого соединен с первым входом вычитающего блока 9 и двигающей шиной регистра 5, у которого вход установки в 1 первого разряда соединен со вторыми входами группы 4 элементов И и выходом элемента И б, у которого один вход через элемент 10 задержки сое;инен с единичным выходом триггера 8 и первым входом элемента И 7, а другой вход подключен ко входу установки в 1 триггера 8, ко второму входу . вычитающего блока 9 и к шине входной частоты, а выход вычитающего блока 9 подключен ко входу,счетчика 3. Входные шины регистра 11 памяти соединены через группу 12 элементов И с разрядными выходами дополнительного управляемого делителя 15 частоты, подключеннах к младшему разряду последнего. Каждый из дополнительных разрядов имеет второй вход, соединенный с выходом одного из элементов И группы 13, у которых первые входы соединены с выходом элемента 7И, второй вход которого соединен с шиной опорной частоты, а вторые - с соответствующими выходами дешифратора 14, входы которого соединены с разрядными выходами счетчика 3.Младший разряд управляемого делителя 1 частоты также имеет дополнительный вход,соединенный с выходом соответствующего эл мента группы 13. Устройство работает следующим образом. Мод-елирующая зависимость Nj устройства имеет вид М,к. 2 F /FQ, причем в устройстве вместо деления входной частоты F на опорную , производится деление их периодов Г Ф м т т оN - -ь ОПiftx. и Т(,п,т.е. ibir Топ. выбирается из условия , , Каждый 1 - ый шаг деления состоит из удвоения остатка, полученного на предыдущем -i -1-ом шаге (Л4 -l) и его сравнении с периодом входной частоты Tjj . Если ,.,Tjx, то i -ог разряду частотного присваивается значение 1 и определяется i -ый остаток 2й;.,-Т|х . Если .44Tg , то i -ому разряду частного присва ивается значение О. В этсм случае для следующего | +1 шага величина 2д; является остатком л . далее процесс повторяется до получения последнего п -го разряда выходного кода. В исходном состоянии счетчик 3 и триггер 8 обнулены, в регистр 2 и управляемый делитель 1 Частоты записан код МТ,,, Топ F,, в регистр записана, во второй разряд. Процесс преобразования начинается с приходом импульса преобразуемой частоты Fgy , который устанавливает триггер 8 в состояние 1, при этом опорная частота f начинает через группу 13 элементов И и открывший.ся элемент И 7 поступать на управляемой делитель 1 частоты. Таким образом, с приходом первого импульса входной частоты на чинается форми рование интервала времени Т.Синхронность начала периода входной час тоты Tg)t и периода Тдп позволяет легк произвести их сравнение. Если Тр то второй импульс входной частоты, проходя элемент 6, записывает 1 в младший разряд регистра 5 и откры вает группу 4 элементов, через кото рые содержимое управляемого делителя 1 частоты, представлягацее собой в этот момент остаток М п/перепишется в регистр 2 (фиг. 2). Первый импульс на выходе управляемого делителя 1 частоты, соответствующий моменту окончания интервгша Tjjf, производит сдвиг содержимого регист ра 5, и вычитает 1 из вычита1С1цег блока 9, ранее записанную вторым импульсом входной частоты. Кроме то в этот момент (момент обнуления сче чики управляемого делителя 1 частоты; в управляемый делитель 1 частот переносится содержимое регистра 2, т.е. код первого остатка Нд4,.который сразу же начинает преобразовываться в интервсш времени &f . Как следует из фиг. 2, от момента прихода второго импульса входной частоты это будет уже второй остаток м , т.е. второй период входной частоты сравнивается с удвоенным остатком 24. Если 2д Tgj , то третий импульс входной частоты производит изменения .в схеме, аналогичные действию ее второго импульса, записывает 1 в младший разряд регистра 5 и переписывает код второго остатка H5a2N,4 -Tj.-. в регистр 2. Следующий выходной импульс управляемого делителя 1 частоты (момент времени ) аналогично его первому импульсу начнет формирование второго остатка да:N(u/(J. на фиг. 2 изображен случай, когда . При этом выходной импульс управляемого делителя 1 частоты, пройдя вычитающий блок 9, записывает 1 в счетчик 3. При этом высокий потенциал появляется на второй шине дешифратора 14 и исчезает на его первой шине, что открывает второй элемент И из группы 13, выход которого соединен со входом старшего из разрядов делителя 15, и закрывает первый элемент И из группы 13, выход которого связан со входом управляемого делителя 1 частоты. Подключение сдного дополнительного разряда ко входу управляемого делителя 1 частоты аналогично увеличению .его содержимого вдвое (.j). Следовательно, управляемый делитель 1 частоты начнет формировать интервал времени , Если Tgy , то импульс с выхода делителя 1 частоты ( момент времени 2Tgy- -4Aj) снова сдигает содержимое регистра 5 и, пройдя вычитакщий блок 9, поступает в счетчик 3, увеличивая его содержимое на 1. При этом дешифратор 14 с помощью группы 13 элементов И подключает к управляемому делителю 1 частоты еще один дополнительный разряд иэ делителя 15. Вследствие этого формируется интервал . Итак, предыдущий остаток удйаивается до тех пор,.пока не превысит период входной частоты. Выходной код формируется в регистре 5 цифра за цифрой, начиная со CTajKiiero разряда, путем записи 1 в первый разряд регистра 5 и последующего сдвига в сторону стаЕнпих разрядов. После (п -11 сдвигоэ записанная до начала работы 1 из второго разряда регистра 5 перемацается в (п+1Ьый разряд, что является сигналом окончания преобразования. Погрешность возникает на тех шагах преобразования, где очередной импульс, входной частоты производит перезапись содержимого управляемого делителя 1 частоты и дополнительного делителя 15 в регистры 2 и 11 т.е. если значение очередной К цифры выходного кода равно 1. На всех последующих шагах эта погрешност преобразования, не превышающая в личину периода опорной последова ности I/FO t удваивается, в соот ствии с изложенным максимальная ввли.чина погрешности временного и тервала равна (.к,,лк,..2)|(), где К, К2...,К„ - значение цифр выходного кода ( О или 1). Наиболь шего значения ДТ достигает при V. бьл.тах 11... -1 в известном устр1ойстве 1 имеется два источника погрешности. Пер вая из них совпадает с погрешност предлагаемого устройства. Источни ком второй является принятый способ удвоения временных интервалов путем переключения рпорной частоты с FO/2 на При этом изза несинхронности конца предыдуи го преобразования (0 и начала последующего ( / т.е. несинхронности момента начала преобразования кода остатка МдГ в интервал времени с началом периода после довательности FO/2.возникает погрешность AT-i/(Fo2) , которая на всех последуквдих шагах преобразования удваивается. Наибольшей ве личины рассматриваемая составлякща погрешность достигает при М,,,, ,т,|-п:: Согласно логике работы устройства ее величина при этом равна .т;.Ми-2)) Суммарная погрешность известно устройства равна Отношение погрешностей известного устройства С23 и предлагаемого устрой ва составляет ,. Таким образом, точность предлага емого устройства в п/2 раз выше известного. Формула изобретения Преобразователь частота - код, содержащий регистр памяти, выходы разрядов которого через основной управляемый делитель частоты подключены ко входам основной группы элементов И, выходы которой соединены с информационными входами регистра памяти, выход переполнения основного управляемого делителя частоты ооединен с первым входом вычитающего блока и сигнальным входом регистра сдвига, вход установки 1 первого разряда которого соединен с управляющим входом основной группы элементов И и выходом первого элемента И, первый вход которого соединен с входной шиной, входом триггера и вторым входбм вычитающего блока, выход которого соединен со входом счетчика, прямой выход триггера подключен через элемент задержки ко второму входу первого элемента И и непосредственно к первому- входу второго элемента И, отличающийся тем, что, с целью повышения точности, в него дополнительно введены дешифратор, две группы элементов И, управляемый делитель частоты и регистр памяти, причем выходы счетчика через дешифратор подключены ко входам первой дополнительной группы элементов И, сигнальный вход которой соединен с выходом второго элемента И, второй вход которого подключен к шине опорной частоты, выходы первой дополнительной группы элементов и подключены к первой группе входов дополнительного управляемого делителя частоты, вторая группа, входов которого соединена с выходами разрядов регистра памяти, входы которого подключены к выходам второй дополнительной групгм элементов И, входы которой соединены с выходами разрядов ополнительного делителя частоты, первый и второй дополнительные вхоы основного управляемого делителя астоты подключены к дополнит(льным ыходам соответственно дополнителього управляемого делителя частоты первой дополнительной группы элеентов И, управляющий вход второй ополнительной группы элементов И оединен с выходом первого элемена И. Источники информации, ринятые во внимание при экспертизе 1.Папамарюк Г.О. Быстродействуюий преобразователь частоты в код непрерывным отсчетом. Вычислительая техника. Труды РРТЙ. Рязань, 1970, ып. 18, с. 44-46. 2.Авторское свидетельство СССР 664152, кл. Н 03 К 13/20, 1979.

W

hS

г-А

«N

И

/ /V

.J

а л.1

Ж

Авторы

Даты

1981-06-15—Публикация

1979-09-05—Подача