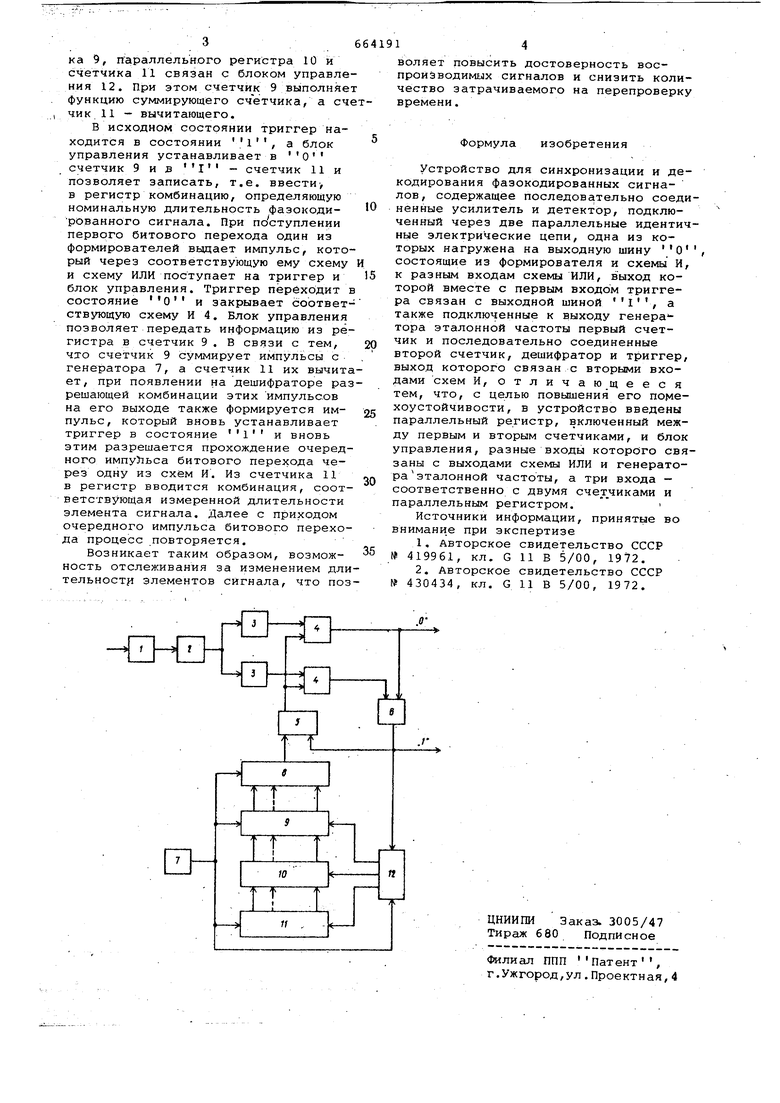

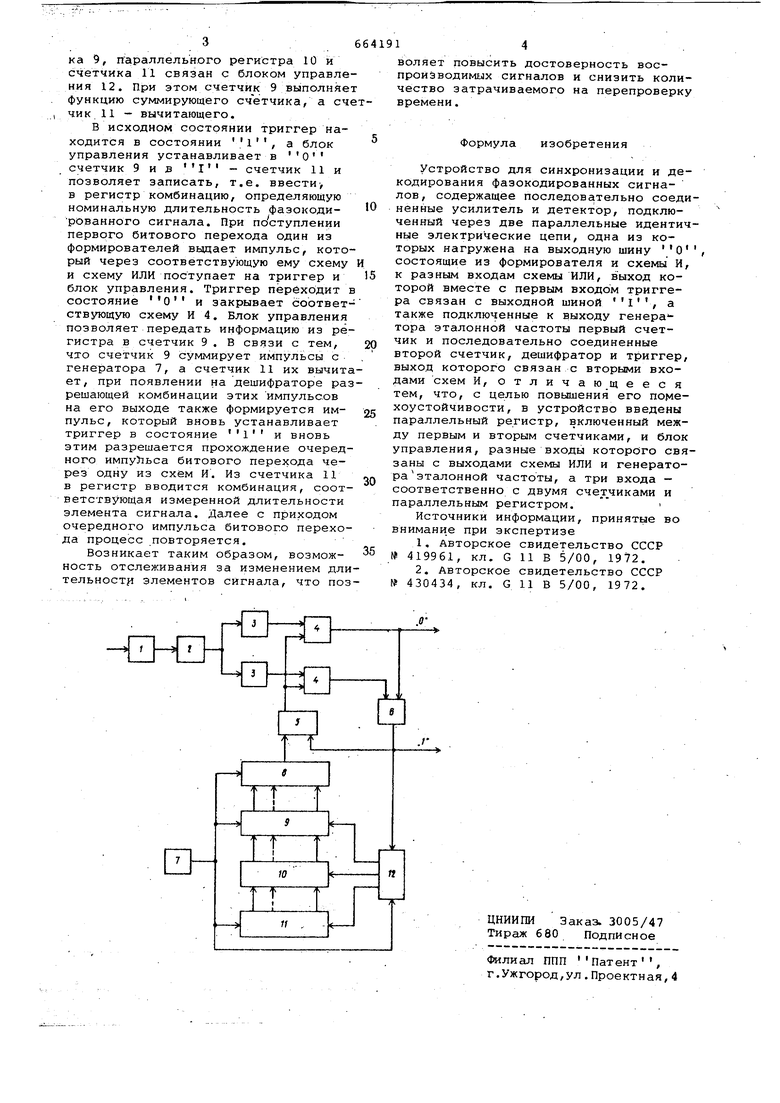

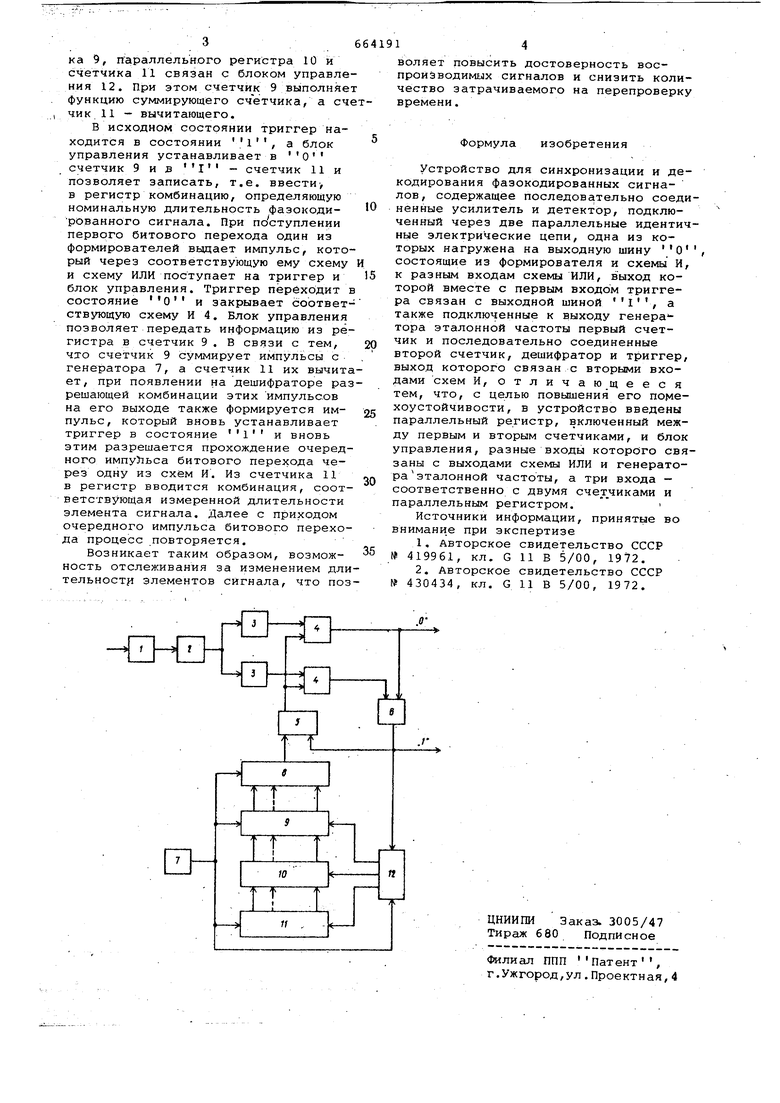

3 ка 9, параллельного регистра 10 и счетчика 11 связан с блоком управле ния 12. При этом счетчик 9 выполняе функцию суммирующего счетчика, а сч чик. 11 - вычитающего. В исходном состоянии триггер находится в состоянии , а блок управления устанавливает в О счетчик 9 ив - счетчик 11 и позволяет записать, т.е. ввести в регистр комбинацию, определяющую номинальную длительность фазокодированното сигнала. При поступлении первого битового перехода один из формирователей выдает импульс, кото рый через соответствующую ему схему и схему ИЛИ поступает на триггер и блок управления. Триггер переходит состояние и закрывает соответ ствующую схему И 4. Блок управления позволяет передать информацию из ре гистра в счетчик 9. В связи с тем, что счетчик 9 суммирует импульсы с генератора 7, а счетчик 11 их вычит ет, при появлении на дешифраторе ра решающей комбинации этих импульсов на его выходе также формируется импульс, который вновь устанавливает триггер в состояние i и вновь этим разрешается прохождение очеред ного импуЛьса битового перехода через одну из схем И. Из счетчика 11 в регистр вводится комбинация, соот ветствующая измеренной длительности элемента сигнала. Далее с приходом очередного импульса битового перехо да процесс повторяется. Возникает таким образом, возможность отслеживания за изменением дли тeльнocт элементов сигнала, что по 14. воляет повысить достоверность воспроизводимых сигналов и снизить количество затрачиваемого на перепроверку времени. Формула изобретения Устройство для синхронизации и декодирования фазокодированных сигналов, содержащее последовательно соединенные усилитель и детектор, подключенный через две параллельные идентичHtje электрические цепи, одна из которых нагружена на выходную шину состоящие из формирователя и схемы И, к разным входам схемы ИЛИ, выход которой вместе с первым входом триггера связан с выходной шиной , а также подключенные к выходу генера тора эталонной частоты первый счетчик и последовательно соединенные второй счетчик, дешифратор и триггер, выход которого связан с вторыми входами схем И, отличающееся тем, что, с целью повышения его помехоустойчивости, в устройство введены параллельный регистр, включенный между первым и вторым счетчиками, и блок управления, разные входы которого связаны с выходами схемы ИЛИ и генератора эталонной частоты, а три входа соответственно с двумя счет чиками и параллельным регистром. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР I 419961, кл. G 11 В 5/00, 1972. 2.Авторское свидетельство СССР № 430434, кл. G 11 В 5/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения фазомодулированных сигналов | 1978 |

|

SU771711A1 |

| Устройство для воспроизведения фазомодулированных сигналов | 1978 |

|

SU714475A1 |

| Устройство для воспроизведения фазомодулированных сигналов | 1982 |

|

SU1065873A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Многоканальный измеритель интенсивности импульсов | 1991 |

|

SU1807423A1 |

| Устройство межмашинной связи | 1987 |

|

SU1474666A1 |

| Устройство цикловой синхронизации | 1988 |

|

SU1721835A1 |

| Устройство для контроля аппарата магнитной записи | 1988 |

|

SU1607012A1 |

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1984 |

|

SU1185617A2 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

Авторы

Даты

1979-05-25—Публикация

1977-08-01—Подача