щего триггера, с вторым выходом генератора управляющих импульсов и входом элемента задержки, выход шестого элемента ИЛИ подключен к тактовым входам дополнительного регистра сдвига и регистра сдвига, выход счетчика времеЯи подключен к входу сброса формирователя импульсов, выходы разрядов счетчиков ошибок и счетчика времени подключены соответственно к входам мультиплек

185617

сора счетчиков и дополнительного мультиплексора счетчиков через первый и второй промежуточные накопители, управляющие входы которых соединены с выходом третьего элемента ИЛИ, управляющие входы и выходы дополнительного мультиплексора счетчиков соединены соответственно с выходами первого счетчика импульсов и в-ходами общего мультип- прксора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Тренажер для обучения сварщиков | 1986 |

|

SU1441446A1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство телеконтроля регенераторов цифровой системы передачи | 1985 |

|

SU1261125A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПОКАЗАТЕЛЯ ГРУППИРОВАНИЯ ОШИБОК В ДИСКРЕТНОМ КАНАЛЕ СВЯЗИ по авт. св. № 1016845, отличающеес я тем, что, с целью повьшения достоверности путем измерения дополнительных характеристик потока ошибок, в устройство введены дополнительный мультиплексор счетчиков, переключатель этапов измерения, фор мирователь импульсов, первый и второй промежуточные накопители, второй дополнительный переключатель, второй датчик константы управления, пятый и шестой элементы ИЛИ, дополнительный управляющий триггер, переключатель задержки, элемент задержки, V счетчиков, первый выход переключателя режима работы подключен к установочному входу формирователя импульсов, прямой выход которого подключен к входу генератора управляющих импульсов, к установочному входу дополнительного управляющего триггера, к первому управляющему входу переключателя этапов измерения и к первому управляющему входу второго дополнительного переключателя, первые сигнальные входы которого соединены с выходами второго датчика константы управления, выходы третьего счегчика импульсов соединены с соответствующими входами первого дополнительного переключателя через второй дополнительный переключатель, второй выход переключателя режима работы соединен с соответствующими входами триггеров через счетчиков, инверсный выход формирователя импульсов подключен к вторым управляющим входам второго дополнительного переключателя и переключателя этапов измерения, информационный вход и первый и второй выходы которого соединены соответственно с выходом четвертого разряда регистра сдвига, с .. входом пятого разряда регистра сдвига и с объединенными третьим входом первого элемента ИЛИ и первым вхоое дом пятого элемента ИЛИ, второй, третий и четвертый входы которого т соединены соответственно с выходами первого, третьего и десятого раз-, рядов регистра сдвига, а выход пятого элемента ИЛИ подключен к установочному входу дополнитель.юго уп равляющего триггера, вход сброса которого соединен с выходом элемента задержки и с первым входом шестого элемента ИЛИ, второй вход которого соединен с первьпч выходом переключателя задержки, лервый и второй управляющие входы, информационный вход и выход которого соединены соответственно с инверсным и прямым выходами дополнительного управляю

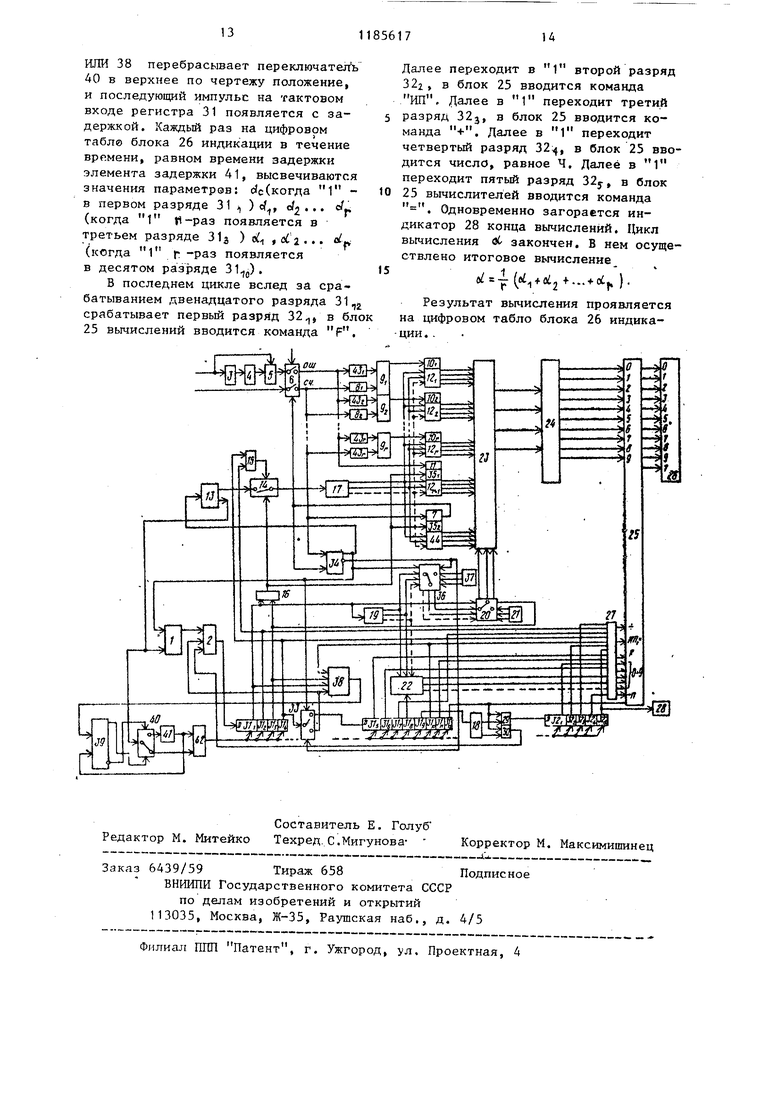

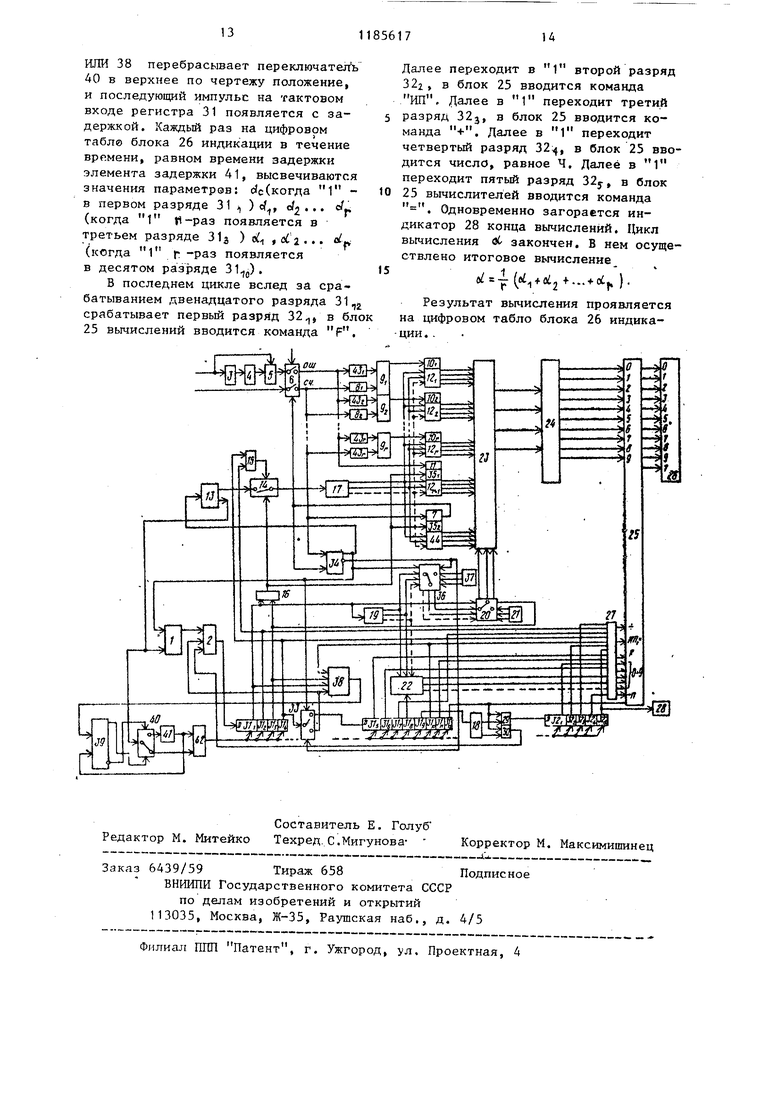

Изобретение относится к технике электросвязи и может использоваться при построении систем передачи дискретной информации. Цель изобретения - повышение достоверности за счет измерения дополнительных характеристик потока ошибок. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство для измерения показателя группирования ошибок в дискретном канале связи содержит управляющий триггер 1, первый элемент ИЛИ 2 блок 3 фазирования, датчик 4 эталонных сигналов,блок 5 сравнивания,переключатель 6 режима работы, счетчик 7 времени, г делителей 8,, триггеров 9,,- 9р, Г счетчиков искаженных блоков, счетчик 11 ошибок, f+l мультиплексоров 1 счетчиков, генератор 13 управляющих импульсов, ключ 14, второй и третий элементы ИЛИ 15 и 16, первый, второй и третий счетчики 17, 18 и 19 импульсов, первый дополнительный пе реключатель 20, датчик 21 константы управления, блок 22 памяти, общий { льтиплексор 23, дешифратор 24, бл 25 вычислений, блок 26 индикации-, блок 27 объединения сигналов, индикатор 28 конца вычислений, первый и второй элементы И 29 и 30,- регистр 31 сдвига с разрядами 31т 31 дополнительный регистр 32 с разрядами 32J, переключатель 33 этапов измерения, формирователь 34 импульсов, первый и вторЬй промежуточные накопители 35 и 35 , второй дополнительный переключатель 36, второй датчик 37 константы управления, пятьй элемент ИЛИ 38, дополнительный управляющий триггер 39, переключатель 40 задержки, элемент задержки 41, шестой элемент ИЛИ 42, г счетчиков 43f., дополнительный мультиплексор 44 счетчиков. Устройство работает следующим образом. К моменту начала измерений сигнальньш вход и вход синхроимпульсов устройства соединены с выходом дискретного канала связи. Устройство работает в два этапа, Ь первом этапе производится изме-. рение параметров потока ошибок в канале, он длится определенное время, называемое сеансом. Счетчики lOj, подсчитьгаают число искаженных блоков разной длины, причем число ошибок в блоках выбирается заранее. В счетчике 11 накапливается число ошибок за весь сеанс связи. Длительность (длина) сеанса связи определяется скоростью работы дискретного канала и емкостью счетчика 7-. Она равна TL секунд, где Т - длительность бита (период синхроноимпульсов), L- емкость счетчика 7. Одновременно производится вычисление текущих и окончательного значений коэффициента ошибок. При этом на цифровом табло блока 26 индикации высвечиваются значения числа ошибок ( d , ) длина сеанса связи (L, Lj. ), а затем значения коэффициента ошибок (К, , Кд).

После окончания сеанса связи начинается второй этап, в котором производится вычисление частных значений показателя группирования и его среднего значения.

Время вычисления зависит от быстродействия блока 25 вычислений, примененньпс микросхем, времени задержки элемента 41 и определяется генератором 13 управляющих импульсов.

При этом на цифровом табло блока 26 индикации последовательно высвеч ваются общее число ошибок в сеансе () число блоков определенной дли (dfi) и частное значение показате ля грздтпирования (d) , После вычисления всех частных значений показателя группирования (d р вычисляется, а затем высвечивается на табло среднее значение показателя группировлния за сеанс связи. Информационные сигналы с помощью блока 3 фазирования, выделяющего из приходящей информации комбинацию синхронизации, осуществляют фазирование датчика 4. Блок 5 производит поразрядное сравнивание поступаю щей с датчика 4 эталонных сигналов с входной последовательностью. Результатом сравнения является поток ошибок, который поступает на переключатель 6. На другой вход этого переключателя поступают синхроимпуль сы, сопровождающие поток ошибок. Первый этап измерения начинается замыканием переключателя 6 (оператором или автоматом), при этом поток ошибок (ошибке соответствует сигнал 1) поступает на вход счетчика 11 и на входы счетчиков 43., которые служат для подсчета ошибок в соответствии с выбранным критерием искаженности - m (блоки считаются искаженными, если число ошибок в нем т). Далее сигнал с выходов счетч ков 43;)- 43f. поступает на входы триг геров 9ц- Эр-р синхроимпульсы, период которых равен длительности одного бита информации - на входы счетчика 7 и делителей BL, m-ой ошибкой триггеры 9j, устанавливаются в 1, а импульсами с выходов этих триггеров счетчики 10 .устанавл ваются в состояние 1, Ctinif4HK 1

также устанавливается в состояние 1 непосредственно импульсом ошибки. Последующие импульсы, поступающие на входы f триггеров 9,- 9

не оказьшают на них действия и, следовательно, не оказывают действия на счетчики 10, так как триггеры уже находятся в состоянии Ч, и так до тех пор, пока триггеры 9 - 1

не переведутся в состояние О. Такой перевод осуществляется импульсами с выходов делителей 8,, поскольку йа входы этих делителей поступают синхроимпульсы, импульсы появляются на их выходах с периодами п,, Пл «I (бит), равными коэффициентам деления делителей. После того, как триггер 9 - 9f. вновь установлен в состояние О, пришедший сигнал со счетчиков 43j, снова переводит его в состояние 1 и, следовательно, соответствующий счетчик 10 установлен в состояние 1. Это означает, что в счетчике 10- зарегистрированы два искаженных блока; длиной п бит. Так как коэффициенты деления делителей выбират тся из условиях n. г f п, (например, п 10, п 30, .nj 100, П4 300, nj 1000 и т.д.), то числа искаженных блоков, накопленные в счетчиках 10 разные. Таким образом, за время сеансов (за время замкнутого состояния переключателя 6) в счетчиках 10, накапливается информация о числе (в двоич- нодёсятичном коде) искаженных блоков длиной п, п ... ч j, (числа . cj: ) соответственна. В счетчике 11 накапливается общее число ошибок . в сеансе J;. , а в счетчике 7 - число, определяющее длительность сеанса связи. Эти цифровые данные удерживаются в счетчиках весь второй этап. Вычисление текущих и окончательного значений коэффициента ошибок в канале осуществляется по формулам di rf к К --. К .t ) пш - 1 ) ., с -с Д ot - текущее значение числа ошибок в момент вычисления-, с/с - оищее число ошибок за сеанс связи; LC - текущее значение длины сеанса связи в момент вычисления; Uc - длина сеанса связи.

Вычисление значений , и К начинается после замыкания переключателя 6 режима работы и установления формирователя 34 в состояние 1. При этом второй датчик 37 консФанты управления подключается через второй дополнительньй переключатель 36 к первому дополнительному переключателю 20 и начинает работать генератор 13 уп-. равляющих импульсов, а управляющий триггер 1 переводится в состояние 1.

Действие устройства в режиме вычисления определяется работой регистра 31 сдвига. В начале процесса вычисления первый разряд 31 переходит в состояние 1. В дальнейшем эта 1 продвигается вдоль по регистру 31 сдвига, при этом в каждьй данньй момен только один разряд находится в состоянии 1. Продвижение 1 в регистре 31 производится под воздействием импульсоз, вырабатьшаемых генератором 13, Этот генератор на первом выходе выдает пачки импульсов, число которых в одной пачке равно числу десятичньк разрядов счетчиков 7, . 11.

На втором выходе генерируются одиночные импульсы, располагаювще- ся между пачками, 1 с выхода управляющего триггера 1 через первый элемент ИЛИ 2 поступает на вход регистра 31 Импульсом с второго вы-, хода генератора 13 управляющий гркг|гер 1 переводится в О. Этот же импульс, минуя элемент задержки 41,

через переключатель 40 и шестой эле мент ИЛИ 42 записьшает 1 в первый разряд регистра 31 сдвига.

Импульсы с первого выхода генератора 13 начинают постзтать в первый счетчик 17. Импульс с выхода первого разряда 31. поступает на счетный вход третьего счетчика 19 и через третий элемент ИЛИ 16 замыкает ключ 14.

Емкость первого счетчика 17 определяется числом десятичных разрядов принятым для счетчиков 7, Ю.и 11. Для примера примем, что в них установлено восемь разрядов. Тогда первый счетчик 17 должен быть выполнен в виде двоичного счетчика на три разряда (), Выход его в

этом случае выполнен в виде трех цепей - по одной от каждого разряда. Эти цепи соединены с управляющими 5 входами г +1 мультиплексоров 12 - 12 и дополнительного мультиплексора . . 44, с помощью которых устанавливается соединение одного из восьми разрядов каждого из счетчиков 7, 10 0 lOj, и 11 с выходами f + 1 мультипЛе1с С6ров 12 - 12 (состоящими из четырйс цепей), Последовательный выбор 1-го, 2-го, 3-го.,., 8-го разрядов для их пересылки в общий

5 мультиплексор 23 и далее и дешифратор 24 и блок 25 вычислений осуществляется изменением состояния первого счетчика 17 последовательно от 1 до 8, Для этого на его счетный вход необходимо подать последовательно восемь импульсов от генератора 13 через ключ 14, Общий мультиплексор 23 предназначен для соединения любой из входной групп цепей, каждая из

которых состоит из четырех цепей, с выходной группой, состоящей из четырех цепей, соединенной с входом дешифратора 24, Выбор группы осуществляется цепями управления общего

0 мультиплексора 23, сигналы для которых вырабатываются датчиком 21 (если первый дополнительньй переключатель 20 в прайом по чертежу положении) или вторым датчиком 37 константы

5 управления (если первый дополнительньй переключатель 20 - в левом положеш1и) , Если цепи управления общего мультиплексора 23 получают сигналы управления от датчика 21,

0 то мультиплексорами 12 - 12-f. и общими мультиплексорами 23 образуется цепь пересьтки сигналов от счет чиков 11 к дешифратору 24 и далее к блоку 25 вычислений. Если сигналы

5 управления поступают от второго

датчика 37, то образуется цепь пересыпки сигналов от счетчика 7,

Для пересылки информации со счет-гчиков 7 и 1 в мультиплексор 12

0 и дополнительньй мультиплексор 44 сигнал переноса для превого и второго промежуточных накопителей 35 и 35л формируется либо с первого разряда регистра 31 сдвига,

5 либо с третьего разряда этого

регистра 31, В рассматриваемьй момент (первьй разряд 31 в состоянии 1) первьй дополнительньй переключатель 20 находится в правом положании, первый счетчик 17 - в состоянии 1 Следовательно, с помощью мультиплексора общего мультиплексо ра 23 первый разряд счетчика 11 пересылается через дешифратор 24 в блок 25 вычислений. При поступлени второго импульса в первый счетчик 17 пересылается второй разряд счет чика 11 в блок 25 вычислений. Дале пересылаются последовательно остал ные разряды числа, хранящегося в счетчике 11. Это значит, что в память блока 25 вычислений введено число с(с . Так как цифры (0...9) в блок 25 вводятся по принципу провод - цифра, то предусмотрен де шифратор 24 для преобразования дво но-десятичного кода в десятичный. Кроме цифр в .блок 25 вычислений по отдельным цепям вводятся команды деление О,,), функция (F), логарифмирование С ij), память со сложением (ff-f), извлечение из памяти и равняется (Ш), запятая (,). (Перечисленные входные цепи блока 25 вычислений соответственно обоз чены на чертеже), В том случае, когда цифры или команды до.пжны вводиться от разных источников, предусмотрен блок 27 объединения сигналов. Число , введенное в память блока 25 вычислений, высвечивается на цифровом табло блока 26 индикации 1 до тех пор, пока 1 в регистре 31 сдвига не продвинется в следующий разряд. Это продвижение происходит с задержкой, так как сигнал с первого разряда 31д через пятьй элемент РШИ 38 устанав ливает на прямом выходе дополнительного управляющего триггера 39 сигнал 1, который переводит пере ключатель 40 в верхнее по чертежу положение. Следующий импульс с генератора 13 проходит по цепи через переключатель 40, элемент за держки И 41, шестой элемент ИЛИ 42 и появляется в цепи продвижения (н тактовом входе) регистра 31 с заде кой и записывает 1 во второй разряд регистра 31. Величина задержки элемента задержки 41 выбирается с учетом врем ни восприятия оператором измеряемого параметра с цифрового табло (несколько секунд). Дополнительный управляющий триггер 39 сигналом с выхода элемента задержки 41 устанавливается в исходное положение и переводит переключатель 40 в нижнее по чертежу положение. И далее продвижение 1 в регистре 31 происходит либо без задержки после второго разряда 31, либо с задержкой после третьего и четвертого разрядов 31 и 31. Импульсом с выхода второго разряда 312 размыкается, одновременно этим импульсом через блок 27 вводится команда i в блок 25 вычислений. Третьим импульсом в цепи продвижения регистра 31 состояние 1 принимает третий разряд 31j в результате этого ключ 14 замкнут и сигнал переноса поступает во второй промежуточньй накопитель 352 Первый дополнительный переключатель 20 переходит в левое положение, через него с выхода датчика 37 в общем мультиплексоре 23 образуется цепь переноса цифр из счетчика 7 в дещифратор:24 На вход первого счетчика 17 поступает из генератора 13 пачка импульсов и на выходах первого счетчика 17 последовательно образуются двоичные комбинации 1.2,3..., с помощью которых в мультиплексоре 121/по следовательно образуются цепи для переноса зна-; чений всех разрядов счетчика 7 через общий мультиплексор 23, дешифратор 24 в блок 25 вычислений. Таким образом в блок 25 вычислений вьщано первое текзтцее значение длины сеанса связи ( oi ) . Это значение высвечивается на цифровом табло блока 26 индикации до прихода след тощего -импульса на тактовом входе регистра 31, который приходит с задержкой, так как сигнал с выхода третьего разряда З через пятый элемент ИЛИ 38 устанавливает на прямом выходе дополнительного управляющего триггера 39 сигнал 1, который переводи переключатель 40 в верхнее по чертежу положение. Когда.1 появляется на выходе четвертого разряда ЗЦ, то ключ 14 размьжается,в блок 25 вычислений введена команда ИП, одновременно 1 переходит через переключатель 33 и перьый элемент ИЛИ 2 на вход регистра З, подготовив цепь для срабатьшания первого разряда 31 регистра 31. При этом результат деления значений d на d , т.е. первое текущее значение коэффициента ошибок высвечивается на цифровом табло в течение времени, равн.рм вре меня-задержки злемента задержки 41.

Следующим импульсом с второго вьосода генератора 13 переводится в 1 следующий разряд регистра 31 и начинается вычисление следуюп1его значения текущего коэффициента ошиЬок изложенным способом, отличающегося от первого коэффициента ошибок различными значениями чисел в счетчиках 7 и 11,

Аналогично после окончания сеанса связи подсчитывается окончательное значение коэффициента ошибок (Крщ), оно переведено в память блока 25 и это значение появляется на цифpoBQ- табло блока 28 индикации.

Начинается работа во втор6;м этапе.

На выходе счетчика 7 времени появляется импульс, которым переключатель 6 размыкается, а формирователь 34 переводится в состояние О, При этом по цепям установки четвертый разряд 31 регистра 31 сдвига устанавливается в О, а управляющий триггер 1 - в 1. Импульсом с инверсного выхода формирователя 34 второй дополнительный переключатель 36 устанавливается в левое по чертежу положение, а переключатель 33 - в верхнее.

Работу устройства в режиме вычисления показателя группирования целесообразно разбить на циклы:

1 ffi цикл - вычисление -/ /У /

1Д, ™

Wc/

11 -и цикл - вычисление ч 2

Ч( /с )

h-й цикл - вычисление а к

последний цикл - вычисление

()

где .oij ,.. , . - промежуточные

результаты вычис. ленияу

Г| , t/2 ,.., d(, - число блоков дли. ной п,, Oj ,... п бит с одной или

более ошибками ,

п , nj f Пр - число бит в блоках, на которые разбивается изме ряемая последовательность-,

г - число градаций значений длины блока п.

Блоками, которыми в основном определяется действие устройства во втором этапе, является регистр 31 сдвига, и дополнительный регистр 32 сдвига.

В 1-ом,..., г ом циклах г раз используются разряды регистра 31, а в последнем цикле однократно используются разряды дополнитепьного регистра 32.

Продвижение 1 в первых двух разрядах регистра 31, вычисление и индикация числа d , ввод в блок 25 вычислений команды J описано в первом этапе.

Третьим импульсом в цепи продвижения (на тактовом входе) регистра 31 состояние 1 принимает третий разряд 31з. В результате этого замкнут ключ 14. Первый дополнительный переключатель 20 переходит в

левое положение, через него с выхода третьего счетчика 19 цепями управления в общем мультиплексоре 23 образуется цепь для переноса цифр из счетчика 10 в дешифратор 24. На

вход первого счетчика 17 поступает из генератора 13 пачка импульсов, на выходах первого счетчика 17 последовательно образуются двоичные комбинации 1,2,3,..., с помощью которых в мультиплексоре 12 последовательно образуются цепи для переноса значений всех разрядов счетчика 10 - 10j4 через общий мультиплексор 23 и деимфратор 24 в блок 25 вычислений. Таким образом, в блок 25 вычислений введено число с/

Следук«1щм импульс ом в цепи продвижения регистра состояние 1 принимает червертый разряд 31. Ключ

14 размыкается в блок 25 вычислений введена команда ИП. Далее состояние 1 принимает пятый разряд 315, при этом в блок 25 введена команда F. Далее в состояние 1 переходит шестой разряд 31, в блок 25 введена команда Далее в состояние 1 переходит седьмой разряд 31, в блок 25 введена команда ;. Далее в состоянке 1 переходит восьмой разряд 31 Импульсом с его выхода приводится в действие блок 22 памяти, предназн ченный для формирования цифровых значений fg-n. Поскольку в рассматриваемом случае вычисляется л;,, блок 22 памяти выдает на своих выходах значений g-n . Если, например, п 10, блок 22 выдает импульс на выходе 1 (характеристика fcr 10, мантисса в данном случае равна нулю), Выбор одного из г значений логарифмов (констант) ,которые хранятся в блоке 2 памяти,осуществляется с выходов трет го счетчика 19 так же, как управляется общий мультиплексор 23, Число состояний общего мультиплексора 23 при управлении от третьего счетч ка 19 равно г J число состояний блока 22 памяти также равно ь После ввода в блок 25 вычисле1Ц й цифрового значения девятый разряд 313 регистра 31 переходит в состояние 1. Импульс с выхода де вятого разряда. 31 g поступает на ный вход второго счетчика 18 и пере водит его в состояние 1. Так как второй счетчик 18 имеет и инверсный выходы, которые соединены с входами первого и второго элементов И 29 к 30.соответственно, состояние этих выходов в данном случае не изменяется (оно изменяется тогда, когда второй счетчик 18 находится в состоянии Г ). Состояние 1 девятого разряда 31$ передается через второй элемент И 30 и первый элемент ШШ 2 на вход регистра 31. Подготавливается jjenb вторичного срабатывания первч)го раз ряда 31 регистра 31. Десятый разряд переходит в состояние 1 в блок 25 введена команда . Одиннадцатый разряд 31 переходит в состояние 1, в блок 25 введена команда F. Двенадцатый разряд переходит в состояние 1, в блок 25 введена команда п-е. Одновременно 1 переходит через агорой элемент И 30 и первый элемент ИЛИ 2 на вход регистра 31. Этим вновь подготовлена цепь для срабатывания , первого разряда 31 регистра 31. На этом заканчивается первый вычисления, в результате которого блоком 25 вычислений подсчитано значение oi , оно переведено в память блока 25 для использования в дальнейших вычислениях. Следующим импульсом с второго выхода генератора 13 переводится в 1 первый разряд 31. Начинается второй цикл вычисления, который отличается от первого цикла состоянием второго и третьего счетчиков 18 и 19. Третий счетчик 19 импульсом с выхода первого разряда 31 переведен в состояние 2, этим подготовлена возможность переноса информации (числа о/ ) со счетчика 10. (вместо 10 в первом цикле). Изменением состояния третьего счетчика 19 кроме того, подготовлено новое значение логарифма в блоке 22 . Второй счетчик 18 также переходит в состояние 2, но выход его остается без изменения. В остальном устройство во втором цикле работает так же, как в первом. В результате вычисления вычислено значение « () оно введено в память блока 25, где суммируется с о(., т.е. в памяти блока 25 хранится oC --oi . Аналогично в циклах 3,... г-ом вычислены р. и введены в память блока 22 суммированием. - с, . в t--oM гщкле второй счетчик 18 переходит в состояние г , на его прямом выходе появляется 1, а на инверсном - О. В результате при переходе в 1 двенадцатого разряда 31„ подготавливается цепь для работы первого разряда 32 , а не. первого разряда 31 как это было в 1,2,3..., г-1 циклах г-и цикл заканчивается. Аналогично первом этапу продвижение 1 в регистре 31 происходит либо без задержки, либо с задержкой после соответствующих разрядов 31, 31,|,, так как сигнал с выхода этих разрядов через пятьп элемент

| Устройство для измерения показателя группирования ошибок в дискретном канале связи | 1982 |

|

SU1016845A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-10-15—Публикация

1984-04-03—Подача