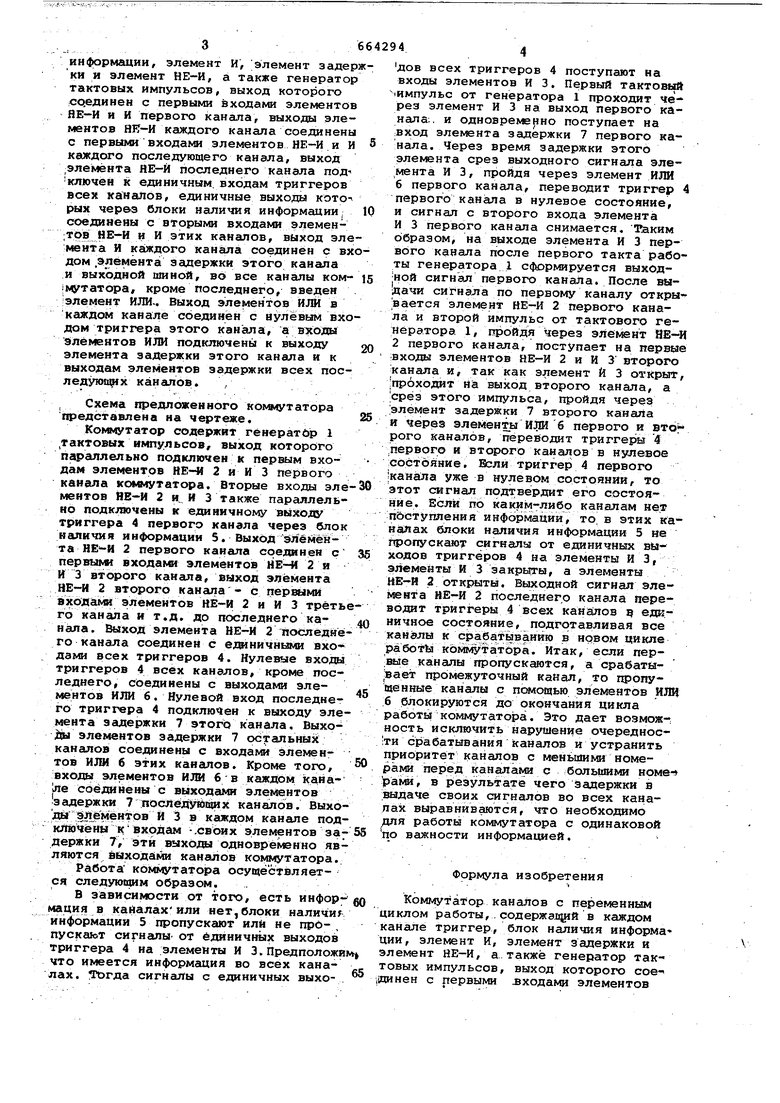

1. . . Изобретение касается импульсной техники и может быть использовано, например в устройствах передачи информации, адаптирующихся к скорости ее поступления. При передаче информа ции с помощью данного коммутатора формирование сигналов может производиться с испольэов51Нием кодового, ча тотного разделения сигналив зазЛичных каналов, а также посылкой по раз личным каналам импульсов разной формы. Передаваемая информация может быть дискретной или непрерывной. Такой коммутатор также может быть использован в многоканальных аналогоцифровых преобразователях .с адаптивной коммутацией каналов. Известен коммутатор, выполняющий подобные функции и использующий коль цевой принцип работы, т.е. коммутатор последовательно опрашиваёт кайалы и на том канале, по которому поступает информация, останавливается, прерывая цикл, этот коммутатор содер жит логические элементы и триггеры 1 однако в, этом коммутаторе имеется потеря информации по другим каналам в то время,-когда коммутатор стоит. выдавая информацию по одному из них. Известен также коммутатор каналов с переменным .циклом работы, содержащий в каждом канале триггер, блок наличия информации, элемент И, элемент задержки и элемент НЕ-И, а также генератор тактовых импульсов, выход которого соединен с первыми входами элементов НЕ-И и И первого канала, выходы эле 1ентов НЕ-Й каждого канала соединены с первыми входами эле- ментов НЕ-И и И каждого последующего канала, выход элемента Нб-И последнего канала подключен к единичным входам.триггеров всех каналов, единичные выходы которых через блокиналичия информации соединены с вторыми входами элементов НЕ-И и и э.тих ка:налов. Выход элемента И каждого калала соединен с входом элемента зацержки этого каналаи выходной шиной 2. Однако в этом кo Ф yтaтope предыдущие каналы обладаю- приоритетом в выдаче своих сигналов последующими каналами, т.,е. быстродействие каналов коммутатора разное. Цель изобретения - выравнивание быстродействия каналов. Для этого в коммутатор каналов с переменным циклом работы, Содержащий в каждом канале триггер, блок наличия информации, элемент И, элемент эадер ки и элемент НЕ-И, а также генератор тактовых импульсов, выход которого :Со.единен с первыми входами элементов НЕ-И и И первого канала, выходы элементов НЕ-И каждого канала соединены с первыми входами элементов НЕ-И и И каждого последующего канала, выход элемента НЕ-И последнего канала поД ключей к единичным, входам триггеров всех каналов, единичные выходы кото рык через блоки наличия информации; соединены с вторыми входами элемен;Трв НБ-И и И этих каналов, выход эле кюнта И каждого кан&ла соединён с вх дом .элемента задержки этого канала и выходной шиной, во все каналы ком|мутатора, кроме последнего, введем элемент ИЛИ-. Выход элементов HJffl в каждом канале соединён с нулевым вхо дом триггера этого канала, а входы Элементов ИЛИ подключены к выходу элемента задержки этого канала и к выходам элементов задержки всех последуюо х каналов. , Схема предложенного кок 1утатора представлена на чертеже. Ком татор содержит гёнератдр 1 ,тактовых импульсов, выход которого пгфаллельно подключен к первым входам элементов НЕ-4 2 и И 3 первого канала ко в |утатора. Вторые входы эле ментов НЕ-И 2 и, И 3 также параллельно подключены к единичному выход/ триггера 4 первого канала через блок наличия информации 5. Выход элемента НЕ-И 2 первого канала соедкиен с первыми входами элементов НЕ- 2 и И 3 второго канала, выход элемента НЕ-Я 2 второго канала - с первыми входами элементов НЕ-И 2 и И 3 треть го канала и т.д. до последнего канала. Выход элемента НЕ-И 2 тюслёдйё го канала соединен с единичными входами всех триггеров 4. Нулевые входы триггеров 4 всех каналов, кроме последнего, соединены с выходами элементов ИЛИ 6. Нулевой вход последнего триггера 4 подключен к выходу эле мента задержки 7 этого канала. Выхо; элементов задержки 7 остальных каналов соединены с входами элементов ида б этих каналов. Кроме того, вход:ол элементов 1ЛШ 6 в каждом канаLrte соёданены с выходами элe eнтoв задержки 7 :послёдУйщих каналов. Выхо да Щёментов И 3 в каждом канапе под кШочёны к входам .своих элементов за держки 7, эти выходы одновременно яв ляются выходами каналов комк гтатора. Работа коммутатора осуществляется следуювчим образом. В зависимости от того, есть инфор мация Bi кайалахили нет, блоки наличи; информации 5 пропускают или не про-, nycKaioT сигналыот единичных выходов триггера 4 на элементы И 3.Предполож что имеется информгщия во всех каналах. Тогда сигналы с единичных выхо44дов всех триггеров 4 поступают на входы элементов И 3. Первый тактовый 1импульс от генератора 1 проходит через элемент И 3 на выход первого канала;, и одновременно поступает на :Вход элемента задержки 7 первого канала. Через время задержки этого элекюнта срез выходного сигнала эле мента ИЗ, пройдя через элемент ИЛИ 6 первого канала, переводит триггер 4 первого канала в нулевое состояние, и сигнал с второго входа элемента И 3 первого канала снимается. Таким образом, на выходе элемента И 3 первого канала после первого такта работы генератора 1 сформируется выходной сигнал первого канала. После выдачи сигнала по первому каналу открЫ :вается элемент НЕ-И 2 первого канала и второй импульс от тактового генератора 1, пройдя через эле-мент НЕ-И 2 первого канала, поступает на первые ;входы элементов НЕ-И 2 и И 3 второго канала и, так как элемент И 3 открыт, проходит На выход второго канала, а ;Срёз этого импульса, пройдя через элемент задержки 7 второго канала и через элементы ИЛИ б первого и это рого каналов, перейодит триггеры 4 первого И второго каналов в нулевое сОстбяние. Если триггер 4 первого |канала уже в нулевом состоянии, то этот сигнал подтвердит его состояние. Если по каким-либо каналам пет пЬступления информации, то в этих каналах блоки наличия информации 5 не пропускают сигналы от единичных выходов триггеров 4 на элементы ИЗ, эл еМенты И 3 закрыты, а элементы НЕ-й 2 открыты. Выходной сигнал элемента НЕ-И 2 последнего канала аеревОдит триггеры 4 всех каналов в единичное состояние, подготавливая все каналы к срабатыванию в новом цикле работу колйлутатора. Итак, если первые каналы пропускаются, а срабаты|вает промежуточный канал, то пропущенные каналы с помощью элементов ИЛИ 6 блокируются до сэкончания цикла работы коммутатора. Это дает возмож-: ность исклю чить нарушение очередности срабатывания каналов и устранить приоритет каналов с меньшими номерами перед каналами с большими номе- pavK, в результате чего задержки в выдаче своих сигналов во всех каналах выравниваются, что необходимо для работы коммутатора с одинаковой по важности информахшей. Формула изобретения .ч Коммутатор каналов с переменным циклом работы, . содержадц й в каждом канале триггер, блок наличия информации, элемент И, элемент задержки и элемент НЕ-И, а также генератор тактовых импульсов, выход которого сое-ч |динен с первыми входами элементов

,НЕ-И и И первого канала, выходы элементов НЕ-И каждого канала соединены с первыми входаки элементов НБ-И и И каждого последующего канала, выход элементов НЕ-И последнего канала подключен к единичным.входам триггеров всех каналов, единичные выходы которых через блоки наличия информации соединены с вторыми входамиэлементов НЕ-И и И этих каналов, выход элементов И каждого канала соединен с входом элемента задержки этого канала и выходной шиной,, отличаю;щ и и с я тем, что, с целью выравнивания стродействия каналов, во

,все каналы коммутатора, кроью последнего, введен элемент ИЛИ, выход элемента ИЛИ в каждом канале соединен с нулевым входом триггера этого канала, а входы элементов ИЛИ подключены к выходу элемента задержки этого канала и к выходам элементов задержки всех последующих каналов.

Источники информации, принятые во внимание при экспертизе

1.Патент Франции 2206641, кл. Н 03 К 17/00, 1972,

2.Авторское свидетельство СССР № 466618, кл. Н 03 К 17/04, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор каналов | 1982 |

|

SU1045389A1 |

| Коммутатор | 1981 |

|

SU978342A1 |

| Коммутатор каналов с переменным циклом работы | 1982 |

|

SU1070690A1 |

| Коммутатор каналов с переменным циклом работы | 1978 |

|

SU741464A1 |

| Коммутатор | 1981 |

|

SU1001470A1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1310838A1 |

| Устройство для моделирования передачи сообщений | 1986 |

|

SU1397931A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

Авторы

Даты

1979-05-25—Публикация

1977-06-14—Подача