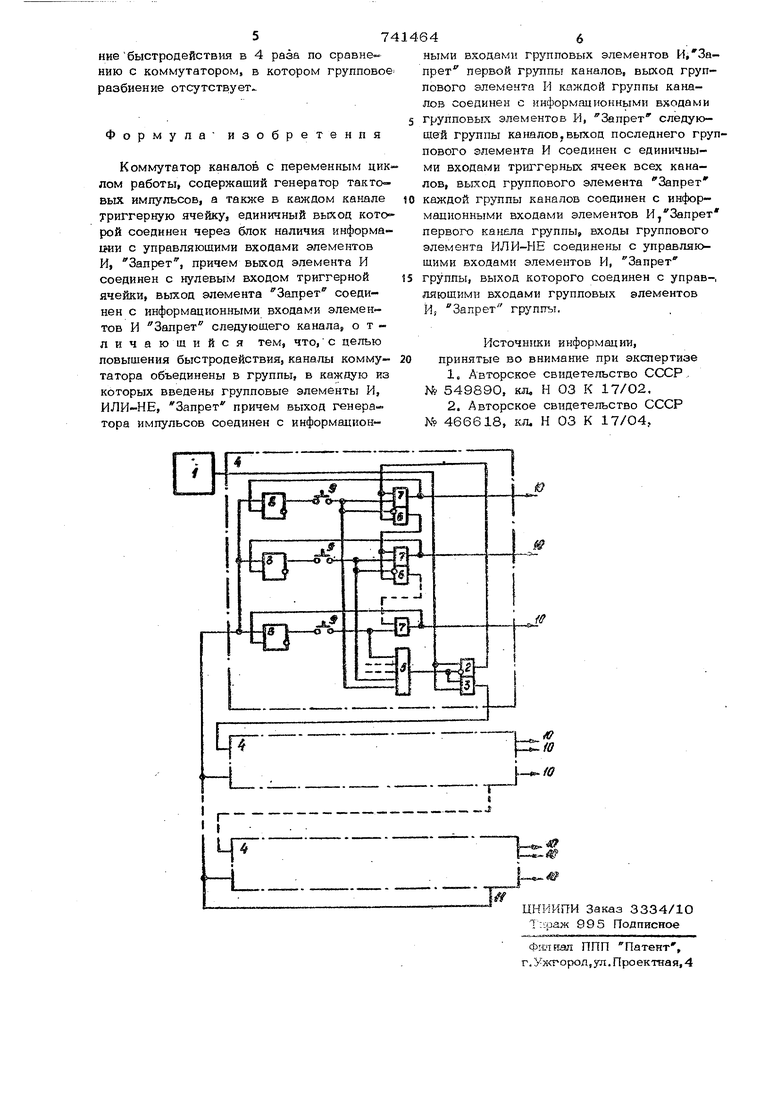

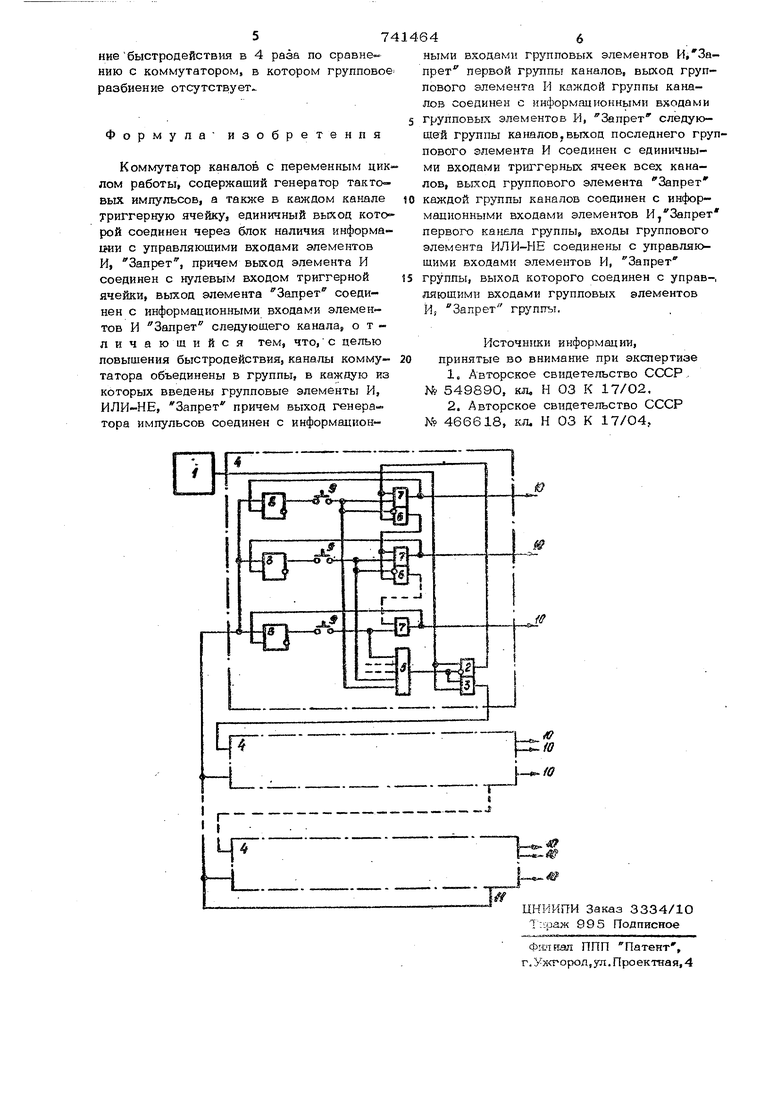

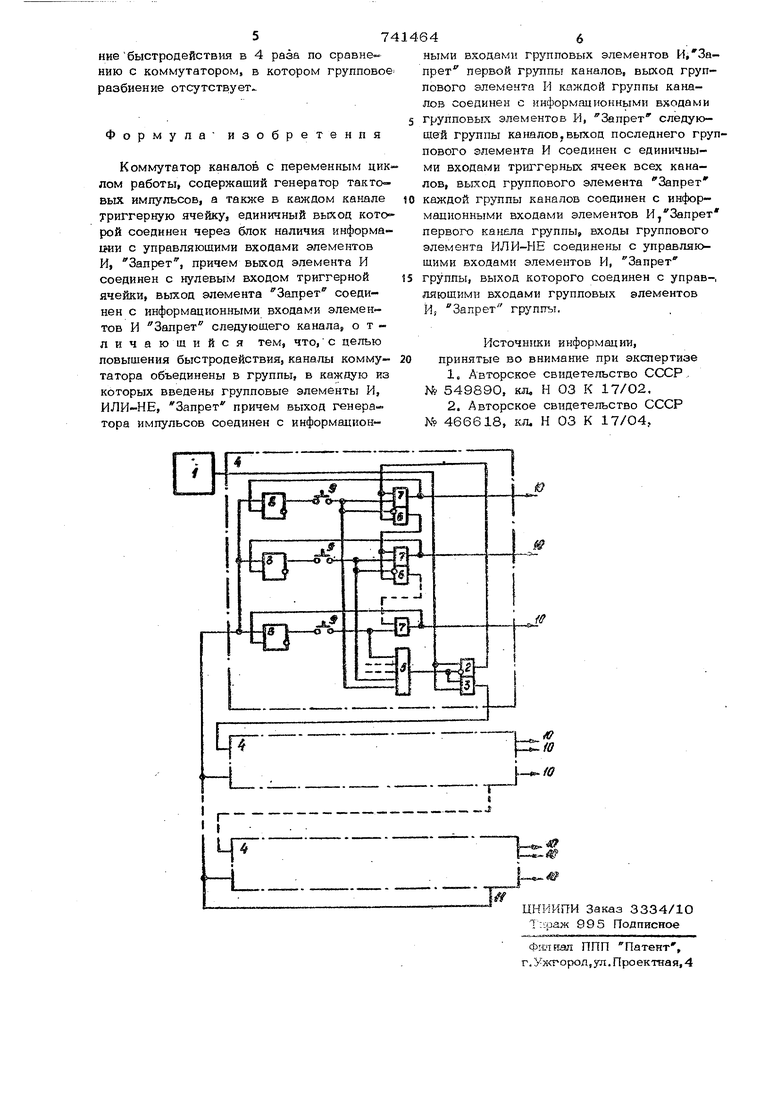

Изобретение относится к импульсной технике и может быть использовано в ком мутаторах информационных каналов, работающих с переменными скоростями. Известен коммутатор каналов с переменными циклом работы, длительность цикла которого пропорциональна числу каналов, по которому в данный момент имеется информация. Коммутатор состоит из генератора тактовьк импульсов, объектных триггеров кольцевого коммутатора, элеме тов И, Запрет и элементов задержки. Число объектных триггеров равно числу каналов . Недостатком коммутатора является его ограниченное быстродействие, обусловленное тем, что период следования тактовых (опросных) импульсов прямо пропорционален числу каналов. Известен также коммутатор с перемен ным циклом работы, содержащий генератор тактовых импульсов, а также в каждом канале триггерпую ячейку, единичный выход которой соединен через блок наличия информации с управляющими входами элементов И, Запрет, причем выход элемента И соединен с нулевым входом триггерной ячейки, выход элемента Запрет соединен с информационными входами элементов И, Запрет следующего канала 2., Цель изобретения - повышение быстродействия устройства. Цель достигается тем, что каналы коммутатора соединены в группы, в каждую из которых введены групповые элементы И, ИЛИ-НЕ, Запрет, причем выход генератора импульсов соединен с информационными входами групповых элементов И, Запрет первой группы каналов, выход группового элемента И каждой группы каналов соединен с информационными входами групповых элементов И, Запрет, следующей группы каналов, выход последнего группового элемента И соединен с единичными входами триггерных ячеек всех каналов, выход группового элемента Запрет каждой группы каналов соединен с информационными входами элементов И, первого канала группы, входы группового элемента соединены с управляющими входами элементов И, Запрет груп пы, выход которого соединен с управляющими входами групповых элементов И, За прет группы. На чертеже представлена схема устройства. Устройство содержит генератор 1 тактовых импульсов (ГТИ), выход которого подключен к информационным входам групповых элементов 2 Запрет и 3 И первой группы каналов 4 коммутатора. Управляющие входы элементов 2 и 3 подключены к выходу группового элемента -5 ИЛИ-НЕ первой группы каналов 4 коммутатора, Выход элемента 2 первой группы каналов 4 пошслючен ко входам элементов 6 Запрет и 7 И первого канала коммутатора. Другие входы элементов 6 и 7 первого канала подключены к первому входу элемента 5 первой группы каналов 4 и к единичному выходу триггера 8 первого канала через блок наличия информации 9, Выход элемента 7 первого капала подключен к первому входу 10 кодирующего устройства и к нулевому входу триггера 8 первого канала кольцевого коммутатора. Выход элемента 6 первого канала подключен ко входам элементов. 6 и 7 второго канала и т.д. Выход 11 последней группы каналов 4 соединен с единичными входами всех триггеров 8 кольцевого коммутатора. Отдельные блоки схемы работают следующим образом. ГТИ 1 выдает импульсы, частота которых определяет быстродействие коммутатора .Элемент 2 пропускает импульсы ГТИ 1 на входы элементов 6 и 7 первого канала первой группы, если в этой группе имеется информация хотя бы по одному каналу. Элемент 3 про пускает импульсы с ГТИ 1 на свой выход только в том случае, если в первой группе каналов отсутствует информация по всем каналам, либо все каналы опрошены, при этом элемент 2 запрещает прохождение импульсов с ГТИ 1 на свой выход Элемент 5 формирует запрещающий потенциал на вход хлемента 3 и разрещающий потенциал на вход элемента 2 в случае, когда в первой группе каналов хотя бы п одному каналу имеется информация, в про тивном случае запрещающий потенциал с выхода элемента 5 поступает на вход эле мента 2, а разрешающий потенциал на вх элемента 3. Таким образом организуется цепь прохождения импульсов с ГТИ 1 меж ДУ группами каналов. Элемент 6 пропускает на свой выход импульсы, поступивщие на ее вход, только в том случае, ес- ли нет сигнала с блока 9 налиЧ1ш информации. Элемент 7 пропускает на свой выход импульсы с ГТИ 1 в случае, если информация поступает Сигнал единичного выхода триггера 8 подается на вход блока наличия информации. Перед началом каждого цикла все триггеры 8 приводятся в состояние единица. Блок 9 наличия информации пропускает сигнал с единичного вькода триггера на входы элементов 6 и 7 только в том случае, когда по данному каналу есть информация. В простейшем случае это какой-либо контакт, например кнопка укрепления. В схеме применена заднефронтовая логика, т.е. триггер 8 сбрасывается в О . задним фронтом им- пульса с ГТИ 1, тем самым на входе 10 кодирующего устройства удерживается соответствующий код канала в течение всего действия импульса. Для получения максимального быстро- действия коммутатора (-максимальной частоты генератора тактовьк импульсов)п ка1тлов необходимо определить число групп каналов, на которое разбивается коммутатор и количество каналов в отдельных группах. Если число каналов в группах одинаково, то ш где Т длительность тактового импульcajсуммарное число каналов коммутатора;число каналов в группе| задержка элементов 2, 3 И, 6, 7 И. Первое слагаемое в формуле для Т соответствует задержке тактирующего импульса на по элементах 6, а второе на п /т элементах 3 И, соответствующих чисду групп каналов. Определив минимальное значение Т по переменной, оптималЬ .ное значение числа каналов в группе m-Vn Тогда t:( гтгЧп. В известном устройстве величина Т-Т П 2rVn 2 т. 8, Н-- 4. f П-64 каналам. имеет место повыще- этом случае

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор с переменным циклом работы | 1986 |

|

SU1338046A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1310838A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для моделирования систем передачи и обработки информации | 1987 |

|

SU1481791A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

| Матричный коммутатор | 1991 |

|

SU1800605A1 |

Авторы

Даты

1980-06-15—Публикация

1978-01-02—Подача