каждый единичный и нулевой выходы группы выходов регистра тестов соединены соответственно с вторыми входами первого и второго элементов равнозначности соответствующего канала блока анализа, выход третьего элемента равнозначности каждого канала

блока анализа соединен с соответствующим входом второго блока индикации и с соответствующим входом элемента ИЛИ, выход которого соединен с вторым входом установки нуйя триггера блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Система централизованного контроля радиоэлектронных изделий | 1978 |

|

SU744481A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЬК БЛОКОВ, содержащее коммутатор, блок памяти, регистр тестов, регистр управления коммутатором, первый блок индикации и блок управления, который содержит триггер, генератор тактовых импульсов, счетчик адресов и первый элемент И, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен с входом счетчика адресов, вход Пуск устройства соединен с единичным входом триггера, единичньй выход которого соединен с вторым входом первого элемента И, выходы счетчика адресов соединены с адресными входами блока памяти, информационные выходы которого соединены с информационными входами регистра тестов и регистра управления коммутатором, информационные выходы регистра управления коммутатором соединены с группой управляющих входов коммутатора, группа единичных выходов регистра тестов соединена с первой группой информадионных входов коммутатора, вторая группа информационных входов коммутатора является группой входов устройства, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введен элемент ИЛИ, второй блок индикации, п-канальный блок анализа (где п- число контактов контролируемого блока), a в блок управления введен элемент задержки, второй, третий и четвертый элементы И и элемент НЕ, причем выход первого элег мента И через элемент задержки соедиСП нен с первыми входами второго и третьего элементов И, выходы которых соединены с входами записи соответственно регистра тестов и регистра управления .коммутатором, информационные выходы счетчика адресов соединены с входами четвертого элемента И, выход которого соединен с вторым входом 00 О) третьего элемента И и через элемент НЕ соединен с вторым входом второго эле4 оо оо мента И, каждый канал блока анализа содержит первый, второй и третий элементы равнозначности, причем каждый вьосод коммутатора соединен с первыми входами первого и второго элементов равнозначности соответствующего канала блока анализа, выходы первого и второго элементов равнозначности каждого канала блока анализа соединены с входами третьего элемента равнозначности и с соответствующими входами первого блока индикации, выход которого соединен с первым входом установки нуля триггера блока управления,

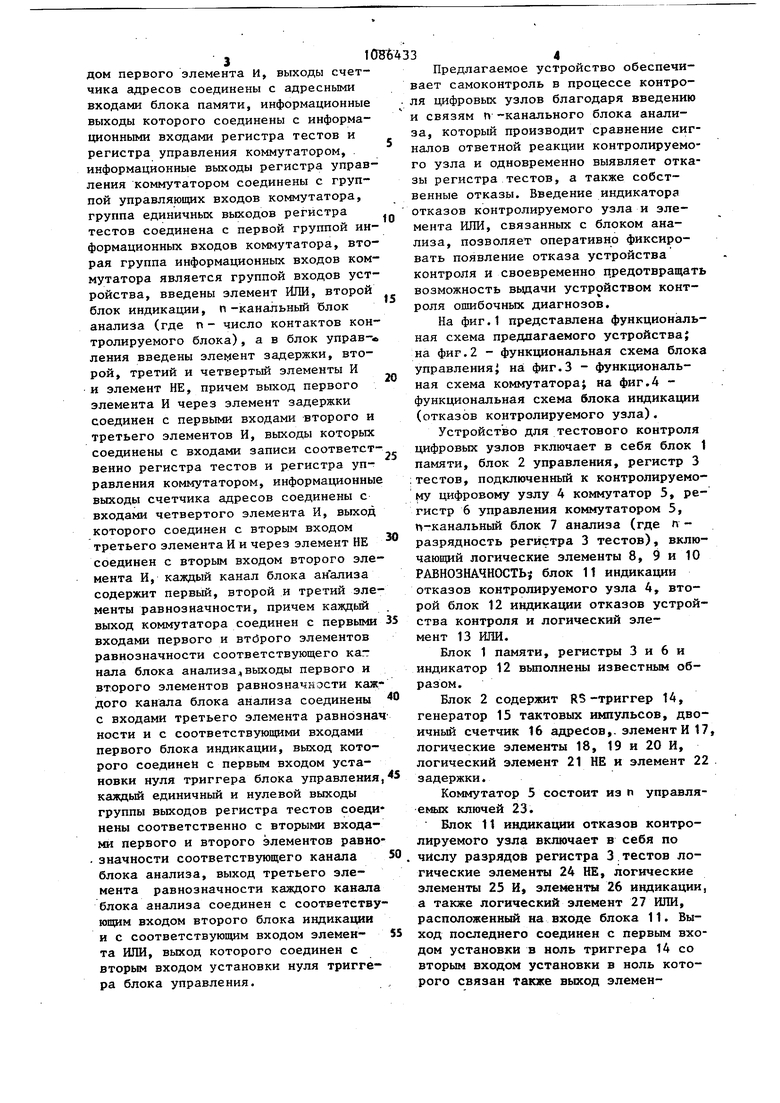

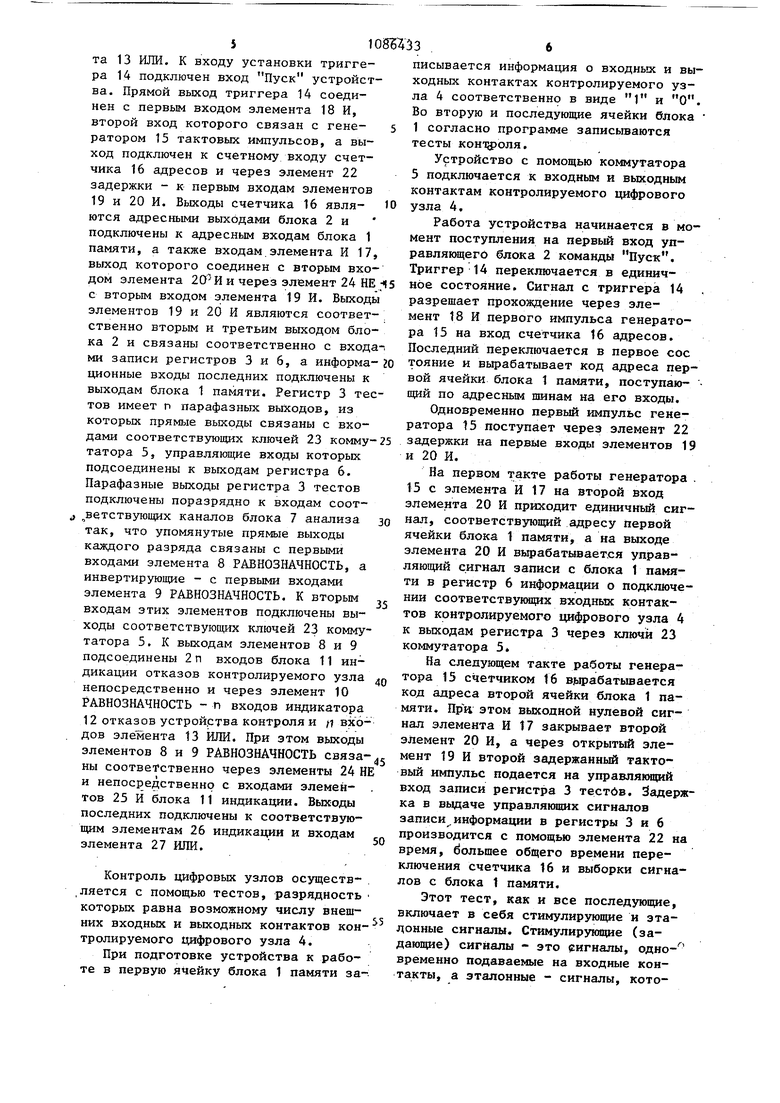

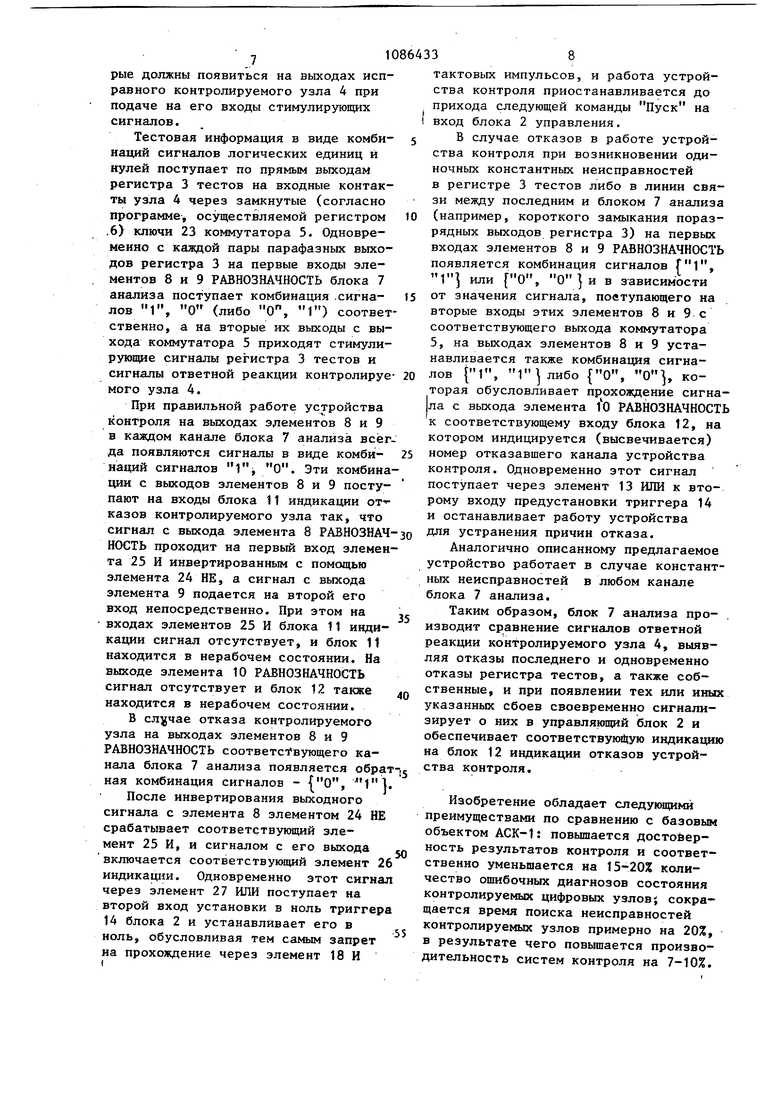

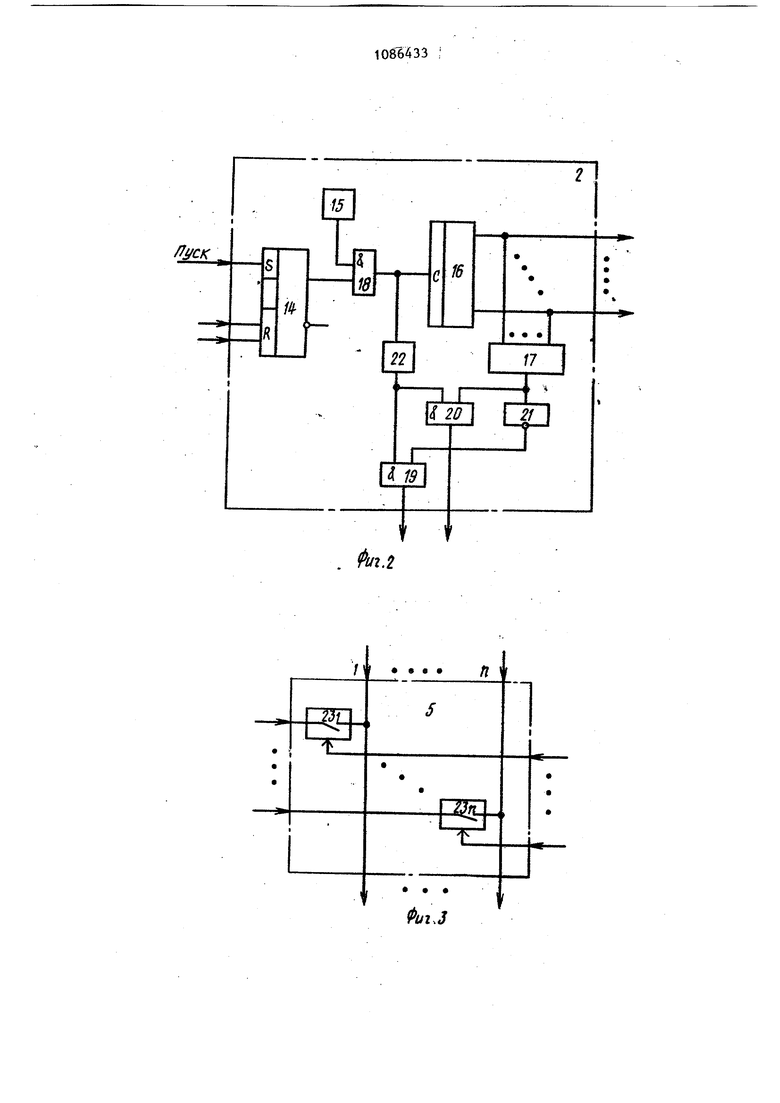

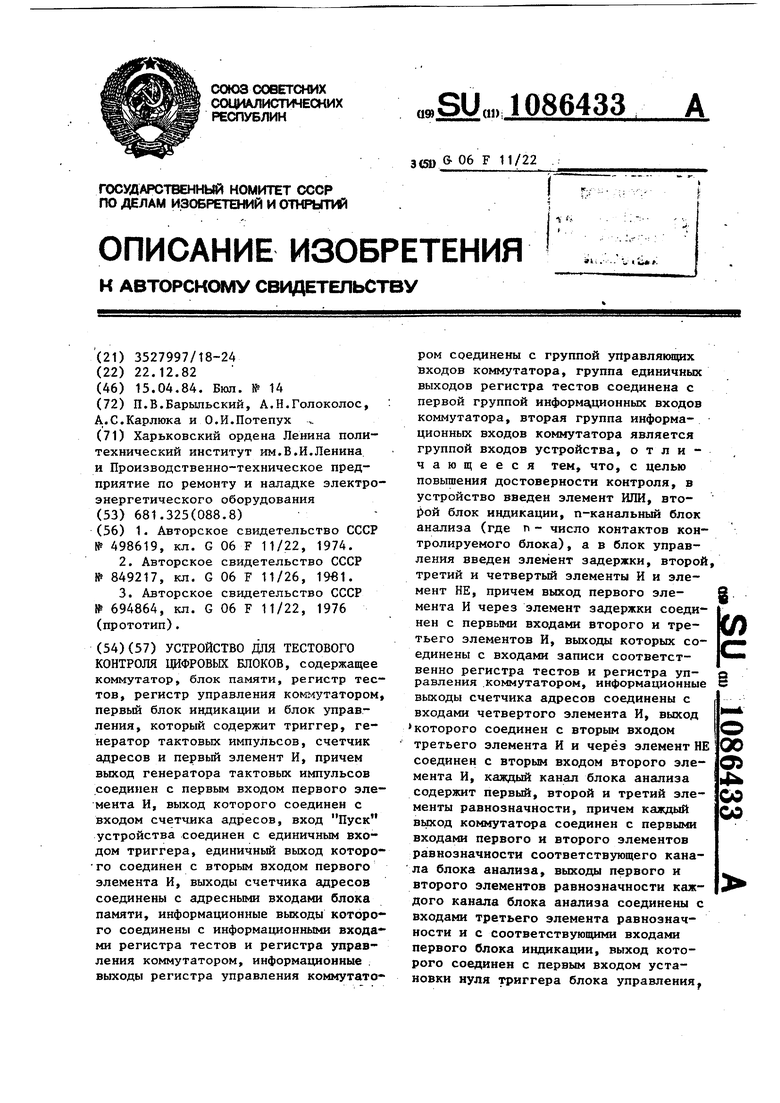

Изобретение относится к электронной контрольно-измерительной технике в частности к средствам контроля функционирования и диагностики неисп равностей цифровых узлов вычислитель ной техники и автоматики в процессе их производства, нападки и технического обслуживания. Известно устройство для контроля цифровых узлов, содержащее блок памя ти, блок коммутации, блок сравнения и блок индикации. Контроль цифровых узлов осуществляется при помощи тестов, представляющих собой совокупйость сигналов, подаваемых на входы проверяемого узла, и эталонных сигна лов для сравнения с ответной реакцией контролируемого цифрового узла{ 1% Это устройство не обладает достаточной достоверностью результатов контроля, так как в случае отказов в самом устройстве контроля возможна ошибочная индикация отказов контроли руемого узла. Известно тавже устройство для кон троля цифровых узлов, содержащее бло ввода, регистр задания, блок сравнения, блок управления, блок индикации регистр маски с парафазными выходами и коммутатор 23 Такое устройство обеспечивает самоконтроль, однако он цроизводится только в промежутках меаду циклами контроля, а в процессе контроля возможные отказы в работе блока сравнения и других блоков устройства обусловливают ошибочные результаты контроля цифровых узлов. Наиболее близким к предлагаемому по технической сущности и достигаемому эффекту является устройство для тестового контроля цифровых узлов электронных вычислительных машин, со держащее блок памяти, связанньй с ним своими входами блок записи, регистр тестов, блок индикации отказов контролируемого узла, расположенный на ; входе устройства коммутатор, регистр управления коммутатором, соединенный парафазными выходами с управляющими входами коммутатора, информационные входы которого связаны с выходами регистра тестов, подключенными также к регистру .управления коммутатором. Входы регистра Тестов поразрядно соединены с выходами блока записи Сз J. Однако такое устройство не позволяет получать результаты контроля с необходимой достоверностью, так как из-за отсутствия самоконтроля устройства при отказах блока сравнения или регистра тестов будет иметь место ложное срабатывание устройства.в процессе контроля цифрового узла, которое невозможно зафиксировать для ; предотвращения выдачи устройством контроля ошибочных диагнозов. Целью изобретения является повышение достоверности результатов контроля цифровых.узлов. Поставленная цель достигается тем, что в устройство для тестового контроля цифровых блоков, содержащее коммутатор, блок памяти, регистр тестов, регистр управления коммутатором, первый блок индикации и блок управления, который содержит триггер, генератор тактовых импульсов, счетчик адресов и первый элемент И, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика адресов, вход Пуск устройства /соединен с единичным входом триггера, единичный выход которого соединен с вторым вхо3Юдом первого элемента И, выходы счетчика адресов соединены с адресными входами блока памяти, информационные выходы которого соединены с информационными входами регистра тестов и регистра управления коммутатором, . информационные выходы регистра управления коммутатором соединены с группой управляющих входов коммутатора, группа единичных выходов регистра тестов соединена с первой группой информационных входов коммутатора, вторая группа информационных входов коммутатора является группой входов устройства, введены элемент ИЛИ, второй блок индикации, п-канальный блок анализа (где п- число контактов контролируемого блока), а в блок управ- ления введены элемент задержки, второй, третий и четвертый элементы И и элемент НЕ, причем выход первого элемента И через элемент задержки соединен с первыми входами второго и третьего элементов И, выходы которых соединены с входами записи соответственно регистра тестов и регистра управления коммутатором, информационные выходы счетчика адресов соединены с входами четвертого элемента И, выход которого соединен с вторым входом третьего элемента И и через элемент НЕ соединен с вторым входом второго эле мента И, каждый канал блока анализа содержит первый, второй и третий элементы равнозначности, причем каждый выход коммутатора соединен с первыми входами первого и втброго элементов равнозначности соответствующего канала блока анализа выходы первого и второго элементов равнозначности каж дого канала блока анализа соединены с входами третьего элемента равнознач ности и с соответствующими входами первого блока индикации, выход которого соединен с первым входом установки нуля триггера блока управления каждьй единичный и нулевой выходы группы выходов регистра тестов соеди нены соответственно с вторыми входами первого и второго элементов равно . значности соответствующего канала блока анализа, выход третьего элемента равнозначности каждого канала блока анализа соединен с соответству ющим входом второго блока индикации и с соответствующим входом элемента ИЛИ, выход которого соединен с вторым входом установки нуля триггера блока управления. З Предлагаемое устройство обеспечивает самоконтроль в процессе контроля цифровых узлов благодаря введению и связям п -канального блока анализа, который производит сравнение сигналов ответной реакции контролируемого узла и одновременно выявляет отказы регистра тестов, а также собственные отказы. Введение индикатора отказов контролируемого узла и элемента ИЛИ, связанных с блоком анализа, позволяет оперативно фиксировать появление отказа устройства контроля и своевременно цредотвращать возможность вьщачи устройством контроля ошибочных диагнозов. На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока управленияi на фиг.З - функциональная схема коммутатора; на фиг.4 функциональная схема блока индикации (отказов контролируемого узла). Устройство для тестового контроля цифровых узлов рключает в себя блок 1 памяти, блок 2 управления, регистр 3 тестов, подключенный к контролируемоНУ цифровому узлу 4 коммутатор 5, регистр 6 управления коммутатором 5, г -канапьный блок 7 анализа (где п разрядность регистра 3 тестов), включающий логические элементы 8, 9 и 10 РАВНОЗНАЧНОСТЬ блок 11 индикации отказов контролируемого узла 4, второй блок 12 индикации отказов устройства контроля и логический элемент 13 ИЛИ. Блок 1 памяти, регистры 3 и 6 и 12 вьшолиены известным обиндикаторразом. Блок 2 содержит R5-триггер 14, генератор 15 тактовых импульсов, двоичный счетчик 16 адресов,-элемент И 17, логические элементы 18, 19 и 20 И, логический элемент 21 НЕ и элемент 22 задержки. Коммутатор 5 состоит из п управляемых ключей 23. Блок 11 индикации отказов контролируемого узла включает в себя по числу разрядов регистра 3 тестов логические элементы 24 НЕ, логические элементы 25 И, элементы 26 индикации, а также логический элемент 27 ИЛИ, расположенный на входе блока 11. Выход последнего соединен с первым входом установки в ноль триггера 14 со вторым входом установки в ноль которого связан также выход элемента 13 ИЛИ. К входу установки триггера 14 подключен вход Пуск устройства. Прямой выход триггера 14 соединен с первым входом элемента 18 И, второй вход которого связан с генератором 15 тактовых импульсов, а выход подключен к счетному входу счетчика 16 адресов и через элемент 22 задержки - к первым входам элементов 19 и 20 И. Выходы счетчика 16 являются адресными выходами блока 2 и подключены к адресным входам блока 1 памяти, а также входам.элемента И 17, выход которого соединен с вторым входом элемента 20И и через эл1емент 24 НЕ с вторым входом элемента 19 И. Выходы элементов 19 и 20 И являются соответственно вторым и третьим выходом блока 2 и связаны соответственно с входа ми записи регистров 3 и 6, а информационные входы последних подключены к выходам блока 1 памяти. Регистр 3 тес тов имеет п парафазных выходов, из которых прямые выходы связаны с входами соответствующих ключей 23 коммутатора 5, управляющие входы которых подсоединены к выходам регистра 6. Парафазные вьгходы регистра 3 тестов подключены поразрядно к входам соот ветствующих каналов блока 7 анализа так, что упомянутые прямые выходы каждого разряда связаны с первыми входами элемента 8 РАВНОЗНАЧНОСТЬ, а инвертирующие - с первыми входами элемента 9 РАВНОЗНАЧНОСТЬ. К вторым входам этих элементов подключены выходы соответствующих ключей 23 коммутатора 5. К выходам элементов 8 и 9 подсоединены 2 п входов блока 11 индикации отказов контролируемого узла непосредственно и через элемент 10 РАВНОЗНАЧНОСТЬ - п входов индикатора 12 отказов устройства контроля и п входов элемента 13 ИЛИ. При этом выходы элементов 8 и 9 РАВНОЗНАЧНОСТЬ связаны соответственно через элементы 24 Н и непосредственно с входами элементов 25 И блока 11 индикации. Вьгходы последних подключены к соответствующим элементам 26 индикаций и входам элемента 27 ИЛИ. Контроль цифровых узлов осуществляется с помощью тестов, разрядность которых равна возможному числу внешних входных и выходных контактов контролируемого 1щфрового узла 4. При подготовке устройства к работе в первую ячейку блока 1 памяти записывается информация о входных и выходных контактах контролируемого узла 4 соответственно в виде 1 и О. Во вторую и последующие ячейки блока 1 согласно программе записьшаются тесты контроля, Устройство с помощью коммутатора 5 подключается к входным и выходным контактам контролируемого цифрового узла 4, Работа устройства начинается в момент поступления на первый вход управляющего блока 2 команды Пуск. Триггер 14 переключается в единичное состояние. Сигнал с триггера 14 разрешает прохождение через элемент 18 И первого импульса генератора 15 на вход счетчика 16 адресов. Последний переключается в первое сое тояние и вырабатывает код адреса первой ячейки блока 1 памяти, поступаю- щий по адресным пшнам на его входы. Одновременно первый импульс генератора t5 поступает через элемент 22 задержки на первые входы элементов 19 и 20 и. На первом такте работы генератора . 15 с элемента И 17 на второй вход элемента 20 И приходит единичный сигнал, соответствующий адресу первой ячейки блока 1 памяти, а на выходе элемента 20 И вырабатывается управляющий сигнал записи с блока 1 памяти в регистр 6 информации о подключении соответствуищих входных контактов контролируемого цифрового узла 4 к выходам регистра 3 через ключи 23 коммутатора 5 На следующем такте работы генератора 15 счетчиком 16 вьфабатьшается код адреса второй ячейки блока 1 памяти. этом выходной нулевой сигнал элемента И 17 закрывает второй элемент 20 И, а через открытый элемент 19 И второй задержанный тактовый импульс подается на управляющий вход записи регистра 3 тестов. Задержка в выдаче управляющих сигналов записи.информации в регистры 3 и 6 производится с помощью элемента 22 на время, большее общего времени переключения счетчика 16 и выборки сигналов с блока 1 памяти. Этот тест, как и все последующие, включает в себя стимулирующие и зтадонные сигналы. Стимулирующие (задающие) сигналы - это ригналы, одновременно подаваемые на входные контакты, а эталонные - сигналы, которые должны появиться на выходах исправного контролируемого узла 4 при подаче на его входы стимулирующих сигналов. Тестовая информация в виде комбинаций сигналов логических единиц и нулей поступает по прямым выходам регистра 3 тестов на входные контакты узла 4 через замкнутые (согласно программе, осуществляемой регистром .6) ключи 23 коммутатора 5. Одновременно с каждой пары парафазных выходов регистра 3 на первые входы элементов 8 и 9 РАВНОЗНАЧНОСТЬ блока 7 анализа поступает комбинация .сигналов 1, О (либо О, 1) соответ ственно, а на вторые их выходы с выхода коммутатора 5 приходят стимулирующие сигналы регистра 3 тестов и сигналы ответной реакции контролируе мого узла 4. При правильной работе устройства контроля на выходах элементов 8 и 9 в каждом канале блока 7 анализа всег да появляются сигналы в виде комбинаций сигналов 1 О. Эти комбина ции с выходов элементов 8 и 9 поступают на входы блока 11 индикации отказов контролируемого узла так, что сигнал с выхода элемента 8 РАВНОЗНАЧ НОСТЬ проходит на первый вход элемен та 25 И инвертированным с помощью элемента 24 НЕ, а сигнал с выхода элемента 9 подается на второй его вход непосредственно. При этом на входах элементов 25 И блока 11 инди кации сигнал отсутствует, и блок 11 находится в нерабочем состоянии. На выходе элемента 10 РАВНОЗНАЧНОСТЬ сигнал отсутствует и блок 12 также находится в нерабочем состоянии. В случае отказа контролируемого узла на выходах элементов В и 9 РАВНОЗНАЧНОСТЬ соответствующего канала блока 7 анализа появляется обратная комбинация сигналов - , 1. После инвертирования выходного сигнала с элемента 8 элементом 24 НЕ срабатывает соответствующий элемент 25 И, и сигналом с его выхода включается соответствующий элемент 26 индикации. Одновременно этот сигнал через элемент 27 ИЛИ поступает на второй вход установки в ноль триггера 14 блока 2 и устанавливает его в ноль, обусловливая тем самым запрет на прохождение через элемент 18 И 10 38 тактовых импульсов, и работа устройства контроля приостанавливается до прихода следующей команды Пуск на вход блока 2 управления. В случае отказов в работе устройства контроля при возникновении одиночных константных неисправностей в регистре 3 тестов либо в линии связи между последним и блоком 7 анализа (например, короткого замыкания поразрядных выходов регистра 3) на первых входах элементов 8 и 9 РАВНОЗНАЧНОСТЬ появляется комбинация сигналов , 1 или О, и в зависимости от значения сигнала, поступающего на вторые входы этих элементов 8 и 9с соответствующего выхода коммутатора 5, на выходах элементов 8 и 9 устанавливается также комбинация сигналов (1, , О, которая обусловливает прохождение сигнала с выхода элемента IO РАВНОЗНАЧНОСТЬ к соответствующему входу блока 12, на котором индицируется (высвечивается) номер отказавшего канала устройства контроля. Одновременно этот сигнал поступает через элемент 13 ИЛИ к второму входу предустановки триггера 14 и останавливает работу устройства для устранения причин отказа. Аналогично описанному предлагаемое устройство работает в случае константных неисправностей в любом канале блока 7 анализа. Таким образом, блок 7 анализа про- , изводит сравнение сигналов ответной реакции контролируемого узла 4, выявляя отказы последнего и одновременно отказы регистра тестов, а также собственные, и при появлении тех или иных указанных сбоев своевременно сигнализирует о них в управляющий блок 2 и обеспечивает соответствующую индикацию на блок 12 индикации отказов устройства контроля. Изобретение обладает следукнцими преимуществами по сравнению с базовым объектом АСК-1: повышается достойерность результатов контроля и соответственно уменьшается на 15-20% количество ошибочных диагнозов состояния контролируемых цифровых узлов; сокращается время поиска неисправностей контролируемых узлов примерно на 20%, в результате чего повышается производительность систем контроля на 7-10%.

. Фиг.2

Щ16

3

1 EjLJ

22

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых узлов | 1974 |

|

SU498619A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-15—Публикация

1982-12-22—Подача