(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УЗЛОВ

ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШЙЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Вычислительная машина со структурной интерпретацией входного языка | 1971 |

|

SU513567A2 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

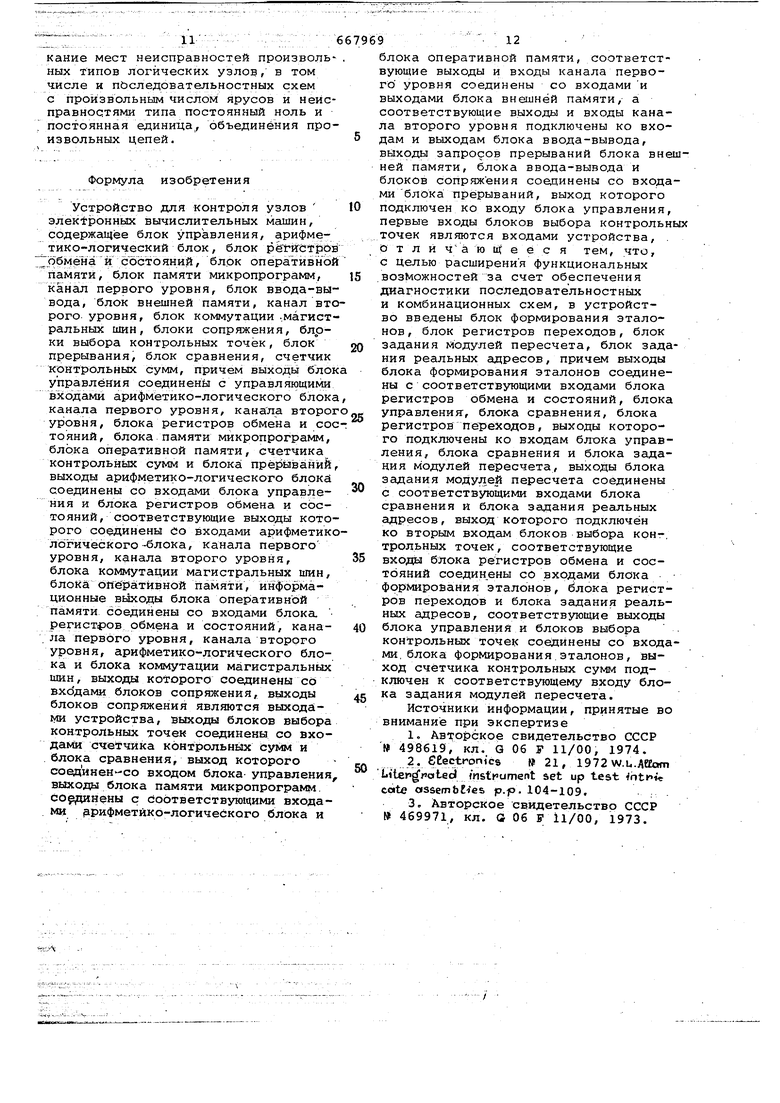

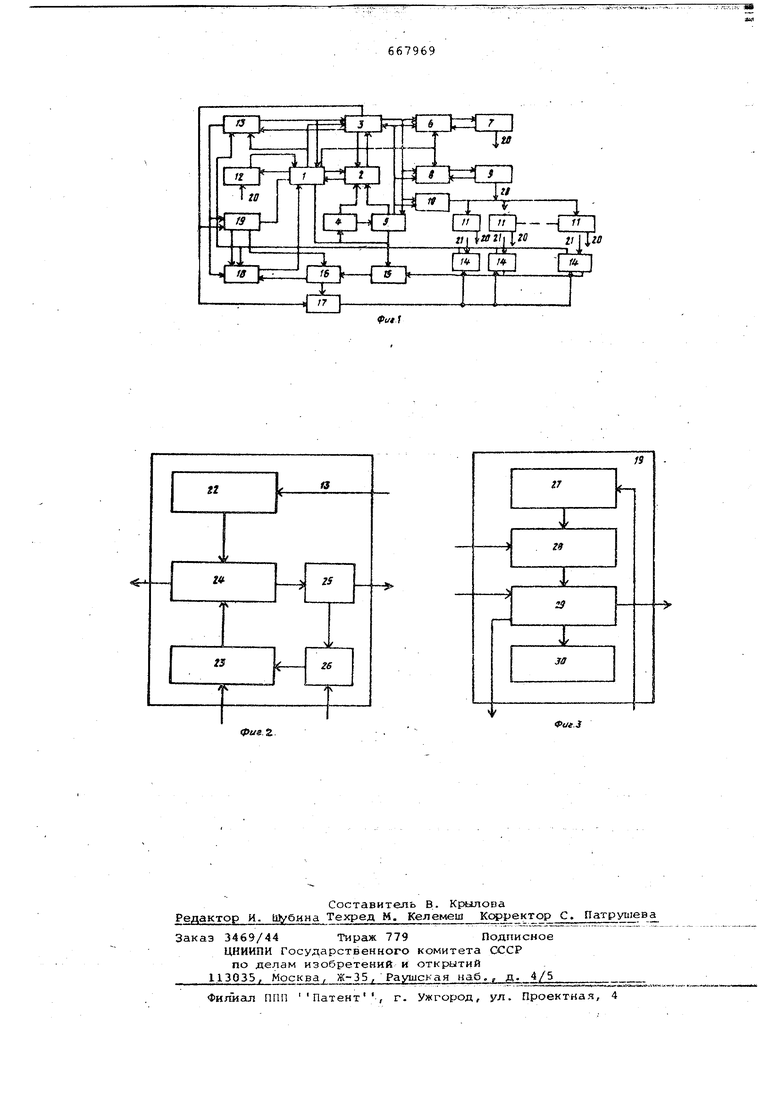

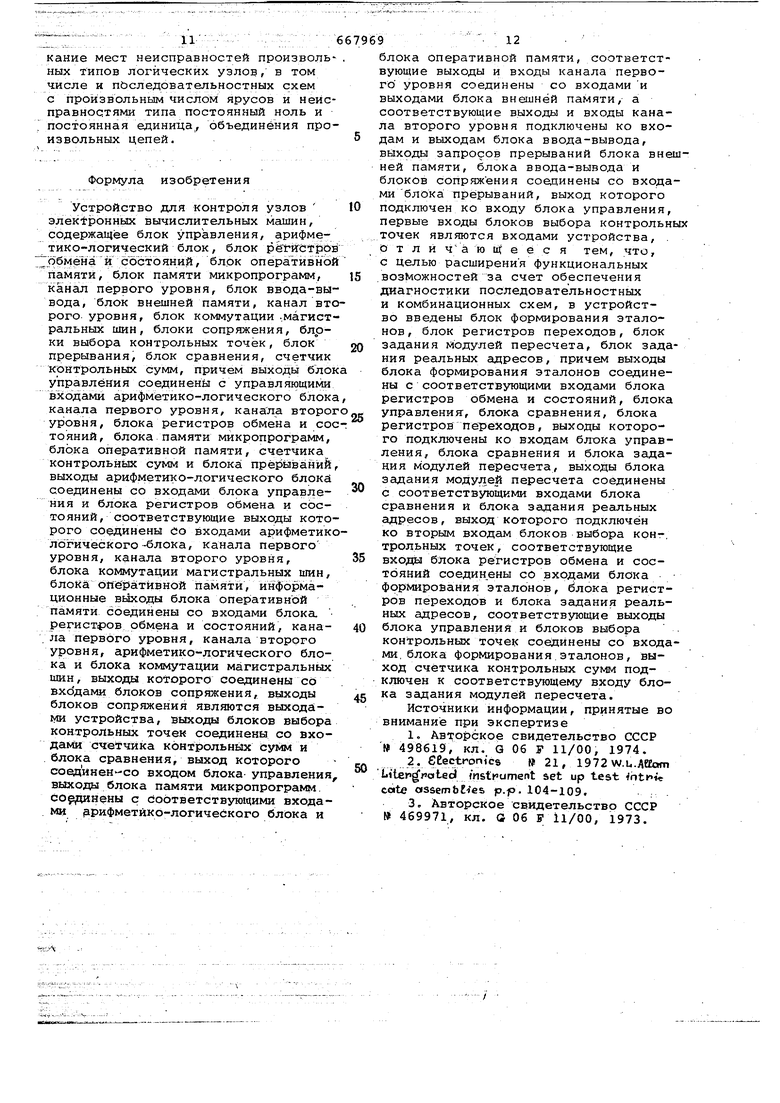

Изобретение относится к области автоматики и вычислительной техники и мЬжет быть использовано при реализации технических средств контрол и диагностики неисправностей логиче ких узлов дискретных устройств автоматики и электронных вычислительных машин. Известно устройство для контроля узлов электронных вычислительных машин, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления, при чем первый вуход блока ввода соединен со входом блока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внешними контактами контролируемого узла, второй выход блока ввода соединен со входом блЬка управления выходы которого подключены соответст венно к управляющим входам блока вво да, блока памяти и блока индикации, соединенного входом с выходом блока сравнения, регистр настройки, соединенный входом с первым выходом блока ввода, управляющим входом - с выходом блока управления, выходом - со вторым входом Коммутатора; выход ,блока памяти подключен к первому входу блока сравнения, второй вход которого соединен с выходом коммутатора 1 . Недостатком известного устройства является то, что оно не обеспечивает контроля последователъностных; схем, а его диагностические возможности сводятся к использованию только диагностическихтестов, Что связано с большими .предварительными затратами на их разработку. Известно устройство для контроля цифровых узлов электронных вычислительных машин, содержащее спёциализированный вычислитель, устройства ввода-вывода, блок сопряжения и блок измерений 2. Недостатком этого устройства является сложность и необходимость составления тестовых программ контроля, а его диагностические возможности ограничены использованием диагностических словарей или диагностических программ контроля. Наиболее близким техническим решением к предлагаемому изобретению является устройство, содержащее блок управления, арифметико-логический блок, блок регистров обмена и состояний, блок оперативной памя3ти, блок памяти микропрограмм., канал первого уровня, блок ввода-выводэг бло квнешней памяти, какал второго уровня, блок коммутации магистральных шин , блоки сопряжения, блоки выбора контрольных точек, блок пре рывания, блок сравнения, счетчик контрольных сумм, причём выходы блока управления соединены с управляющими входами арифметико-логического блока, канала первого уровня, канала второго уровня, блока регистров обмена и состояний, блока памяти микро программ, блока оперативной памяти, счетчика контрольных сумм и блока прерываний, выходы арифметико-логического блока .соединены со входами блока управления и блока регистров обмена и состояний, соответствующие выходы которого соединены со вхо дами арифметико-логического блока, канала первого уровня, канала второг уровня, блока коммутации магистральных шин, блока оперативной памяти, информационные выходы блока опера-. тивной памяти соединены со входами блока регистров обмена и состояний, канала первого уровня, канала второго уровня, арифметико-логического блока и блока коммутации магистральных шин, выходы которого соединены со входами блоков сопряжения, выходы блоков сопряжения являются выхода ми устройства, выходы блоков выбора контрольных точек соединены со входами счетчика контрольных сумм и блоха сравнения, выход которого соединен со входом блока управления, выходы блока памяти микропрограмм соединены с соответствующими входами арифметико-логического блока и блок оперативной памяти, соответствующие выходы и входы канала первого уровн соединены со входами и выходами блока внешней памяти, а соответствующие выходы и входы канала второго уровня подключены ко входам и выходам блока ввода-вывода, выходы запросов прерываний блока внешней паМяти, блока ввода-вывода и блоков сопряжения соединены со входами бло прерываний, выход которого подключе ко входу блока управления, первые в . ды блоков выбора контрольных точек являются входами устройства 3, Недостатком этого устройства явл ется необходимость предварительного Составле1 ия крнтрольнЬ-диагностйчес них тестов, невозможность его испол зования для проверки последовательностных схем, а его диагностические ; возможности связаны с Д1спользоваГй йём диагностических программ контр ля и по существу ограничены диагнос тичёскимй слбварйми. ,То- есть ное устррйствр имеет малые функциональные возможности, так как не обеспечивает диагностику последовательнрстньй и комбинационных схем. Целью изобретения является расшиение функциональных возможностей за чет обеспечения диагностики неисравностей последовательностных и омбинационных схем. Поставленная цель достигается тем, то в предлагаемое устройство введеы блок формирования эталонов, блок егистров переходов, блок задания одулей, пересчета, блок задания реальых адресов, причем выходы блока ормирования-эталонов соединены с оответствующими входами блока регистров обмена и состояний, блока правления, блока сравнения , блока егистров переходов, выходы которого одключены ко входам блока управления, 5лока сравнения и блока задания модулей пересчета/ выходы блока задания модулей пересчета соединены с соответствующими входами блока сравнения и блока задания реальных адресов, выход которого подключен ко BTOptirt входам блоков выбора контрольных точек, соответствующие входы блока регистров рбмена и срстояний соединены со входами блока формирования эталонов, блока регистров переходов и блока задания реальных адресов, соответствующие выходы блока управления и блоков выбора контрольных точек соединены со входами блока формирования эталонов, выход счетчика контрольных сумм подключен к соответствующему входу блока задания модулей пересчета. Устройство рбеспечивает как программный контроль и диагностику неисправ.ностей комбинационных и после довательностных схем, так и их контроль и диагностику на псевдослучайных кодах и в режиме многотерминальной системы с разделением времени, тоесть обеспечивает одновременную работу нескольких выносных пультов контроля (блоков сопряжения) с использованием стандартнрго псевдослучайного циклического кода, по1 рождаемого полиномом аСх)5:аЛх)х ( И - количество информационных входных каналов проверяемого изделия) в режиме счета контрольных сумм на фиксированном поле псевдослучайных комбинаций. На Фиг . 1 показана блок-схема предлагаемого устройства; на фиг. 2 пример технической реализации блока формирования эталонов; на фиг. 3 пример технической реализации блока регистров переходов. Устройство содержит блок управления 1, арифметико-логический блок 2, блок 3 регистров обмена и состояний, блок 4 памяти микропрограмм, блок 5 оперативной памяти, канал 6 второго уровня, блок 7 ввода-вывода, канал 8 первого уровня, блок 9 внешней памяти, блок 10 коммутации магистральных шин, блок 11 сопряжения, блок 12 прерываний, блок 13 формирования эталонов, блок 14 выбора контрольны точек, счетчик 15 контрольных сумм, блок 16 задания модулей пересчета, блок 17 задания реальных адресов, блок 18 сравнения, блок 19 рег ров переходов, шины 20 запросов пре рываний, шины 21 подключения контро руемых изделий. Блок 13 формирования эталонов (см,фиг. 2) состоит из регистра 22, набора 23 эталонных элементов, комм татора 24, схемы 25 сравнения по мо лю три и узла 26 деления. Блок 19 регистров переходов (см. фиг. 3) со тоит из регистра 27, схемы 28 сравй ния по модулю два, узла 29 приорите тов, дешифратора 30. Устройство работает следующим образом. На этапе предварительной подготовки устройства к работе выполняет ся ряд операций по загрузке операционной системы и формирование служебных массивов информации для создания модели контролируемого изделия в блоке 13 формирования этало нов. После включения устройства по сигналу с блока 1 осуществляется обращение к блоку 4 памяти микропрограмм и производится выдача последовательности команд програйМЫ загрузки в блок 5 оперативной памяти. Информация из блока 9 внешней памяти через канал 8 первого уров-г ня перезаписывается в блок 3 регист ров Обмена и состояний. Здесь форми руется последовательность управляющих наборов для задания реж:1ма обмена с блоком 7 ввода-вывода и блоком 9 внешней памяти и задаются адреса в блок 5 оперативной памяти, который обеспечивает выдачу на блок 10 коммутации магистральных шин управляющих команд. Затем осу-, ществляет формирование Функциональной модели проверяемого изделия. Для ее формирования используется информация о монтажных соединениях изделия, вводимая с помощью блока 7 ввода-вывода. Кроме того, для формирования мод ли вводится каталог интегра:льных схем, используемых в изделиях прове ряемого типа и информация о расположении элементов на поле ячейки. При подготовке к занесению в бло оперативной памяти соответствующих массивов производится разбивка базо вых элементов функциональных узлов на условные базовые элементы типа И ИЛИ, НЕ-И, НЕ-ИЛИ. В каталоге типов хранится информация о разделении функциональных узлов на условные базовые элементы и о связях между ними. При разбиении базовые элемент нумеруются и в массив заносятся нов значения номеров разовых элементов и признаков. в блок 5 оперативной памяти заносятся массив Прямых ссылок и массив прямЕлх связей, причем на t-ом месте :в MacdMle пряйых™ссьшок находится относительный адрес массива прямых связей, начиная с которого ограниченные разделителями располагаются номера условных базовых элементов, хотябы один вход которых связан с выходом -го условного базового элемента. Кроме того, формируются массив обратных ссылок и массив обратных связей аналогичные двум предыдущим массивам с заменой входов на выходы. Получение опийанных массивов состоит : в следующем. При разбиении на условные базовые элементы и их нумерации информация, находящаяся в каталоге типов микросхем о прямых связях между условными базовыми элементами внутри функциональных элементов заносится в массивы прямых ссылок и прямых связей. Затем рассматриваются все условные базовые элементы, информация 0связях которых еще не вошла в мас,сивы. Координаты выхода обрабатываемого базового элемента заносятся в первую свободную ячейку массива прямых связей. После ввода всей перечисленной информации с блока 7 ввода-вывода, конкретное устройство которого определяется каналом 6 второго уровня, управляемого регистрами блока 3, информация на регистры после необходимых вычислений и преобразований данных, записанных в блоке 9 внешней памяти и коммутируеjvibix каналогй 8 первого уровня, через арифметико-логический блок 2 поступает на блок 3 регистров обмена и состояний. Порядок поступления команды данных определяется Операционной системой,, загружаемой в блок 5 оперативной памяти. Загрузка операционной системы инициируется блоком 1управления, который задает последовательность операций в соответствии с. последовательностью команд, записанной в блоке 4 памяти микропрограмм, который представляет собой запоминающее устройство последовательного действия. В соответствии со сформированной в блоке формирования эталонов 13 моделью контролируемой ячейки осуществляется определение массива состояний всех базовых элементов f проверяемой ячейки на каждом контрольно-диагностическом тестге, вводимых через канал 6 второго уровня с блока 7. ввода-вь1вода иЛи непосредственно с блока 5 оперативной памяти. Режим ввода тестовой информации определяет- ся операционной системой. -На этапе программного контроля логических узлов с блоков 11 сопряжения, я-вляющихся оконечными блоками контроля, к которым подклго.чаются контролируемне изделия, производится вьу1ача сиг налов запросов на прерывание по шина 20. Эти сигналы поступают в блок l2 прерываний, где обрабатйваются и в соответствии с дисциплиной обслуживания, задаваемой операционной системой, поступают в виде запросов в блок 1 управления. Один из блоков 11 подключается через блок 10 к каналу обмена с блоком 5. С подключенного блока 11 зыдается информация о типе проверяемых изделий и режиме. контроля. Через блок 10 коммутации магистральных шин по селекторным управляющим шинам эта информация пос тупает в блок 1, где принимается решение о выдаче соответствующих команд управления, определяемых операционной системой, задаваемой с бло ка 5. Послё заЁершёНия выдачи С71ужебных и вспомогательных сигналов, определяемых спецификой проверяемых изделий,, производится выдача теста разделенйя входов и выходов контролируе мого изделия. Затем выдается последовательность установочных наборов и Осуществляется задание контрольнодиагностических стимулирующих наборов. Ответная реакция контролируемого изделия записывается в блок 5 и по мере накопления поступает в арифметико-логический блок 2, где осуществляется сравнение реальных и эталонных состояний контролируемого изделия, COOT нет ствующих заданным стимулирующим воздействиям. При обнаружении несовпадения реальных сигналов на выходах контролируемого изделия с эталонными,контролирующий набор, на-котором произошло несовпадение, вьщает с я в регистр 22 блока 1 формирования эталонов через блок 3 регистров обмена и состояний, а на коммутатор 24 поступает код, соответ ствующи подключений) элемента из набора эталонных элементов 23, тип которого соотв.етствует элементу, на выходе которого произошло несовпадение сигнала с эталонным значением. Подготовленные ранее массивы свяэей по номеру контакта, на котором произошло это несовпадение, используются для определения адреса элемента, ..связанного по выходу с этим контактом, и через ёлок 3 регистров обмена и состояний адрес въедается в блок 17 задания реальных адресов, который модифицирует этот аярёс., из кода модели узла в реальный адре элемента на ячейке. С блока 17 выдается код на управление блоком 14 выбора контрольных точек, который в роответствии с заданным адресом осу ществляет подключение выводов элеме та (входов и выходов) к блоку 18 сравнения. На другие входы блока 18 поступают сигналы с выводов э талонн го элемента из набора 23 эталонных элементов, подключенного коммутатоfiBuTSb-WSuiSc--ISsasibii.-i. ром 24. По сигналу с выхода блока 18 принимается решение об исправности проверенного элемента и в случае совпадения сигналов на выводах эталонного и контролируемого элементов с блока 1 вьедается сигнал на вычисление адреса следующего элемента, связанного с одним из входов элемента, проверенного на рассмотренном этапе. Одновременно с этим производится оценка риска критических состояний на рассматриваемом наборе стимулирующих воздействий. Для этого в регистр 27 блока 19 регистров переходов записывается предыдущий контролирующ11й набор, а на входе с.хёмы 28 сравнения по модулю два задается контролирующий набор, на котором получено первое несовпадение выходных состояний с эталонными. С учетом возможных максимальных разбросов задержек выбираются управляющие сигналы на узле 29 приоритетов. При воз-никновении сигналов на выходах дешифратора 30, который осуществляет свертку кода в-полиадический, определяется возможность возникновения критических состязаний. В этом случае контролирующий набор отбрасывается- и разбивается на совокупность наборов, при которых допускается смена стимулирующих воздействий более, чем на одном входе контролируемого узла. При этом для определения поля состояний используется схема 25 сравнения по модулю три и узлы 26 деления блока 13 фор- мирования эталонов. После проверки всей совокупности элементов будет определена пара элементов, для которой выходные (входные) сигналы не соответствуют совокупности.эталонных наборов. Использование блоков 13 и 19 обеспечивает в этом режиме работь устройства контроль и отыскание места неисправности как для комбинационных схем, так.и схем с произвольньм числом ярусов памяти. Режим программного контроля логических узлов связан с большими затратами на предварительную разборку контрольно-диагностических тестов и может быть эффективно применен только для устоявшейся серийной продукции. В случае опытного производства этот способ контроля связан с еще большими затратами из-за большого числа корректировок в процессе отработки документации. Поэтому в предложенном устройстве предусмотрен режим контроля узлов,на псевдослучайных кодах. Известные устройства контроля, не позволяют производить диагностику отказов с использованием этих методов и контроль последовательностных схем. В режиме контроля и диагностики неисправностей йа псевдослучайных кодах также как и в режиме программного производится предварительное занесение служебных массивов и поочередное подключение блоков 11 сопряжения к магистральным шинам устройства. По соответствующему сигналу прои водится разделение входов и выходов контролируемого изделия и выдается последовательность установочных наб ров и константных управляющих сигна лов. Арифметико-логический блок 2 пер ключается- блоком 1 управления в режим формирования псевдослучайного кода, порождаемого полиномом К-1( -oi(i) r ajfxVK де п - количество информациойных входных каналов проверяемого изделия, a-(x) xrTjod(x) причем gfx) - произвольный полином с коэффициентами из поля GP( Фор г.«1руемый при этом, псевдослучайный циклический код с кодовым расстоянием, равным единице, поступает чер магистральные шины на входы подключ ного блока 11 сопряжения. Генерируе мая последовательность псевдослучай ных кодов заносится в блок 5 оперативной памяти и с темпом работы это го блок;а выдается в магистральные шины. Формируе№яй на этом этапе код перезаписывается в блок 9 внешней памяти через канал 8 первого уровня и может быть использован многократн при контроле изделий с числом кон1;ак тов не меньшими . Стимулирующие тестовые наборы в виде псевдослучайных кодов и конста ные управляющие сигналы, определяющие разрыв обратных связей в.контро лкруемых изделиях и взаимозависимые .входные воздействия, обеспечивающие исключение запрещённых стимулирующих наборов на входах контролируеммого изделия, однозначно определяют последовательность полей состояния элементов контролируемого изделия. На этапе контроля на псевдослучайных тестовых наборах с помощью счетчика 15 контрольных сумм определяется общая контрольная сумма п выходным шинам контролируемого изде ЛИЯ. Вычисленная контрольная сумма записывается в блок 5 оперативной памяти и поступает .в блок 16 задания модулей пересчета, где производится ее преобразование, заключающееся в последовательном делении на коэффициенты c.j(x) . с выхода бло ка 16 код поступает на вход блока 18 сравнения, на другие входы которого задаются эталонные контрольные суммы с блока 3 регистров обмена и состояний. Причем эталонная контрольная сумма может быть либо вычислена с помощью, модели контролируемого изделия, либо определена путем контроля заведомо исправного. элемента. При совладении кодой на входах блока 18 контролируемое изделие признается исправным. Если, общая контрольная сумма не совпала с эталонной, то производится подсчет локальных контрольных сумм по каждому выходу. Эти контрольные суммы сравниваются с их эталонными значениями и первая, например по порядку возрастания номеров контактозв выходов контролируемого изделия, контрольная суь1ма, не совпавшая с эталонной, определяет адрес элемента, связанного с выходньом контактом, на . котором произошло несовпадение контрольных сумм. С помощью блока 14 выбора контрольных точек по адресу, определяемому блоком 17 задания реальных адресов, осуществляется ,подключение выходов элемента к счетчику контрольных сумм и- сравнение контрольных сумм с эталонными значениями. Одновременно коммутатором 24 блока 13 формирования эталонов осуществляется подклк чение входов эталонного элемента ко входам элемента размещенного в проверяемом Изделии. Выходы эталонного и контролируемого элементов подключаются ко вхо.дам блока 18 сравнения. Повторяется контроль на полном псевдослучайном наборе.и при совпадении сигналов навыходах эле-, ментов принимается решение об исправности элемента, установленного в изделии, С использованием массивов связей и ссылок определяется адрес следующего элемента, связанного с элементом, проверенным на предылущсм этапе. Процедура полностью повторяется. При обнаружении первого элемента, функционирование которого не совпадает с функционированием эталонного элемента, вьщеляется пара возможно неисправных элементов. Разделение .неисправности выполняется одним из известных методов вручную. Использование в предложенном устройстве блока 13 формирования эталонов блока 19 регистров переходов и блока 16 задания модулей пересчета обеспечивает контроль и диагностику неисправностей комбинационных и последовательностных схем не только в режиме программного контроля, но и с использованием псевдослучайных наборов. Это особенно эффективно на этапе производства опытных образцов изделий, когда структура контролируемых изделий подвергается значительным переработкам и разработка контрольно-диагностических тестов связана со значительными затратами труда и машинного времени, а.оперативая корректировка тестов затруднена. По сравнению с известными устройтвами предложенное обладает большии функциональными возможностями, так как обеспечивает контроль и отыскание мест неисправностей произвольных типов логических узлов, в том числе и пЬследовательностных схем с произвольным числом ярусов и неисправностями типа постоянный ноль и постоянная единица, объединения произвольных цепей. Формула изобретения Устройство для контроля узлов электронных вычислительных машин, содержащее блок управления, арифметико-логический блок, блок peffifdtpOB обмена и состояний, блок опера тивной памяти, блок памяти микропрограмм, канал первого уровня, блок ввода-вывода, блок внешней памяти, канал вто рого уровня, блок коммутации ..магист ральных шин, блоки сопряжения, блоки выбора контрольных точек, блок прерывания, блок сравнения, счетчик контрольных сумм, причем выходы блок управления соединены с управляющими входами арифметико-логического блок канала первого уровня, канала второ уровня, блока регистров обмена и со тояний, блока памяти микропрограмм, блока оперативной памяти, счетчика контрольньк сумм и блока; прёры)заний выходы арифметико-логического блоки соединены со входами блока управления и блока регистров обмена и состояний, соответствующие выходы кото рого соединены do входами арифметик логического -блока, канала первого уровня, канала второго уровня, блока коммутации магистральных шин, блока оперативной памяти, информационные выходы блока опер ативной памяти соединены со входами блока. регистров обмена и состояний, кана. ла первого уровня, канала второго уровня, арифметико-логического блока и блока коммутации магистральных шин, выходы которого соединены со входами блоков сопряжения, выходы блоков сопряжения являются выходами устройства, выходы блоков выбора контрольных точек соединены со входакм контрольных сумм и блока сравнения, выход которого соеяйнеН-со входом блока управления выходы блока памяти микропрограмм, со ринены с Соответствующими входами арифметико-логического блока и лока оперативной памяти, соответстующие выходы и входы канала первоо уровня соединены со входами и выходами блока внешней памяти, а оответствующие выходы и входы канаа второго уровня подключены ко вхоам и выходам блока ввода-вывода, выходы запросов прерываний блока внешней памяти, блока ввода-вывода и блоков сопряжения соединены со входаи блока прерываний, выход которого подключен ко входу блока управления, первые входы блоков выбора контрольных точек являются входами устройства, . о т л и ча ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения диагностики последовательностных и комбинационных схем, в устройство введены блок формирования эталонов , блок регистров переходов, блок задания модулей пересчета, блок задания реальных адресов, причем выходы блока формирования эталонов соединены с соответствующими входами блока регистров обмена и состояний, блока управления, блока сравнения, блока регистров переходов, выходы которого подключены ко входам блока управления, блока сравнения и блока задания модулей пересчета, выходы блока задания модулей пересчета соединены с соответствующими входами блока сравнения и блока згшания регшьных адресов, выход которого подключён ко вторым входам блоков выбора кон-, трольных точек, соответствующие входы блока регистров обмена и состояний соединены со блока формирования эталонов, блока регистров переходов и блока задания реальных адресов, соответствующие выходы блока управления и блоков выбора контрольных точек соединены со входами, блока формирования.эталонов, выход счётчика контрольных сумм подключен к соответствующему входу блока задания модулей пересчета. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 498619, кл. G 06 F 11/00, 1974. 2,eeectronics 21, 1972w.u.AeSam Litep rcfted mstfument set up test intfiv cate orssembEies p.f. 104-109. 3,Авторское свидетельство СССР № 469971, кл. G 06 F 11/00, 1973.

IS

гг

2«

25

и

Т

I

фи&..

Фиг.З

Авторы

Даты

1979-06-15—Публикация

1976-06-01—Подача