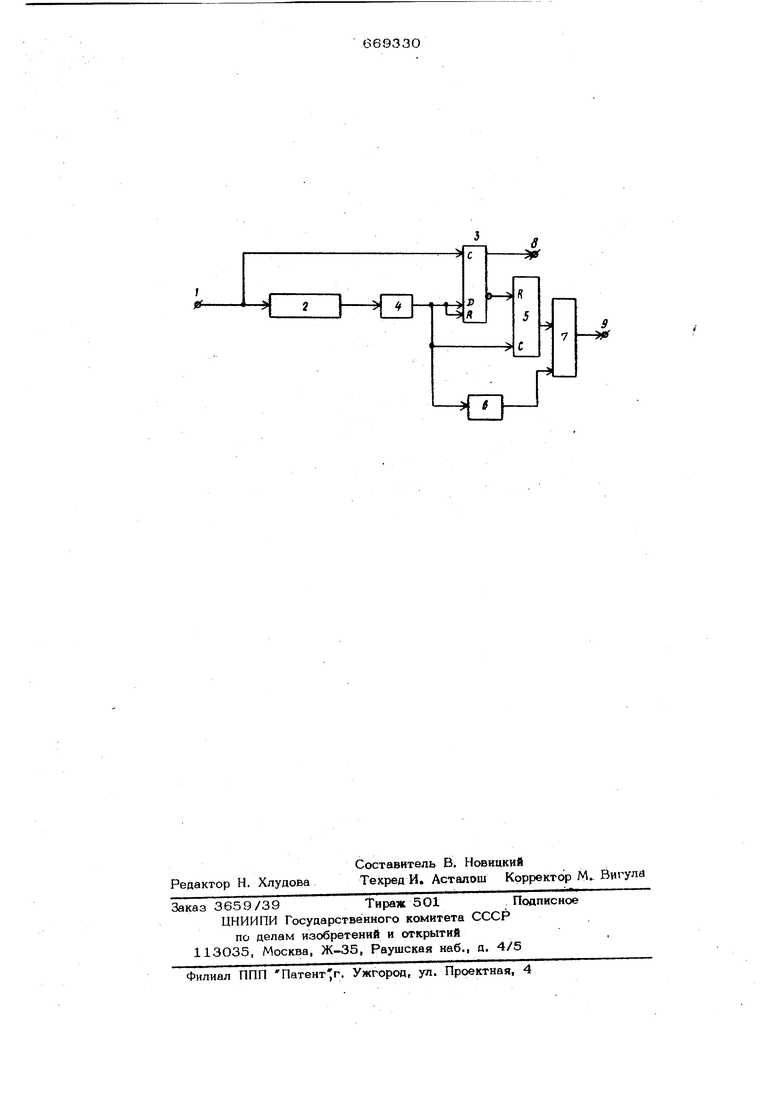

В исходном состоянии отсутствуют им пульсы на входной шине 1 и на выходе формирователя 4 имеется низкий потенциал, которым триггер 3 устанавливается в .нулевое состояние с низким потенциалом на единичном выходе, соединенном с первой выходной шиной 8 и высоким потенциалом на нулевом выходе, который прикладывается к нулевому входу триггера 5, подготавливая его к приему сигналов по входу синхронизации. Пусть начальная установка триггера 5 такова, что на его единичном выходе имеется низкий потенциал. Низкий потенциал с выхода триггера 5 прикладывается к одному из входсш элемента И 7 и независимо от сигнала на втором его входе обеспечивает на выходе элемента 7 высокий потенциал. Первый импульс входной последовательности поступает на вход устройства 2 точной временной задержки, на выходе которого появляются два импульса, задержанные на время Т. , Т соответственно относительно пер вого импульса. Эти импульсы поступают на вход формирователя 4. С выхода формирователя 4 два строба длительностью С. и Cj поступают на информационный и нулевой входы триггера 3. Таким образом, в интервалах времени от т, (Tj Tj) выключается установка триггера 3 в О, а на информационном входе существует высокий потенциал, т. е, триггер 3 в эти моменты готов к приему импульсов по входу синхронизации. Одновременно стробы Т( и Тп через инвертор 6 запирают по второму входу схему. И 7, обеспечивая на ее выходе высокий потенциал независимо от состояния первого входа в эти моменты времени. Кроме того, стробы t и Т поступают на вход синхронизации триггера 5 и устанавливают его в единичное состояние с высоким потенциалом на его выходе, который прикладывается к первому входу схемы И 7. Однако состояние выхода схемы И не изменится, т. к. она заперта по второму входу. Если в инtepвaл8 времени от Tj до (Tj + ) на ввкодную шину 1 поступит импульс то фронтом этого импульса триггер 3 по входу синхронизации будет переключен в единичное состояние и на выходной шине 8 появится высокий потенциал, являющийся фронтом выходного импульса. Срез выходного импульса формируется в момент Т +1, когда триггер 3 возвращается в исходное состояние срезом строба Т, по нулевому входу, независимо от состояния входа синхронизации. Одновременно с формированием выходного импульса единичным выходом триггера 3, на его нулевом выходе появляется импульс низкого потенциала, который своим фронтом возвращает в нулевое состояние триггер 5 и на его выходе устанавливается низ- кий потенциал. Схема И 7 снова оказывается запертой по первому входу и состояние ее выход(а не изменится после того, как в момент (Тх TJ ) на втором входе появится высокий потенциал. Аналогично работает устройсгво при поступлении на входную шину третьего импульса в интервале от Т до (T.-bTj). Итак, если межимпульсные интервалы многоимпульсного кода укладываются в допуск, то на выходной шине 8 устройства появляются импульсы и на выходной шине 9 сохраняется высокий потенциал. При выходе хотя бы одного межимпульсного интервала многоимпульсного кода за пределы допуска на выходной шине 9 установится низкий потенциал. Формула изобретения Устройство Допускового контроля временных интервалов по авт. св. № 513505,. отличающееся тем, что, с целью расширения функциональных возможностей, оно дополнительно снабжено триггером, инвертором и элементом И, при этом нулевой вход дополнительного триггера соединен с нулевым выходом первого триггера, аыход формирователя присоединен к входу инвертора и к входу синхронизации, дополнительного триггера, выхооь дополнительного триггера и инвертора соединены с входами элемента И, выход которого соединен с второй выходной шиной устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1978 |

|

SU764112A1 |

| Устройство для обнаружения потери импульса | 1989 |

|

SU1647870A1 |

| Формирователь импульсов | 1979 |

|

SU813733A1 |

| Формирователь импульсов | 1978 |

|

SU758496A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1357987A1 |

| Цифровое фазометрическое устройство | 1978 |

|

SU763813A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

Авторы

Даты

1979-06-25—Публикация

1978-01-25—Подача