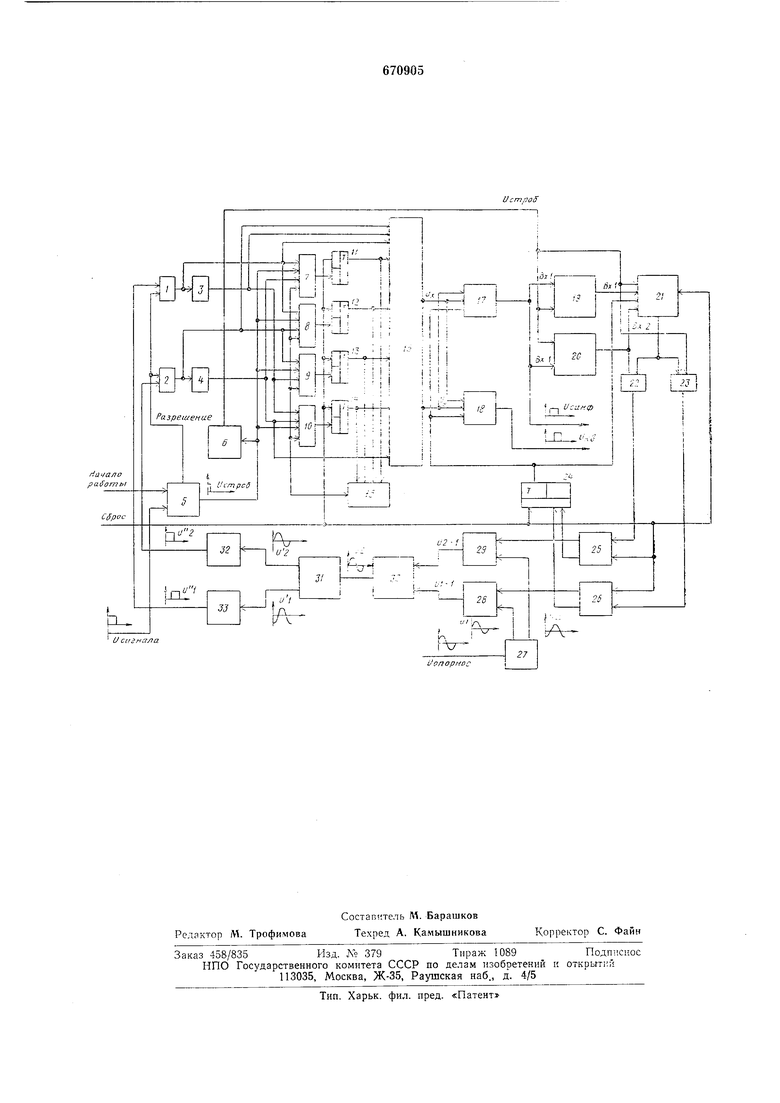

Изобретение относится к области электроизмерительной техники и предназначено для использования в широкополосных фазовых корреляторах и фазочув-ствительных вольтметрах. Известно устройство для выбора квадранта и фазирования сигнала, содержащее коррелятор, инверторы, линии задержки, усилители, триггеры 1. Недостатком такого устройства является низкая точность фазирования. Известно также устройство, предназначенное для выбора квадранта и фаз ирования сигнала, представляющее собой фазовый коррелятор, состоящее из блоков для получения входного и эталонного сигналов, дифференциальных компараторов, обнаруживающих нулевой потенциал, линий задержки, инвертора, дифференциальных усилителей и триггеров 2. Недостатком этого устройства является отсутствие автоматического фазирования сигнала и получения сигнала в двух квадрантах. Целью изобретения является автоматизация фазирования, получение сигнала в двух квадрантах и повыщение точности. Это достигается тем, что в устройство для автоматического выбора квадранта, содержащее два блока запрета, блок управления, выход которого соединен с первыми входами первого и второго элементов совпадения, соединенных своими выходами со входом первого и второго триггеров, выходы которых соединены с первым и вторым входом блока распределения сигналов соответственно, первый фазорасщеплтель, выходы которого соединены соответственно со входам:и первого .и второго усилителя-формирователя, введены первый и второй блоки совпадений, блок запрета срабатывания по заднему фронту, третий и четвертый элементы совпадения, третий, четвертый и пятый триггеры, блок запрета срабатывания по заднему фронту, блок распределения сигналов, первый и второй управляемые переключатели, блоки фазового компарирования отставания и опереженения, блок выработки сигнала окончания подстройки фазы, первая и вторая сборки элемента сигналов, первый II второй счетчики, первый и второй управляемые делители, сумматор и второй фазорасщепитель, причем первый и второй выходы второго фазорасщепител;; соединены с нервыми входами первого и второго управляемых делителей, соединенных своими выходами соответственно с первым и вторым входами сумматора, выход которого соединен со входом первого фазорасщепителя; выходы первого и второго усилителя-Преобразователя соединены соответственно с первыми входам:И первого и второго блока совнадений, вторые входы которых соединены со вторым выходом блока управления, выход nepiBoro блока совпаде:кий соединен с третьим входом блока рас|1гределения сигналов, с входом первого блока запрета, со вторым входом первого элемента совпадения и с третьим входом TD тьего элемента совпадения, первый вход которого соединен со входом блока запрета срабатывания по заднему фронту, а второй вход соединен с выходом второго блока совпадений, со входом второго блока запрета, с четвертым входом блока распределекия сигналов и со вторым входом второго элемента совпадения, третий вход которого соединен с выходом первого блока запрета, с пятым входом блока распределения сигналов и со вторым входом четвертого элемента совпадения, соединенного своим иерным входом со входом блока запрета ера батыван.ия по заднему фронту, а своим третьим входом с выходом второго блока запрета, третьим входом первой схемы совпадения и шестым входом блока распределения сигналов, выходы третьего ,и четвертого элементов совпадения соединены соответственно со входами третьего и четвертого триггеров, выходы которых соединены с седьмым и восьмым входами бложа распределения сигналов, первый выход которого соединен с первым входом первого упрапляемого переключателя и со вторым входе--. второго управляемого переключателя, а второй выход соединен с первым входом второго управляемого переключателя и со вторым входоМ первого управляемого переключателя, третьи входы управляемых переключателей соединены с выходом пятого триггера и с первым входом блока вьгработ|ки сигнала окончания подстройки фазы, выход первого переключающего блока соедиНен с первыми входа1М-и блоков фазового компарирования отставания ,и опережения, вторые входы которых соединены с выходом схемы запрета срабатывания по заднему фронту и со вторым входом блока выработки сигнала окончания подстройки фазы, третий вход которого соединен с выходом блока фазового комларирования отставания и nepiBbiM входом первого элемента ИЛИ, а четвертый вход соединен с выходом блока фазового комларирования опережедия И с первым входом второй сборки сигггалов, выход блока выработки сигнала окончания подстройки фазы соеди«ен со иторыми выходами первой и второй сборки сигналов, выходы которых соединены соответственно со входами первого « второго счетчика, соединенных соответственно своими nepiBbiMH входами со вторыми входами первого и второго делителя, а вторые входы счетчиков соединены с первым и вторым 1ходами пятого триггера соответственно, при этом первый, второй, третий и четвег тый входы блока запрета срабатывания по заднему фронту соединены соответственно с четвертыми входа:ми элементов совпадения. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит первый и второй блоки совпадений У и 2, первый и второй блоки запрета 3 и 4, блок управления 5, блок запрета срабатывания по заднему фронту 6, первый, второй, третий и четвертый элементы совпадения 7-10, первый, второй, третий и четвертый триггеры //- 14, блок запрета срабатывания по заднему фронту 15, блок распределения сигналов 16, первый и второй управляемые переключатели 17 и 18, блок фазового компарирования отставания 19, блок фазового компарировапия опережения 20, блок выработки сигнала окончания подстройки фазы 21, пер.вую и вторую сборки сигналов 22 и 23, триггер переполнения 24, первый и второй счетчик 25 и 26, первый фазораспдеп-итель 27, первый и второй управляемые дел-ител-и 28 и 29, сумматор 30, второй фазорасгцепитель 31, усилители-формирователи 32 и 33. Устройство работает следующим образом. В начале работы устройства по сигналу «сброс все триггеры устанавливаются в нулевое положение. На вход первого фазорасщеиителя 27 подается опорное напряжеНапряжения U и /2 на выходе раВНы между собой по амплитуде и сдвинуты относите аьно друг друга на 90°. Коэффициент передачи дискретных делителей переменного напряжения 28 и 29 при сигнале «сброс равен «1 и напряжении U i L2 без изм-гнения проходят на вход сумматора 30, осуществляющего геометрическое сложение векторов входных напряжений. Выход сумматора соединен со в.ходом второго фазоращепителя 31, выполняющего такие же функции, что и первый фазорасщепитель 27, т. е. напряжение U и HI сдвинуты одно относительно другого на 90°. К выходам фазорасщепителя 31 подсоединены усилители-фор.мираватели 32 и 33, которые преобразуют синусоидальные напряжения в напряжения прямоугольной формы. Выходы усилителей-формирователей 32 и 33 соединены с первыми входами блоков совпадения / и 2. Входное напряжение t/сигн поступает на блок управления 5. По команде «начало работы в блоке управления 5 формируется команда «разрешение, поступающая на вторые входы блоков совпадений 1 и 2, одновременно формируется узкий СТробируЮЩИЙ импульс i/строб по переднему фронту f/сипп поступающий на первые входы элементов совпадения 7, 6, 9, 10. Для устранения ложного срабатывания блоков фазового компарирования 19, 20 и устройства выработки сигнала окончания подстройки фазы 21 по заднему фронту оигнала строб проходит через схему запрета срабатывания по заднему фронту 6. По сигналу «разрешение напряжение с выходов усилителей-формирователей 32 и 33 через блоки совпадения У и 2 и блоки запрета 3 и 4 иоступает на вторые и третьи входы элементов совпадения 7-JO, а также на входы блока распределения сигналов 16. При совладении сигналов на первых, вторых и третьих входах .одного из элементов совпадения 7, 8, 9 -или 10 включается один из триггеров выбора квадрантов //, 12, 13 или 14, соответст1вующей квадранту, в котором находится бсиги относительно f/I и t/2. При срабатывании одного из триггеров 11, 12, 13 или 14 блок запрета 15 блокирует элементы совпадения 7, 8, 9 я 10, чтобы устранить срабатывание триггеров 11, 12, 13 или 14 в процессе фазирования. Выходы триггеров 11, 12, 13 или 14 соединены с первыми входами блока распределения сигналов 16. Напряжения f/x и f/y с выхода блока 16 поступают на входы управляемых переключателей 17 и 18, выходное напряжение переключателя 17 (Усппф совпадает по фазе с напряжением сигнала /синф, а выходное напряжение переключателя 18 УКВ отстает от синф на 90°.

Выход управляемого переключателя /7 соединен с первыми входами блоков фазоiBoro компарировавия 19 и 20. Если сигнал на входе строба «омларатора 19 быстрой отстает от f/синб. поступающего на другой вход 19 от О до 45 эл. град, на выходе компаратора появляются импульсы, которые через сборку сигналов 23 поступают ка вход счетчика 26. Двоичный код со счетных выходов счетчика 26 поступает на управляющие входы делителя переменного напряжения 28, при этом на выходе делителя соответственно изменяется амнлитуда напряжения С/1.

Когда сигналы f/строб и U,,,, совпадут, начнет работать фазовый компаратор олережения 20, т. е. на выходе компаратора 20 появится импзльс, который поступит на второй вход блока выработки сигнала окончания подстройки фазы 21, на выходе этого блока появляется сигнал, запирающий сбора-си 22 и 23. При этом С/,-„пф совпадает с i/cHni а UKB отстает от С/с„нф на 90 эл. град.

При фазовом сдвиге между н строб от 45 эл. град, до 90 эл. град, на входа1х компаратора 19 схема работает также, как и в случае фазового сдвига межДУ синф и t/crpo6 от о до 45 эл. град. Однако, даже при полностью включенном делителе 28 бсимф и f/.,oo6 не могут совпадать и на выходе переноса счетчика 26 появляется импульс, который включает триггер переполнения 24 и блок 21 устанавливается в исходное положение; на выходе переключателя 17 напряжение С/сииФ совпадает с напряжением Uy, на выходе переключателя 18 напряжение f/кв совпадает с напряжением U. В этом случае начинает работать блок фазового компарирования опережения 20 и импульсы через сборку 22 поступают на вход счетчика, изменяя амплитуду напрялсения на выходе управляемого делителя переменного напряжения 29. При совпадении f/синф и f/строб начинает работать фазовый компаратор 19, и блок выработки сигнала окончания подстройки фазы 21 запрещает прохождение импульсов через сборки 22 и 23. При этом f/синф совпадает с t/e,irii, а UK- отстает от i/синф на 90 эл. град.

Применение изобретения позволяет повысить точность, производить автоматизацию фазирования и получение сигнала в двух квадрантах.

Формула изобретения

Устройство для автомат ического выбора квадранта, содержащее два блока запрета, блок управления, выход которого соединен с первыми входами первого и второго элементов совиадения, соединенных своими выходами со входом первого и второго триггеров, выходы которых соединены с первы.м и вторым входом блока распределения сигналов соответственно, первый фазорасщепитель, выходы которого соединены соответственно со входами первого и второго усилятеля-формирователя, отличающееся тем, что, с целью автоматического фазирования, получения сигнала в двух квадрантах и повышения точности, в него введены первый и второй блоки совпадений, блок запрета срабатывания по заднему фронту, третий i; четвертый элементы совпадения, третий, четвертый и пятый триггеры, блок запрета срабатывания по заднему фронту, блок распределения сигналов, первый и второй управляемые переключатели, блоки фазового компарирования отставания и опережения, блок выработки сигнала окончания подстройки фазы, первая и вторая сборки элемента сигналов, первый и второй счетчики, первый и второй управляемые делители, сумматор и второй фазорасщепитель. причем первый и второй выходы второго фазорасщепителя соединены с первыми входами первого ц второго управляемых делителей, соединенных своими выходами соответственно с первым ц вторым входами сумматора, выход которого соединен со входо.м первого фазорасщепптеля, выходы и второго усилителя-преобразователя соединены соответственно с первыми входаг.-и первого и второго блока совпадений, вторь:; входы которых соединены со вторым выходо;.; блока управления, выход первого блока совпадений соединен с третьим входом-с.:ок распределения сигналов, с входом первого блока запрета, со вторым входом первого элемента совпадениянс третьим входом третьего элемента совпадения, первый вход которого соединен со входом блока запрета срабатывания по заднему фронту, а второй вход соединен с выходом второго блока совпадений, со входом второго блока запрета, с четвертым входом блока распределения сигналов и со вторым входом второго элемента совпадения, третий вход которого соединен с выходом первого блока запрета, с пятым входом блока распределения сигналов и со вторым входом четвертого элемента совпадения, соединенного своим первым входом со входом блока запрета срабатывания по заднему фронту, а своим третьим входом с выходом второго блока запрета, третьим входом первой схемы совпадения и шестым входом блока распределения сигналов, выходы третьего и четвертого элементов совпадения соединены соответственно со входами третьего и четвертого триггеров, выходы которых соединены с седьмым и восьмым входами блока распределения сигналов, первый выход которого соединен с первым входом первого управляемого переключателя и со вторым входом второго yпpaвvlяeмoгo переключателя, а второй выход соединен с первым входом второго управляемого переключателя и со вторым входом первого управляемого переключателя, третьи входы управляемых переключателей соединены с выходом пятого триггера и с первым входом блока выработки сигнала окончания подстройки фазы, выход первого переключающего блока соединен с первыми входами блоков фазового компарирования отставания и опережения, вторые входы которых соединены с выходом схемы запрета срабатывания по заднему фронту и со вторым входом блока выработки сигнала окончания подстройки фазы, третий вход которого соединен с выходом блока фазового компарирования отставания и первым входом первого элемента ИЛИ, а четвертый вход соединен с выходом блока фазового компар):рованяя опережения и с первым входом второй сборки сигналов, выход блока выработки сигнала окончания подстройки фазы соединен со вторыми выходами первой и второй сборки сигналов, выходы которых соединены соответственно со входами первого п второго счетчика, соединенных соответственно своими первыми входами со вторыми входами первого и второго делителя, а вторые входы счетчиков соединены с первым и вторым входами пятого триггера соответственно, при этом первый, второй, третий и четвертый входы блока запрета срабатывания по заднему фронту соединены соответственно с четвертыми входами элементов совпадения.

Источники информации, принятые во

внимание при экспертизе:

1.Авторское свидетельство

СССР № 331333, кл. G 01 R 25/00, 1969.

2.Патент США N° 3737771, кл. 324-183 А, 1973. iflrt ij опорное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Преобразователь угол-код | 1977 |

|

SU720456A1 |

| Резистивная нагревательная установка | 1984 |

|

SU1248082A1 |

| Устройство для приема дискретных сигналов | 1990 |

|

SU1823146A1 |

| Усилительное устройство | 1985 |

|

SU1354391A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Фотоэлектрический преобразователь угол-код | 1984 |

|

SU1197081A1 |

| КОМПЛЕКСНЫЙ ИЗМЕРИТЕЛЬ ДАЛЬНОСТИ | 1992 |

|

RU2018861C1 |

| Устройство для передачи сигнала с частотной манипуляцией | 1985 |

|

SU1256235A1 |

| Устройство двухступенчатого автоматического фазирования факсимильного аппарата | 1984 |

|

SU1238265A2 |

Авторы

Даты

1979-06-30—Публикация

1976-11-16—Подача