Изобретение относится к вычислительной технике и может бЕГгь использовано в ЦВМ.

Известно устройство, осуществля- 5 ющее асинхронную связь между более медленной оперативной памятью и более быстродействующим процессором 1 .

Недостатком данного устройства 10 является то, что после обращения процесса к оперативной памяти его . действие блокируется на время,равное времени выборки данных из памяти, т.е. одновременная параллельная 5 работа Оперативной памяти и процессора возможна только во второй половине цикла оперативной памяти.

Наиболее близким по технической сущности является микропрогргмкшый 20 процессор, содержащий оперативную память, местную память, схему для выполнения арифметических операций, аппаратуру для формирования адресов, аппаратуру для обмена данными и блок 25 микропрограммного управления. В данном процессоре для увеличения быстродействия также организована асинхронная работа оперативной памяти и процессора 2,Недостатком данного процессора, является также блокирование его работы на время, равное времени выборки данных из. памяти.

Цель изобретения - увеличение быстродействия процессора.

Эта цель достигается тем, что в процессор, содержащий буферную память, арифметическо-логическое устройст;во, регистр слова па№1яти, регистр данных, ксдаилутатор данных, блок выборки элементов И, элемент задержки, блок памяти, память микропрограмм, дешифратор (микрокоманд, регистр текущего цикла, блок блокировки процессора, восемь элементов И, причем вход-выход арифметическо-логического устройства соединен с выходом-входом буферной памяти,выход дешифратора микрокоманд соединен с первыми входами первого, второго, третьего, четвертого, пятого шестого, седьмого элементов И, первым входом буферной памяти и первым входом арифметическо-логического устройства, первый выход блока памяти соединен с первым входом восьмого элемента И, выход которого подключен к первому входу регистра данных.

выход которого соединен с первым входом блока памяти и первым входом коммутатора данных, выход которого .подключен ко второму входу буферной памяти и второму входу арифметическо-логического устройства, второ выход блока памяти соединен со вторым входом восьмого элемента И и первым входом блока блокировки процсора, выход которого подключен к певому входу дешифратора микрокоманд и первоглу входу регистра текущего цикла, выход которого соединен со входом памяти микропрограмм, выход которой соединен со вторым входом дешифратора микрокоманд и вторым вхдом регистра текущего цикла, первый выход арифметическо-логического устройства соединен со вторым входо первого элемента И, выход которого подключен ко второму аходу регистра данных, выходы пятого, шестого и седьмого элементов И подключены ко входам регистра слова памяти, выход которого соединен со вторым входом блока памяти, выход элемента задержки соединен со входом блока вборки элементов И, выход которого подключен к третьему входу первого элемента И, введены счетчик текущего .адреса, блок проверки логических условий, п счетчиков и п регисров, формирователь сигналов блокировки, при этом первые выходы п счетчиков подключены ко вторым входам соответственно пятого, ш.естого и седьмого элементов И, первые выходы п регистров подключены ко вторым входам соответственно второго, третьего и четвертого элементов И, вторые выходы п счетчиков и п регистров соединены с соответствующими входаг«1И арифметическо-лотического устройства, второй выход которого соединен с первым входом блока проверки логических условий, выход которогоподключен к третьим входс1м пятого, шестого и седьмого элементов И, первый выход арифметическо-логическо.го устройства соединен со входагли -п счетчиков и первыми входами п регистров, выходы второго, третьего и четвертого элементов И подключены ко входам счетчика текущего адреса, выход которог подключен ко второму входу блока проверки логических условий, входу элемента задержки, второму входу коммутатора данных и вторым входам п регистров, причем выход регистра текущего цикла подключен ко входу формирователя сигналов.блокировки, выход которого соединен со вторым входом блока блокировки процессора.

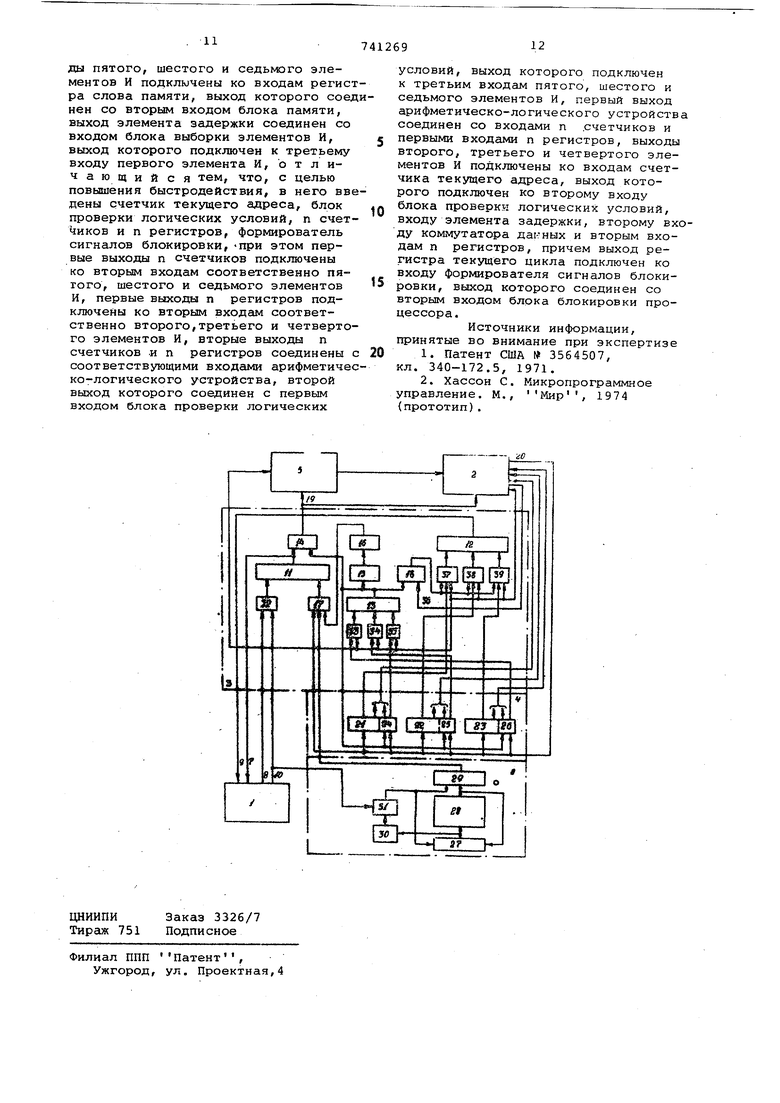

На чертеже приведена схема микроnporpatviMHoro процессора.

Схема микропрограммного процессора состоит из блока 1 памяти, арифметико-логического устройства 2,

блока 3 обмена данными, адресного блока 4, буферной памяти данных 5 и блока 6 микропрограммного управления. Оперативная память 1 связана с блоком 3 обмена данными входными информационными шинами 7, выходными информационными шинами 8, шинами 9 управляющего слова памяти и шинами

10контроля состояния памяти, а

с блоком 6 микропрограммного управления шинами 10 контроля состояния памяти . Блок 3 обмена, данными содержит регистр 11 данных, регистр 12 слова памяти, счетчик 13 текущего адреса, связанный с коммутатором 14 данных и через элемент 15 задержки и блок выборки элементов 16 И с Входными элементами 17 И регистра

11данных, а также содержит блок 18 определения момента обращения к оперативной памяти (блок проверки логических условий), связанный по входу 36 .с арифметико-логическим устройством 2 и счетчиком 13 текущего адреса, а по выходу с входными элементами И .регистра 12 слова памяти. Блок 3 обмена данными связан с арифметико-логическим устройством 2 и буферной памятью данных 5 выходHfcJMH.информационными-ашнами 19 и входными информационными шинами 20, Адресный блок 4 содержит счетчик

21 адреса команды и счетчики 22 и 23 адресов операндов (п сч-етчиков) , связанные по выходу с арифметикологическим устройством 2, а также содержит регистры 24, 25 и 26, номера байта (п регистров), относящиеся соответственно к адресу команды и адресам операндов..Буферная память д-анных 5 связана с арифметико-логическим устройством 2 входными и вЕлходными информационными шинами. Блок 6 микропрограммного упраления содержит .стр 27 текущего цикла, память микропрограмм 28, дешифратор 29 микрокоманд, формирователь 30 сигналов блокировки и блок 31 блокировки пpoцeccopa -элементы 32, 33, 34, 35, 17, 37, 38, 39 И.

Микропрограммный процессор предназначен для выполнения арифметических и логических операций над данными, расположенными в виде пбле постоянной или переменной длины в --теративной памя.ти 1. Обычный процесс выполнения-операции в микропрограммном процессоре включает выборку из оперативной памяти данных по адресу одного или по адресам двух операндов, выполнение нужной операции в арифметико-логическом устройстве и размещение -результата в оперативной памяти по адресу одного из операндов, наименьшей адресуемой единидей данных является байт. Предусмотренный набор операци выполняется арифметико-логическим устройством 2, причем обработка

полей происходит побайтно, а их длина определяется командой. За один цикл процессора может выполняться рдна операция обработки данных, имеЬщих длину 1 байт.

Цикл оперативной памяти можно условно разделить на четыре равные части, отличающиеся между собой процессами, которые происходят в памяти т.е. на части, соответствующие различным состояниям памяти. В состоянии О в оперативной памяти принимается управляющее слово, определяющее адрес данных и характер операции. В состоянии 1 работа памяти определяется операцией: в операции чтения происходит выборка данных, в операции записи прием данных, подлежащих хранению в памяти. Состояния 2 и 3 определяют регенерацию считанной информации или запись информации, принятой в состоянии 1. Таким образом, данные для записи должны быть подготовлены процессором до того, как память достигнет состояния 1, а в операции чтения . данные могут быть использованы процессором не ранее, чем память достигнет состояния 2, т.е. по истечении времени выборки Tg. Длительность цикла оперативной памяти в предлагаемом микропрограммном процессоре составляет 2,5 мкс, длительность цикла процессора 0,625 мкс, т.е. одну четвертую часть цикла оперативной памяти.

В микропрограммном процессоре предусмотрена аппаратура, позволяющая частично или полностью совместит циклы обработки данных процессором с циклами оперативной памяти, что приводит к увеличению быстродействия процессора. Совмещение достигается за счет того, что в процессоре организуется выборка и размещение данных в памяти группами при байтовой обработке, что позволяет при обработке данных текущей выборки заранее организовать обращение к оперативной памяти с целью чтения или записи данных,которые потребуются по окончании обработки данных текущей выборки. Обмен между оперативной памятью и остальной частью микропрограммного процессора происходит 8-байтовыми словами.

Основной для организации такого обмена является разделение текущего адреса байта данных или текущего адреса команды на две части: физический адрес слова памяти и номер байта в слове памяти, причем физическим адресом слова являются старшие разряды адреса байта, а номерами байта в слове - млгшшие разряды ешреса байта. Физический- адрес слова и номер байта в процессе обработки могут изменяться независимо друг От друга.

Обмен данными с оперативной памятью и обработка происходят в предлагаемом микропрограммном процессоре следующим образом. При необходи1 «)сти чтения или записи данных в регистре 12 слова формирует-ся управляющее слово, содержащее физический адрес 8-байтового слова памяти,запрос обращения к оперативной памяти,

o код операции памяти и другие данные, и передаются в блок 1 памяти через шины 9 управляющего слова. В операции чтения по окончании времени выборки Тд, что соответствует состоя5нию памяти 2, сигналы контроля состояния памяти 10 разрешают запись 8-байтового слова с информационных шин 8 памяти в регистр 11 данных через элементы 32 И. Если в управляющем

0 слове указана операция записи, то после приема управляющего слова,что соответствует состоянию памяти 1, оперативная память принимает через входные информационные шины 7-8-гбай5товое слово, сформированное заранее в регистре 11 данных.

Текущие адреса команды и операндов хранятся в адресном блоке 4 таким образом, что физический адрес

0 слова памяти, которому принадлежат байты Команды или операндов, содержится Е счетчиках 21, 22, 23 соответственно, а номера байтов - в регистрах 24, 25 и 26. Если в регистр 11 данных выбрано слово, соот5ветствующее физическому адресу в счетчиках 21, 22 или 23, значение номера байта переписывается под управлением микрокоманд из регистра 24, 25 или 26 через элементы 33, 34

0 или 35 И в счетчик 13 текущего адреса; нужный байт появляется на выходе коммутатора 14 данных и может быть использован арифметико-логическим устройством 2.Последовательное изме5нение физического адреса осуществляется под управлением микрокоманд непосредственно в счетчиках 21 и 22 или 23, а переход к непоследовательно расположенным словам осуществляется

0 путем измерения адресов в арифметикологическом устройстве 2, для чего выходы счетчиков 21, 22, 23 и регистров 24, 25 и 26 соединены со входами арифметико-логического устрой5ства 2. а выходы счетчиков с выходными шинами 20 арифметико-логического устройства 2.

Текущая адресация данных внутри слова осуществляется е помощью счетчика 13 текущего адреса, содержимое

0 которого может последовательно изменяться под управлением микрокоманд в сторону увеличения или уменьшения. После выборки нужного количества байтов данных текущее значение счет5чика 13 может быть возвращено под -управлением микрокоманд в регистр 24, 25 или 26 номера байта При обработке после одного из операндов обычно размещается частич но ига частично или полностью в буферной памяти данных 5. При этом осуществляется требуемое количество обращений к оперативной памяти и последовательная пересьллка байтов данных через шины 19 с кому1утатора 14 данных в буферную 5, Таким образом создается достаточный запас данных для обработки без обращений к оперативной памяти по адресу этого операнда. Далее таким же способом происходит выборка данных из поля, другого операнда в памяти, но данные побайтно пересылаются через шины 19 на вход арифметико-логического устройства 2. Одновременно происходи побайтная выборка другого операнда из буферной памяти 5 и формирование байта результата. Результат как правило должен быть размещен в оперативной памяти. Накопление результат происходит в регистре 11 данныхна месте использованных байтов исходных данных под управлением счетчика13 текущего адреса следующим образом. Значение счетчика 13, в соответстви с которым сформирован выход коммута тора 14 данных, поступает черезэлеменТ 15 задержки на блок 16 выборки элементов И. Элемент 15 задержки обеспечивает запаздывание счетчика 13 текущего адреса на один цикл процессора. Таким образом,когд новым значением счетчика 13 выбирается очередной байт исходных данньч.х на блоке 16 выборки элементов И име ется предьщущее значение номера бай а на выходных шинах арифметико-логи ческого устройства 2 имеется резуль тат обработки предыдущего байта. Этот результат и записывается под управлением микрокоманд в регистр 11 данных через элементы 17 И на место, определяемое блоком 18 выборки элементов И, который дешифрует задержанное значение номера байта. Текущее значение номера байта в счетчике 13 используется также для определения момента формировани управляющего слова памяти, что озна чает и момент обращения к памяти,та как управляющее слово содерлсит запрос; на выполнение операции памяти Еслипри обработке поля данных спра ва нгшево текущее значение номера байта в счетчике 13 НБ О или при обработке поля данных слева направо НБ 1, происходит обработка по леднего байта в слове, и для продол жения операции без приостанова в сл дующем цикле процессора необходимо, ч:тобы в регистр 11 данных были приняты новые данные, или чтобы регистр 11 данных к началу следующего цикла был освобожден от результата. Для этого необходимо сформировать запрос обращения к оперативной памяти раньше, чем процессор закончит обработку последнего байта в слове. Если поле данных заканчивается в пределах данного слова памяти, то нозое обращение для выборки данных не требуется, т,е, момент формирования запроса на выполнение .операции памяти зависит и от текущей длины обрабатываеглого поля. Формирование управляющего слова определяется схемой 18 определения момента обращения к оперативной памяти,формирующей управлянлдиё сигналы как функции текущего значения номера байта НБ и текущего значения длины поля Л, Текущее значение длины поля, указывающее в каждый момент времени количество байтов данных,,подлежащих обработке в данной операции, формируется в процессе обработки в арифметико-логическом устройстве 2 и передается в схему 18 определения .момента обращения к оперативной памяти через шины 36 текущей длины поля. Схема 18 можетпроверять несколько различных соотношений номера байта и длины в зависимости от выполняемой операции. Например, при обработке байтов поля слева направо может щэрверяться соотношение типа (НВ 5). () + (НБ 6).- () + f (НБ 7), где знак + указывает логическое сложение. Если схема 18 сформировала управляющий сигнал, то в регистра 12 слова памяти формируется требуемое управляющее слово, причем физический адрес очередного слова памяти записывается лод управлением микрокоманд через элементы 37, 38 или 39 и из нужного счетчика (21, 22 или 23).После этого операция памяти считается инициированной, а содержимое счетчиков 21, 22 или 23 может- изменяться процессором с целью подготовки следующего обращения, Из приведенного соотношения между номером байта и текущей длиной поля видно, что заярос на йыполнение .. операции памяти в этом случае может формироваться во .время обработки процессором байта 5, байта 6 или байта 7 текущего слова данных. Если запрос на выполнение операции памяти формируется во время обработки байта 5, то лервая половина цикла памяти (Tg) используется процессором для обработки байтов 6 и 7, а после выборки и приема в регистр 11 данных нового слова памяти при состоянии памяти 2 начинается обработка байта О следуютдего слова без приостановки действия процессора, В этом случае

процессор работает одновременно и параллельно с блоком памяти в тече ие всего цикла -памяти, т.е. осуществляется полное перекрытие цикла оперативной памяти циклами процессора. Обращение к блоку памяти во время обработки процессором байта 6 или байта 7 возможно тогда, когда обработка заданного поля начинается с этих байтов. Однако в этих случаях возможно только частичное перекрытие цикла памяти циклами процессора так как процессор не имеет запаса текущих данных на два цикла процессора, соответствующих времени выборки оперативной памяти (Tg), и его действие должно блокироваться до получения нового слова данных из памяти, т.е. до достижения памятью состояния 2.

Блокирование действия процессора производится в блоке б микропрограммного управления.

Блок 6 микропрограммного управления содержит постоянную память 28 дл хранения микропрограмм, согласно которым выполняются операции процессора. Номер Текущего цикла процессор хранится в регистре 27 текущего цикла и представляет собой одновременно и адрес постоянной памяти 28, по которому находится слово микрокоманды данного цикла. Извлеченное из .памяти 28 слово дешифруется на дешифраторах 29 микрокоманд, на выходах которых формируются сигналгл управления вентилями микроопераций. Схема 30 определения ж мeнтa блокировки формирует сигнал при появлении в регистре текущего цикла процессора 27 номеров таких циклов, в которых требуется результат очередной операции оперативной памяти. Блок 31 блокировки процессора при наличии сигнала с Формирователя 30 анализирует состояние оперативной памяти по сигналам, поступающим по шинам 10 контроля состояния памяти . Если память находится в состоянии 2, которое означает, что в оперативной памяти завершается запись предьадущего 8-байтового слова результата, либо вьгерано новое 8-байтовое слово ДАННЫХ, действие процессора не блокируется, т.е. микропрограшла процессора продолжается без задержки Если память не достигла состояния 2, схема блокирования вырабатьшает сигналы, блокирующие выход микрокоманд и изменение номера цикла. Таким образом, процессор оказывается в состоянии ожидания до тех пор, пока устанавливается состояние 2 оперативной памяти.

Изобретение применимо в вычислительных машинах, имеющих быстродействующие арифметико-логические устройства и оперативную память низкого быстродействия.

В предлагаемом микропрограммном процессоре при его реализации может модифицироваться величина порции данных для обмена с оперативной памятью и соотношение между длительностью цикла оперативной памяти длительного процессора, что приведет к изменению разрядности счетчика 13 и регистров 24, 25, 26, к изменению разрядности регистра 11 данных,блока 16 выборки, а также к выбору другого объема буферной памяти данных 5.

Уменьшение времени выполнения операций находится в пределах от 1,6 до 2 раз для различных операций.

20

Формула изобретения

Микропрограммный процессор, содержащий буферную память, арифметико5логическое устройство, регистр слова памяти, регистр данных, коммутатор данных, блок выборки элементов И, элемент задержки, блок памяти, память микропрограмм, де0шифратор микрокоманд, регистр текущего цикла, блок блокировки процессора, BocisMb элементов И, причем вход-выход арифметическо-логического устройства соединен с выходом-входом буферной памяти, выход дешифратора

5 микрокоманд соединен с первыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого элементов И, первым входом буферной памяти и первым входом арифмети0ческо-логического устройства,первый выход блока памяти соединен с первым входом восьмого элемента И, выход которого подключен к первому входу регистра данных, выход которого

5 соединен с первым входом блока памяти и первым входом коммутатора данных, которого подключен ко второму входу буферной памяти и второму входу арифметическо-логического уст0ройства, второй выход блока памяти соединен со вторым входом восьмого элемента И и первым входом блока блокировки процессора, выход которого подключен к первому входу дешиф5ратора микрокоманд и первому входу регистра текущего цикла, выход которого соединен со входом памяти микропрограмм, выход которой соединен со вторьвл входом дешифратора

0 микрокоманд и вторым входом регистра т:екущего цикла, первый выход арифметическо-логического устройства соединен со вторым входом первого элемента И, выход которого подключен ко

5 второму входу регистра данных, выхо-(

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

Авторы

Даты

1980-06-15—Публикация

1978-01-04—Подача