(54) УСТРОЙСТВО ДЛЯ КС«ТРОЛЯ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО ПОИСКА И ЗАМЕНЫ ВХОЖДЕНИЙ В ОБРАБАТЫВАЕМЫХ СЛОВАХ | 2005 |

|

RU2296366C1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ПОИСКА ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ | 2001 |

|

RU2220448C2 |

| Запоминающее устройство с обнаружением отказов | 1981 |

|

SU1005192A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

..

Изобретение относится к аапомина.щим устройствам.

Известно уст юйство для контроля памяти 11 , содержащее блок фондирования адресов, блок срйзнения, блок регистрации И блоки памяти.

Недостатком этого устройства являются большие аппаратурные затраты.

Из известных устройств наиболее близким тезцшческим решением к изобретению является устройс-то для контроля памяти, содержащее логический блок, управляющие входы которого подключены к управляющим шинам СйТ.

Недостатком этого устройства является невысокая скорость работы при обнаружении скрытых неисправностей. К типу скрытых неисправностей относятся такие неисправности запоминающих элементов блоков памяти, когда при обращении к запоминающим элементам с них считьдвается информация, не зависящая от записываемой информации (например, всегда I независимо от записи). Такай неисправность запоминающих элементов не нарушает работы блока памяти в том случае, если записываемая информация совпадает со считываемой (например, записывается 1 в запоминающий элемент, с которого считывается во всех случаях ). Скрытая Неис11равность обнаруживается только при изменении записываемой Информации.

Целью изобретения является пош 1шение быстродействия устройства за счет обнаружения скрытых неисправностей без использсвания информации, специально предназначенной для тестовых программ.

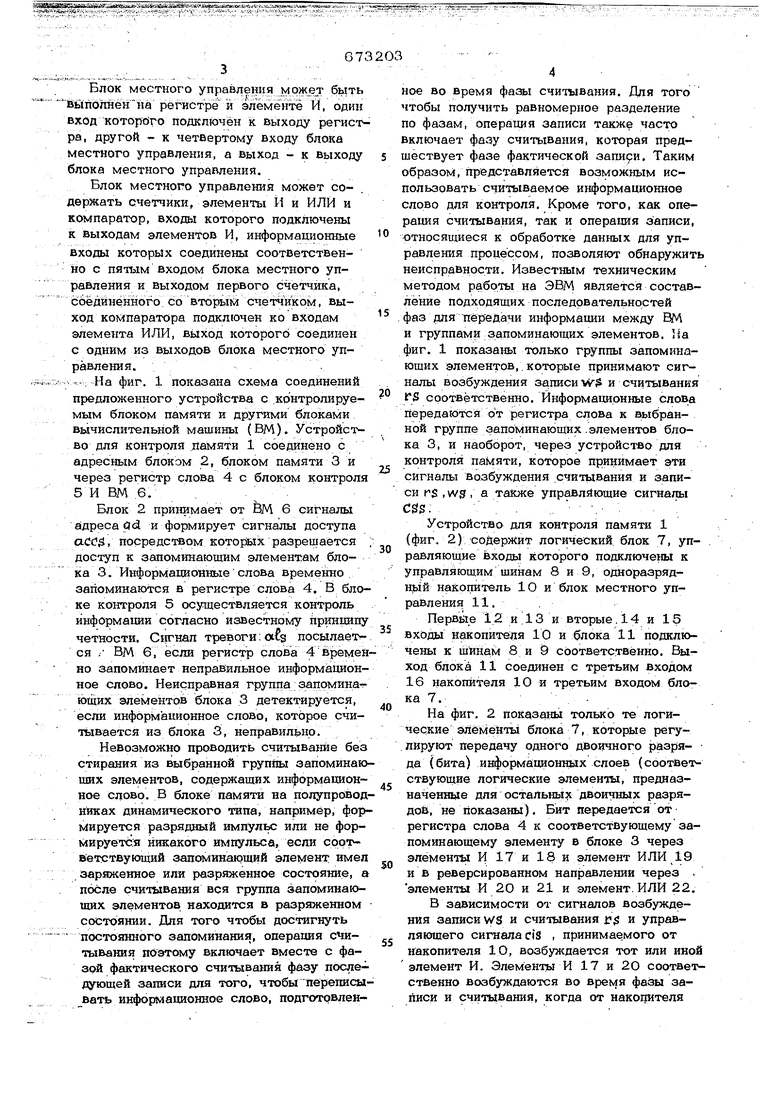

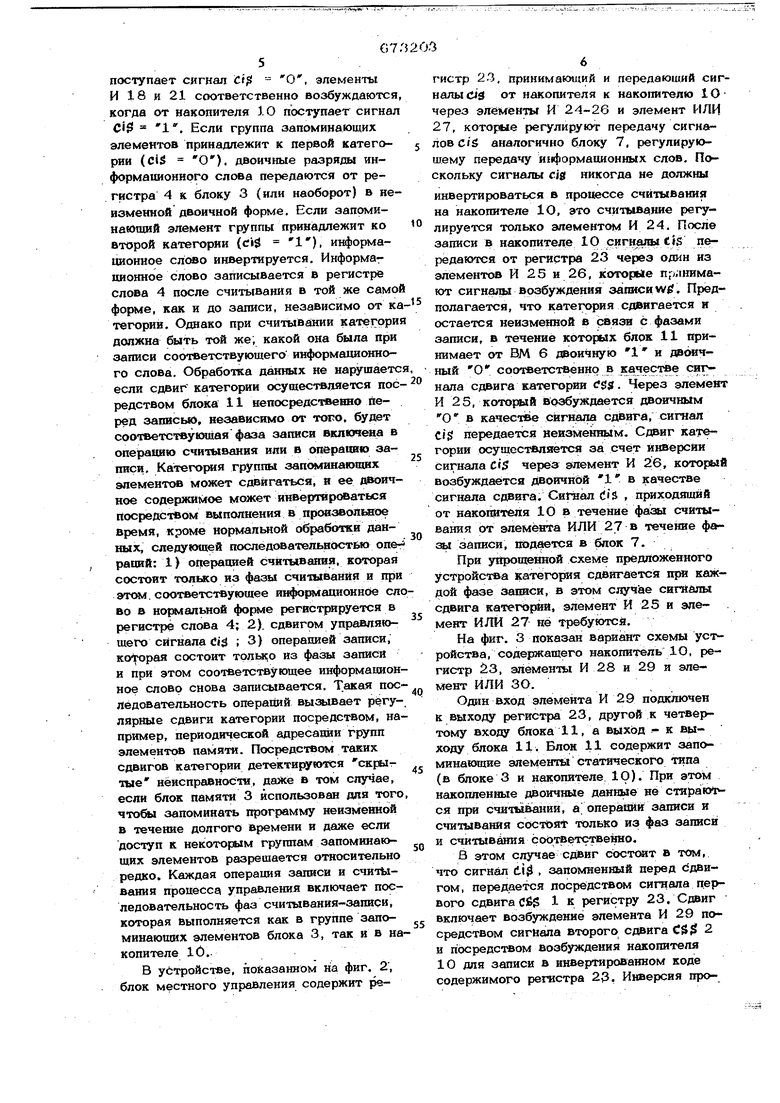

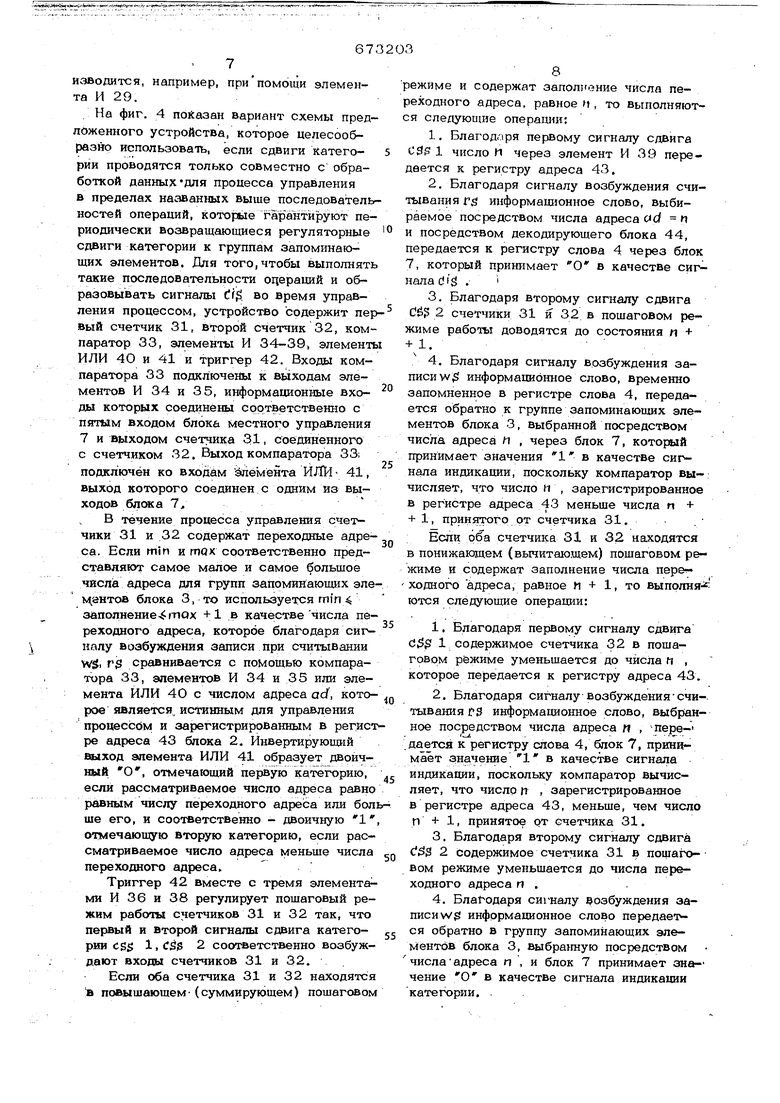

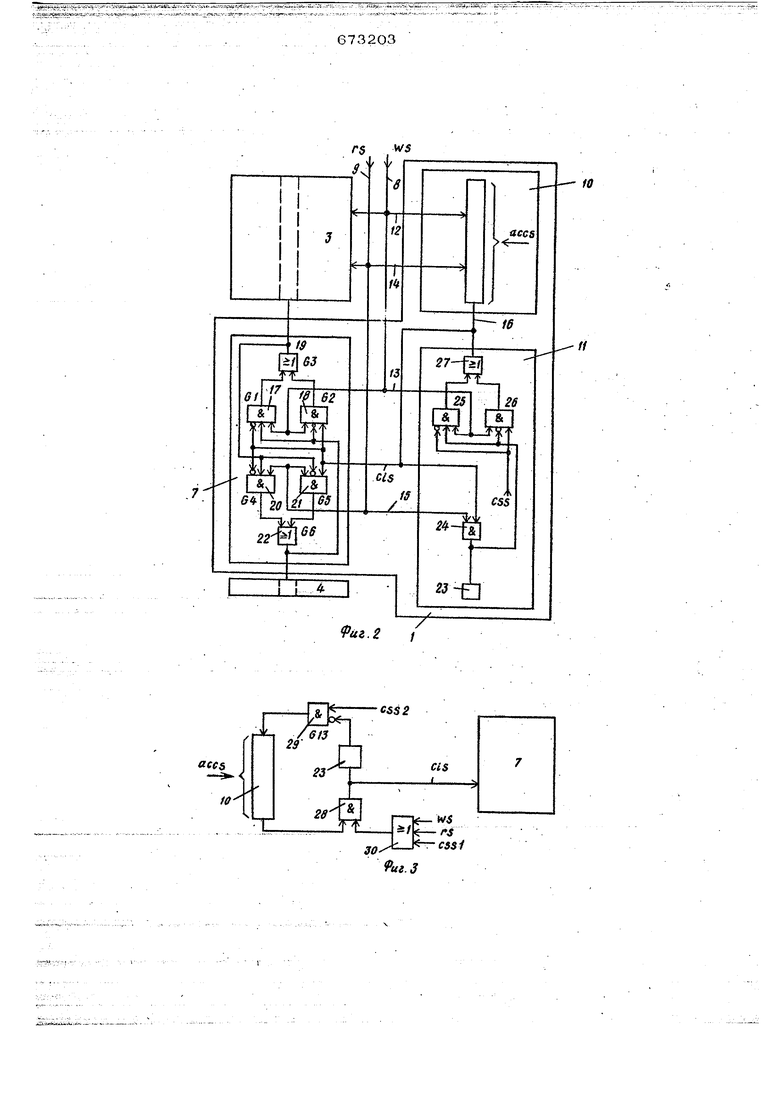

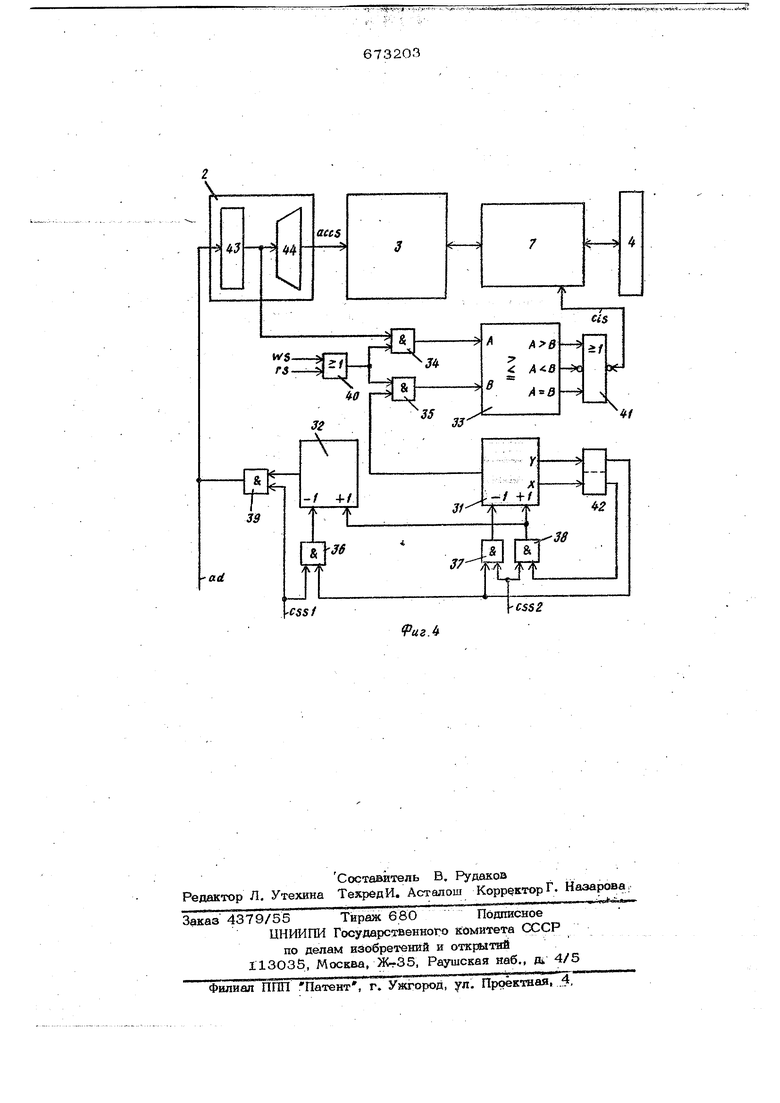

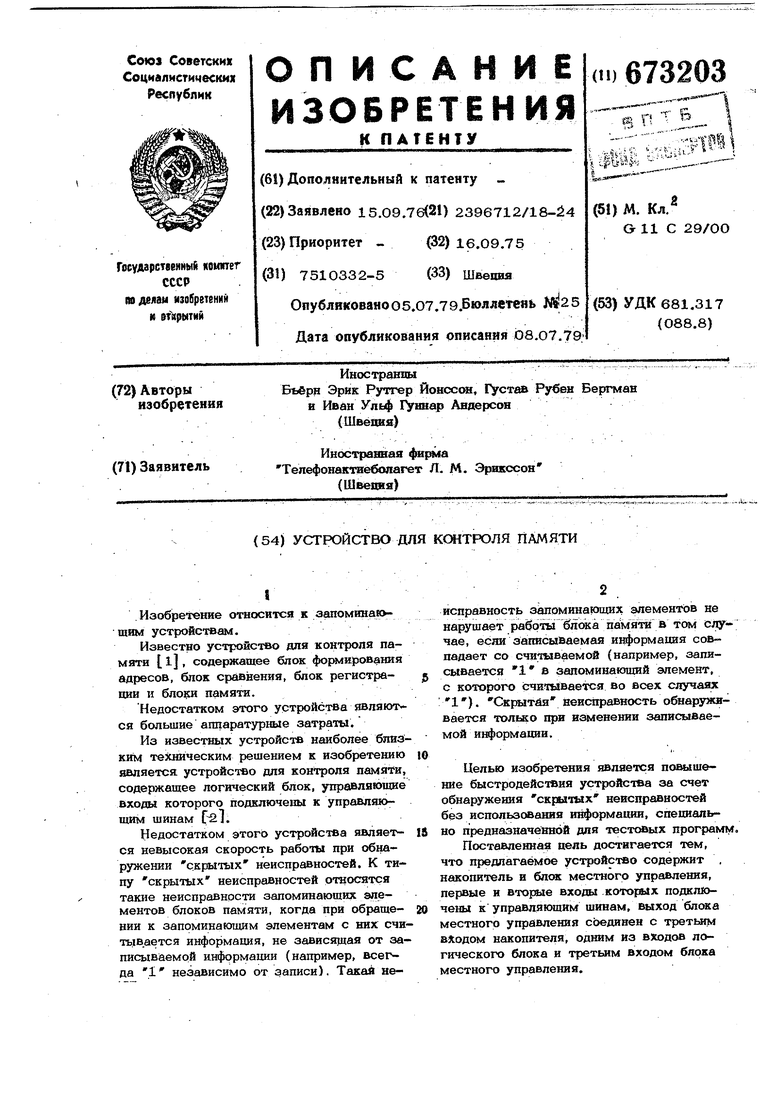

Поставленная цель достигается тем, что предлагаемое устройство содержит . накопитель и блок местного управления, первые И вторые входы которых подключены к управляющим щинам, выход блока местного управления соединен с третьим входом накопителя, одним из входов логического блока И третьим входом блока местного управления. Блок местного управления быть BbinonHeHita регистре и элёмейте И, один вход которого пошслючён к выходу регистра, другой - к четвертому входу блока местного управления, а выход - к выходу блока местного управления. Блок местного управления может содержать счетчики, элементы И и ИЛИ и компаратор, входы которого подключены к выходам элементов И, информационные входы которых соединены соответственно с пятым Входом блока местного управления и выходом первого счетчика, соедйненного. со вторым счетчиком, выход компаратора подключен ко входам элемента ИЛИ, выход которого соединен с одним из выходов блока местного управления. 1-; На фиг. 1 показана схема соединений предложенного устройства с .контролируемым блоком памяти и другими блоками вычислительной машины (ВМ). Устройство для контроля .памяти 1 соединено с адресным блокам 2, блоком памяти 3 и через регистр слова 4 с блоком контроля 5 И ВМ 6.. Блок 2 принимает от ВМ 6 сигналы адреса (3d и формирует сигналы доступа а., посредством которых разреи1ается доступ к запоминающим элементам блока 3. Информационные слова временно запоминаются в регистре слова 4. В блоке контроля 5 осуществляется контроль информации согласно известному принципу четности. тревоги посылает ся ; ВМ 6, если регистр слова 4 Времен но запоминает неправильное информационное слово. Неирправная группа запоминав ющих элементов блока 3 детектируется, если информаиионное слово, которое считывается из блока 3, неправильно. Невозможно проводить считывание без стирания из выбранной группы запоминаю щих элементов, содержащих информационное Слово. В блоке памяти на полупровод никах динамического типа, например, фор мируется разрядный импульс или не формируе тсд никакого импульса, если срр-гветствующий запоминающий элемент имел заряженное или разряженное состояние, а после считывания вся группа запоминающих элементов находится в разряженном состоянии. Для того чтобы достигнуть - постоянного запоминания, операция считывания поэтому включает вместе с фазой фактического считывавши фазу последующей записи для того, чтобы переписы вать информационное слово, подготовленнов во Время фазы считывания. Для того тобы получить равномерное разделение о фазам, опе раютя записи также часто ключает фазу считывания, которая предествует фазе фактической записи. Таким образом, представляетсй возможным использовать считываемое информационное слово для контроля. Кроме того, как операция считывания, так и операция записи, относящиеся к обработке данных для управления процессом, позволяют обнаружить неисправности. Известным техническим методом работы на ЭВМ является составление подходящих последовательностей фаз для пёреДачи информации между ВМ и группами запоминающих элементов, lia фиг. 1 показаны только группы запоминающих элементов,. которые принимают сигналы возбуждения записи W и считывания fS соответственно. Информационные слова передаются от регистра слова к выбранной группе запоминающих .элементов блока 3, и наоборот, через устройство для контроля памяти, которое принимает эТи сигналы возбуждения считывания и записи г$ ,wg, а также управляющие сигналы . . ... Устройство для контроля памяти 1 (фиг. 2) сойержит логический блок 7, уп- . равляющие входь которого подключены к управляющим шинам 8 и 9, одноразрядный накопитель 10 и блок местного управления 11. Первые 12 и 13 и вторые .14 и 15 входы накопителя 10 и блока 11 подключены к шина,м 8 и Э соответственно. Выход блока 11 соединен с третьим входом 16 накопителя 1О и третьим входом блока 7.. На фиг. 2 показаны только те логические элементы блока 7, которые регулируют передачу одного двоичного разряда (бита) информационных слоев (соответствующие логические элементы, предназначенные для остальнь1:х двоичных разрядов, не показаны). Бит передается от регистра слова 4 к соответствующему запоминающему элементу в блоке 3 через элементы И 17 и 18 и э лемент ИЛИ 19 ив реверсированном направлении через . элементы И 20 и 21 и элемент. ИЛИ 22. В зависимости от сигналов возбуждения записи WS и считывания 1С$ и управляющего сигнала cis , принимаемого от накопителя 10, возбунсдается тот или иной элемент И. Элементы И 17 и 20 соответственно возбуждаются во врек1я фазы записи и считывания, когда от накопителя поступает сигнал ci - О, элементы И 18 и 21 соответственно возбуждаются когда от накопителя 10 поступает сигнал Ci 1, Если группа запоминающих элементов принадлежит к первой категории (ciS О), двоичные рааряды информационного слова передаются от регистра 4 к блоку 3 (или наоборот) в не изменной двоичной форме. Если запоминающий элемент группы принадлежит ко Второй категории {ci$ ), информационное слово инвертируется, Информаг оионное слово записывается в регистре слова 4 после считывания в той же само форме, как и до записи, независимо от к тегории. Однако при считывании категори должна быть той же, какой она была при записи соответствующего информаиистного слова. Обработка данных не нарушаетс если сдвиг категории осуществляется пос редством блока 11 непосредственно перед записью, независимо от того, будет соответствуюшаяфаза записи включена в операцию считывания или в операцию записи. Категория группы зап «шающих элементов может сдвигаться, я ее двоичное содержимое может инвертироваться посредством выполнения в прои опьное Время, кроме нормальной обработки данных, следующей послед лател1лостью операций: 1) операцией счйтыва гая, которая состоит только из фазы считывания и при этом, соответствующее информационное сл во в нормальной фо(ме регистрируется в регистре слова 4; 2). сдвигом управляющего сигнала ci ; 3) операцией записи, состоит трлысо из фазы записи и при этом соответствующее информационное слово снова записывается. Такая последовательность операций выадвает регулярные сдвиги категории посредством, например, периодической адресации групп элементов памяти. Посредством таких сдвигов категории детектируются скры тые неисправности, даже в том случае, если блок памяти 3 использован для того чтобы запоминать программу неизменной в течение долгого времени и даже если доступ к некоторым группам запоминающих элементов разрещается относительно редко. Каждая операция записи и считывания процесса управления включает последовательность фаз считывания-записи, которая Выполняется как в группе запоминающих элементов блока 3, так и в накопителе 10.. В устройстве, показанном на фиг. 2, блок местного управления содержит регистр 2.3, принимающий и передающий снгналы д от накопителя к накопителю Ю через элементы И 24-26 и элемент ИЛИ 27, которые регулируют передачу сигналовС/S аналогично блоку 7, регулирующему передачу И |формаш{онных слов. Поскольку сигналы cjg никогда не должны инвертироваться в npoitecce считывания на накопителе 1О, это считывание регулируется тольжо элементом И 24. После записи в накопителе 10 сигналы t is передаются от регистра 23 через один из элементов И 25 и 26, которые пр.шимают сигнашл возбуждения записи w. Предполагается, что категория сдвигается и остается неизменной в связи с фазами записи, в течение которых блок 11 принимает от ВМ 6 двоичную 1 и двоичный О соответственно в качестве сигнала сдвига категории $$. Через элемент И 25, который возбуждается двоичным О в качестве сигнала сд1вига, сигнал С1$ передается Неизменным. Сдвиг категорни осуществляется за счёт инверсии сигнала dS через элемент И 26, который Возбуждается двоичной 1 в качестве сигнала сдвига. СиГзагал й , приходящий от накопителя 1О в течение фазы считывания от элемента ИЛИ 27 в течение фазы записи, подается в блок 7. При уйрощенной схеме предложенного устройства категория сдвйгаетс:я щмя каждой фазе записи, в этом случае сигналы сдвига категории, элемент И 25 и элемент ИЛИ 27 не требуются. На фиг. 3 показан вариант схемы устройства, содержащего накопитель 1О, регистр ИЗ, элементы И 28 и 29 и элемент ИЛИ ЗО. Один вход элемента И 29 подключен к выходу регистра 23, другой к четвертому входу блока 11, а выход - к выходу блока 11, Блок 11 содержит запоминающие элементы статического типа (в блоке 3 и накопителе 10). При этом накопленные двоичные данные не стираю ся при считывании, аопераций записи и считывания состоят- только из фаз записи и считывйния соответственно. В этом случае сдвиг состсдат в том, то сигнал di , запомненный церед с5дВигом, передает-ся посредством сигнала перого сдвига CUS 1 к регистру 23. Сдвиг ключает возбуждение элемента И 29 поредством сигнала второго сдаига С& 2 посредством возбуждения накопителя 10 для записи в инвертированном коде одержимого регистра 23, Инверсия про7ИЗВОДИТСЯ, например, при помощи элемента И 29. На фиг, 4 показан вариант схемы предложенного устройства, которое целесообразно использовать, если сдвиги категории проводятся только совместно с обработкой данны с для процесса управления в пределах названных выше последовательностей операций, которые гар) периодически Возвращающиеся регуляторные сдвиги категории к группам запоминающих элементов. Для того, чтобы выполнять такие последовательности оцераций и образовывать сигналы tf$. во Время управления процессом, устройство содержит пер вый счетчик 31, второй счетчик 32, компаратор 33, элементы И 34-39, элементы ИЛИ 40 и 41 и триггер 42. Входы компаратора 33 подключены к выходам элементов И 34 и 35, информационные входы которых соединены соответственно с пятым входом блока местного управления 7 и выходом счетчика 31 соединенного с счетчиком 32. Выход компаратора 33; подключён ко входам Элемента ИЛИ- 41, выход которого соединен с одним из выходов блока 7, В течение процесса управления счетчики 31 и 32 содержат переходные адреса. Если min и mQX соответственно представляют самое малое и самое больщое числа адреса для групп запоминающих эле цантов блока 3, то используется min 4 заполнение mox +1 в качествечисла переходного адреса, которое благодаря сигналу возбуждения записи при считывании rJ3 сравнивается с помощью компаратора 33, элементов И 34 и 35 или элемента ИЛИ 40 с числом адреса ad, которое является истинным для управления процессом и зарегистрированным в регист ре адреса 43 блока 2. Инвертирующий аыход эяемента ИЛИ 41 образует двоичный О, отмечающий первую категорию, если рассматриваемое число адреса равно равным числу переходного адреса или боп ше его, и соответственно двоичную отмечающую вторую категорию, если рассматриваемое число адреса меньше числа переходного адреса. Триггер 42 вместе с тремя элементами И 36 н 38 регулирует пошаговый режим работы счетчиков 31 и 32 так, что первый и Второй сигналы сдвига категории egg 1, 2 соответственно возбуждают входы счетчиков 31 и 32. Если оба счетчика 31 и 32 находятся в повышающем- (суммирующем) пошаговом

8 ежиме и содержат заполнение числа пееходного адреса, равное и , то выполняютя следуюише операции: 1.Благодаря первому сигналу сдвига Сд 1 число И через элемент И 39 переается к регистру адреса 43. 2.Благодаря сигналу возбуждения счиывания Гй информационное слово, выбиаемое посредством числа адреса и посредством декодирующего блока 44, ередается к регистру слова 4 через блок , который принимает О в качестве сигала d Ig . i 3.Благодаря второму сигналу сдвига de 2 счетчики 31 if 32 в пошаговом реиме работы доводятся до состояния п + 4.Благодаря сигналу возбуждения записи w информационное слово, временно запомненное в регистре слова 4, передается обратно к группе запоминающих элементов блока 3, выбранной посредством числа адреса п , через блок 7, который принимает значения 1 в качестве сигнала индикации, поскольку компаратор вычисляет, что число (1 , зарегистрированное в регистре адреса 43 меньше числа п + + 1, приняпгогр от счетчика 31. Если оба счетчика 31 и 32 находятся в понижающем (вычитающем) пошаговом режиме и содержат заполнение числа пере ходного адреса, равное и + 1, то выполняются следующие операции: 1.Благодаря первому сигналу сдвига С$ 1 содержимое счетчика 32 в пощаговом режиме уменьшается до числа п , которое передается к регистру адреса 43. 2.Благодаря сигналу возбуждениясчитывания гз информационное слово, выбранное посредством числа адреса п , пере.дается к регистру слова 4, блок 7, приниMaieT значение 1 в качестве сигнала индикации, поскольку компаратор вычисляет, что число П , зарегистрированное в регистре адреса 43, меньше, чем число п + 1, принятое от счетчика 31. 3.Благодаря второму сигналу сдвига $$ 2 содержимое счетчика 31 в пощагчэвом режиме уменьшается до числа переходного адреса п . 4.Блаьодаря сигналу возбуждения записи w$ информационное слово передае- ся обратно в группу запоминающих элементов блока 3, выбра1шую посредством числа адреса п , и блок 7 принимает значение О в качестве сигнала индикации категории. 9 Формула изобретения 1,Устройство для контроля памяти, содержащее логический блок, управляющи входы которого подключены к управляющ шинам, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит накопитель и блок местного управления, первые и вто{мде входы которых подключены к управляющим шинам, вдцход блока местного управления соединен с третьим входом на1српителя, одним из входов логического блока и третьим входом блока местного управления. 2.Устройство по п, 1, отличающееся тем, что блок местного управления содержит регистр и элемент И, один вход которого подключен к выходу регистра, другой - к четвертому входу блока местного управления, а вы j|±i jL V5

у

3

.«

е- бf

Фиг. f ХОД к выходу блока местного управления. 3. Устройство по п. 1, о т л и ч ю щ е е с я тем, что блок местного управления содержит счетчики, элементы И и ИЛИ и компаратор, входы которого подключены к выходам элементов И, информационные входы которых соединены соответственно с пятым входом блока местного управления и выходом первого счетчика, соединенного со втррым счетчиком, выход компаратора подключен ко входам элемента ИЛИ, выход которого соединен с одним из выходов блока мест ного управления. Источники информации, принятые во внимание при экспертизе 1.AjBTOpCKO свидете льство СССР NO 5О4250, М.Кл 0-11 С 29/00, 1975. 2.Патент Великобритании №1186416, кл. Н 4 К, 1970.

Риъ.2 /

-CSS I

CSS 2

Авторы

Даты

1979-07-05—Публикация

1976-09-15—Подача